Fターム[5J055AX00]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153)

Fターム[5J055AX00]の下位に属するFターム

スイッチの基本性能向上 (933)

性能の向上 (482)

物理量(温度等)変化の補償 (146)

スイッチ状態の表示、マンインターフェイス (2)

スイッチの操作性向上、誤操作の防止 (16)

誤動作防止 (777)

故障対策 (573)

信頼性向上のための変形 (218)

電源電圧変動の対策 (81)

試験、調整 (60)

構造上の改善、配置、配線等 (18)

簡素化、小型化 (492)

特定の規格を考慮しているもの (2)

課題の発生する時、注目している時 (638)

課題の解決手段 (518)

Fターム[5J055AX00]に分類される特許

121 - 140 / 197

高精度プルアップ/プルダウン回路

【課題】高い精度でプルアップ電流とプルダウン電流の電流値を一致させることが可能な高精度プルアップ/プルダウン回路を提供する。

【解決手段】高精度プルアップ/プルダウン回路1は、PチャネルトランジスタTP1,TP2と、NチャネルトランジスタTN1,TN2と、参照電圧源11と、制御回路12とから構成される。制御回路12は、演算増幅回路の構成であり、−入力端子にノードNA,NBの電圧であるVrefが入力され、フィードバック構成によりPチャネルトランジスタTP2とNチャネルトランジスタTN2の接続点(C点)の電圧がVrefと等しくなるように制御される。このとき、電流Ipuoと電流Ipdoの電流値が等しく、電流Ipuoが正確に電流Ipuにミラーされ、且つ電流Ipdoが正確に電流Ipdにミラーされるため、プルアップ電流Ipuとプルダウン電流Ipdの電流値を高精度に一致させることができる。

(もっと読む)

負荷駆動装置

【課題】構成の大型化やコストの上昇を抑制して、PWM制御によりモータ負荷を高精度に駆動制御することを課題とする。

【解決手段】CPU10から与えられるPWM信号に基づいて負荷駆動電圧が負荷駆動回路12からモータ2に供給されてモータ2がPWM制御により駆動され、モータ2に供給されるモータ駆動電圧のパルス信号がパルス検出回路13で検出され、パルス検出回路13で検出されたモータ駆動電圧のパルス信号とCPU10から負荷駆動回路12に与えられるPWM信号とのパルス幅の差分がCPU10で算出され、この差分に基づいてCPU10から負荷駆動回路12に与えられるPWM信号のパルス幅が補正され、補正されてCPU10から負荷駆動回路12に与えられたPWM信号に基づいてモータ2が駆動制御されて構成される。

(もっと読む)

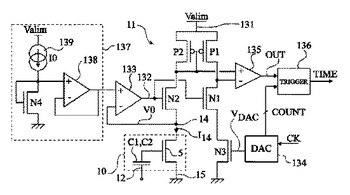

時間測定のための電荷保持要素を読み取る回路

【解決手段】本発明は、その誘電体がリークを示す少なくとも1つの容量性素子(C1,C2) と、残留電荷を読み取るための絶縁された制御ターミナル(5) を含むトランジスタとを備えたタイプの時間測定のための電荷保持電子要素(10)を読み取るための方法及び回路に関し、前記読み取り回路は、第1タイプの少なくとも1つのトランジスタ(P1,P2) と、第2タイプの1つのトランジスタ(N3,5)とを夫々含む、2つの供給ターミナル間の2つの平行な分岐を備えており、前記分岐の一方の第2タイプのトランジスタは、読み取られるべき前記要素のトランジスタから構成されており、前記分岐の他方の第2タイプのトランジスタは、該トランジスタの制御ターミナルでステップ信号(VDAC)を受けており、第1タイプのトランジスタの夫々のドレインは、比較器(135) の夫々の入力に接続されており、比較器の出力(OUT) が、電荷保持要素における残留電圧の表示を与える。  (もっと読む)

(もっと読む)

負荷駆動装置

【課題】ハイサイドトランジスタとローサイドトランジスタを備えた負荷駆動装置においてトランジスタの熱的負荷の低減を図ることができるようにする。

【解決手段】タイマー40により、負荷10の通電期間においてローサイドトランジスタQ2を連続してオンにするとともに負荷10に流れる電流が定電流となるようにハイサイドトランジスタQ1を制御する状態から、ハイサイドトランジスタQ1を連続してオンにするとともに負荷10に流れる電流が定電流となるようにローサイドトランジスタQ2を制御する状態に切り替えられる。

(もっと読む)

遅延時間発生回路

【課題】構成素子の全体を集積回路で実現できる上に、遅延時間の精度を向上でき、しかも集積回路ごとの遅延時間のばらつきを低減できる遅延時間発生回路の提供。

【解決手段】電圧検出回路1は、電源電圧が所定値を上回るときに、その旨を示す検出信号を出力する。カウンタ3は、電圧検出回路1から検出信号が出力されたときに、発振回路3からのクロックの計数動作を開始する。メモリ5には、電圧検出回路1から検出信号があったときを起点とする任意の遅延時間、および発振回路1の発振周波数に基づいて決定される設定値が予め格納されている。コンパレータ7は、カウンタ3の計数値をメモリ5に格納される設定値と比較し、その計数値がその設定値と一致したときに遅延信号を出力する。

(もっと読む)

表示装置とその駆動装置及び駆動方法

【課題】データ駆動部のデジタル−アナログ変換器回路を簡単にしながらも、表示装置のガンマ特性による階調電圧値を正確に反映し、階調電圧の単調増加特性及び正確度を向上させることのできる表示装置とその駆動装置及び駆動方法を提供する。

【解決手段】互いに異なる大きさを有する複数の階調電圧を各々含む複数の階調電圧集合を生成する階調電圧生成部と、画像信号の第1部分に基づいて前記複数の階調電圧集合の内から一つの階調電圧集合を選択する第1選択部と、前記画像信号の第2部分に基づいて前記選択された階調電圧集合に属する複数の階調電圧の内から一つ以上の階調電圧を選択する第2選択部とを含む信号変換部とを有する。

(もっと読む)

電力変換器の制御回路

【課題】電力変換装置の大型化やコストアップを招くことなく、サージ電圧と損失のトレードオフ特性の改善を図る。

【解決手段】PWM信号発生部1からの出力を絶縁器4を介して電力半導体素子をオンオフ制御するに当り、ターンオフ指令信号Bの直後に、デッドタイム生成回路2で作成されるデッドタイムよりも短いパルス状の信号Dを、遅延回路5およびワンショット回路7により得て、これをアンド回路8を経てオア回路3においてデッドタイム生成回路2の出力に重畳させることにより、ゲート駆動条件を切り換えてターンオフやターンオン時間を変えられるようにする。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の機能ブロックを起動するときに発生するラッシュカレントを低減する。

【解決手段】電源線と、第1回路ブロックと第2回路ブロックと、それらの回路ブロックと電源線との接続を制御する電源供給制御部とを具備する半導体集積回路を構成する。

電源供給制御部は、電源線と回路ブロックとの間に設けられたスイッチ群と、スイッチ群の動作を制御するスイッチ制御回路とを具備する。ここで、スイッチ群は、第1回路ブロックと電源線との接続を制御する第1スイッチと、第2回路ブロックと電源線との接続を制御する第2スイッチとを含むことが好ましい。

その上で、スイッチ制御回路は、回路ブロック全体の動作開始を指示する動作制御信号と、第1スイッチを介して出力される出力電位に対応して第2スイッチの動作を制御する。

(もっと読む)

高周波スイッチ回路および半導体装置

【課題】高調波歪やFETの挿入損失を抑制しつつ、入力電力を無理なく増加させることが可能な高性能の高周波スイッチ回路を提供する。

【解決手段】入出力端子と接地端子との間、あるいは、入出力端子間に、多段接続されたFETによって構成された基本スイッチ部(スイッチ回路)を設けると共に、1つの基本スイッチ部に含まれる複数のFETのうち、基本スイッチ部がオフ状態であるときに信号電力が印加される入出力端子側のFETのゲート幅を、その入出力端子から、より遠い位置にある残余のFETのゲート幅よりも大きく設定する。

(もっと読む)

高周波スイッチモジュール

【課題】 省電力で高調波発生量の少ない、小型の高周波スイッチモジュールを提供する。【解決手段】 第1通信システムの送受信信号の伝送経路を切り替える電界効果トランジスタを用いたスイッチ回路と、複数のフィルタ回路を備え、少なくとも3つのポートを備えるSPnTの高周波スイッチであり、その第1のポートに接続する第1のフィルタ回路と、第2のポートに接続する第2のフィルタ回路を有し、第2のフィルタ回路が、ローパスフィルタ又はバンドパスフィルタであり、第1のフィルタ回路が、ノッチフィルタ又はローパスフィルタであって、第1及び第2のフィルタ回路はインダクタとコンデンサで構成し、各回路において、インダクタとコンデンサの少なくとも一部を多層基板内に電極パターンで形成して高周波スイッチを実装し、第1及び第2のフィルタ回路のインダクタ用電極パターンとが、積層方向に重なり合わない。 (もっと読む)

化合物半導体スイッチ回路装置

【課題】スイッチMMICにおいて、ソース電極およびドレイン電極が近接して配置される箇所では、高周波信号の漏れが発生し、歪特性が悪い問題があった。

【解決手段】ゲート配線電極を梯子状のパターンとし、スイッチMMICの全てのソース電極−ドレイン電極間に、ゲート配線電極を配置する。また、ゲート配線電極と、ソース電極またはドレイン電極の交差部において、これらの間に比誘電率の大きい窒化膜と、比誘電率の小さいポリイミド、あるいは中空部を配置する。梯子状ゲート電極と容量低減策により2次高調波レベルを低減できる。またドレイン電極−ソース電極間の高周波信号の漏れを防止できるので3次高調波レベルを低減でき、スイッチMMICの歪特性を大幅に向上できる。

(もっと読む)

ゲート駆動装置

【課題】従来発生していたdv/dt貫通電流および過電流による電力損失を抑止することができるゲート駆動装置を提供する。

【解決手段】第1パワーMOSトランジスタ1を遮断する遮断回路24において、ゲート電荷を放電する電流が異なる2つの遮断回路を備え、第1パワーMOSトランジスタ1が遮断状態で第2パワーMOSトランジスタ2が遮断から導通状態となると同時に、第1パワーMOSトランジスタ1を、ゲート電荷を放電する電流が大きい遮断回路により完全に遮断する。

(もっと読む)

インターバルタイマ装置および半導体集積回路

【課題】カウントクロックの分周比が切り替えられた場合にも、インターバルタイマ装置のイベント信号の周期が変動せず、常に一定の時間間隔でイベント信号を生成できるようにする。

【解決手段】分周回路110によって、入力されたクロックを分周してカウントクロックを生成する。加算器102、初期値レジスタ103、カウンタ値セレクタ104、およびカウンタ105によってアップカウンタを構成し、カウントクロックに同期して、所定の計数値単位で、カウント値を更新する。この際、計数値は、分周回路110における分周比に応じ、計数値セレクタ101で所定の値を選択する。そして、前記カウント値が所定の比較値に達した場合に、比較器107からイベント信号を出力する。

(もっと読む)

出力回路

【課題】プッシュプル出力回路の出力電圧の発振を防止すること。

【解決手段】ソース側出力トランジスタQ1、シンク側出力トランジスタQ2、これらのトランジスタQ1,Q2のベース端子同士を接続するダイオードD1,D2、及びシンク側出力トランジスタQ2のベース端子に、コレクタ端子を接続して、ソース側及びシンク側出力トランジスタQ1,Q2のベース電流を制御する電流制御トランジスタQ3を備える出力回路において、電流制御トランジスタQ3のコレクタ端子とベース端子とを容量性素子6を介して接続した。これにより、出力電圧を発振させるノイズによって、トランジスタQ1,Q2,及びダイオードD1,D2からなるループ経路内の電位が変動したとき、その電位変動が電流制御トランジスタQ3のベース端子に伝達され、電流制御トランジスタQ3は電位変動を打ち消すコレクタ電流を流すことができる。

(もっと読む)

モータドライブ・電流検知回路

【課題】ローサイド(low side)シャント抵抗を使用してモータ電流を検知すること。

【解決手段】負荷に接続したパワートランジスタ(Q1、Q2)と、そのパワートランジスタにゲートドライブ信号を供給するゲートドライブ部(20、22)と、負荷を流れる電流に比例する信号を出力する電流検知デバイス(Ru)と、ゲートドライブ部によって制御されるサンプルホールド回路(28)とを備え、負荷をドライブし、負荷電流を検知する。

(もっと読む)

化合物半導体スイッチ回路装置

【課題】受信側FFTと送信側FETを固定して用いるスイッチMMICでは、それぞれのFETのピンチオフ電圧を異ならせ、送信側および受信側のスイッチング素子として適切な特性に設計すればよい。しかし、HEMTにおいてリセスエッチングの深さ制御が困難であり、ピンチオフ電圧の再現性が悪い問題があった。

【解決手段】エッチングストップ用のInGaP層を2層有する基板を使用する。InGaP層とAlGaAs層の選択エッチングを使用することにより、再現性良く2種類のピンチオフ電圧を実現できる。また2種類のHEMTのゲート電極に埋め込みゲート電極構造を採用するが、PtがInGaP層に拡散しないようにコントロールすることで、耐圧を大幅に向上できる。

(もっと読む)

過電流検出回路

【課題】カレントミラー回路を構成するトランジスタにおいて発生するアーリー効果の影響を排除して、過電流検出精度を向上可能な過電流検出回路を提供する。

【解決手段】過電流検出回路21が、MOSトランジスタ2により負荷1を通電駆動すると、負荷電流の1/nの電流をMOSトランジスタ3側に流し、更にその電流をカレントミラー回路6によりミラーさせて抵抗10及び電圧検出回路11により検出を行なう場合、カレントミラー回路6とMOSトランジスタ3並びに電流検出抵抗10との間に、アーリー効果キャンセル回路29を配置する。

(もっと読む)

スイッチ集積回路装置およびその製造方法

【課題】高周波スイッチMMICにおいてD型HEMTとE型HEMTを同一基板に形成し、D型HEMTのゲート電極をInGaP層にPtを埋め込んだ埋め込みゲート構造とする場合、埋め込まれたPtがInGaP層表面において横方向に異常拡散するため耐圧が低くなるという問題があった。

【解決手段】AlGaAs層とInGaP層を繰り返し積層した第1〜第3ノンドープ層と安定層を有するエピタキシャル構造とし、D型HEMTの第2ゲート電極を第3ノンドープ層(AlGaAs層)上に設け、E型HEMTの第1ゲート電極を第1ノンドープ層上に設ける。第2ゲート電極をPt埋め込みゲート構造とし、埋め込まれたPtの底部を第3ノンドープ層中に留まらせ、InGaP層(第2ノンドープ層)にPtが達しないようにする。これによりInGaP層表面におけるPtの横方向異常拡散を防止し、大幅に耐圧を向上させることができる。

(もっと読む)

フリップフロップ、集積回路、及びフリップフロップのリセット方法

【課題】 リセット配線を無くすことで、LSI内の配線の複雑化を防止でき、又は信号配線に利用できるチャネルを増やすことができるフリップフロップ、それを用いた集積回路、及びフリップフロップのリセット方法を提供する。

【解決手段】 電源電圧の変動を検出してリセットを行うフリップフロップにおいて、ハイ又はローレベルを記憶する状態保持ノード2と、所定値を越える電源電圧の変動を検出することで、状態保持ノード2の記憶状態をリセットするリセット信号を形成するリセット信号形成回路1とを備える。

(もっと読む)

薄膜トランジスタ回路

【課題】温度上昇を低減できる薄膜トランジスタ回路を提供する。

【解決手段】薄膜トランジスタQ1、Q2は充電期間においてオンし、薄膜トランジスタQ2、Q4は放電期間においてオンする。つまり、充電期間でオンする薄膜トランジスタと放電期間でオンする薄膜トランジスタとが交互に配置されている。

(もっと読む)

121 - 140 / 197

[ Back to top ]