Fターム[5J055AX00]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153)

Fターム[5J055AX00]の下位に属するFターム

スイッチの基本性能向上 (933)

性能の向上 (482)

物理量(温度等)変化の補償 (146)

スイッチ状態の表示、マンインターフェイス (2)

スイッチの操作性向上、誤操作の防止 (16)

誤動作防止 (777)

故障対策 (573)

信頼性向上のための変形 (218)

電源電圧変動の対策 (81)

試験、調整 (60)

構造上の改善、配置、配線等 (18)

簡素化、小型化 (492)

特定の規格を考慮しているもの (2)

課題の発生する時、注目している時 (638)

課題の解決手段 (518)

Fターム[5J055AX00]に分類される特許

21 - 40 / 197

レベルシフト回路およびスイッチング電源装置

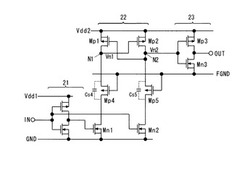

【課題】 高耐圧プロセスを使用することなく、回路的に高耐圧化したレベルシフト回路を実現できるようにする。

【解決手段】 一対のCMOSインバータを有し一方のインバータの出力ノードを他方のインバータのPチャネル型MOSトランジスタのゲート端子に交差結合してなるラッチ回路(22)と、該ラッチ回路のいずれか一方の出力ノードに接続されたCMOSインバータからなる出力段(23)とを有するレベルシフト回路において、ラッチ回路を構成する一対のCMOSインバータの各Pチャネル型のMOSトランジスタ(Mp1,Mp2)とNチャネル型のMOSトランジスタ(Mn1,Mn2)との間に、ゲート端子が電源電圧と接地電位の中間の電位が印加される第3電圧端子(FGND)に接続されたPチャネル型のMOSトランジスタ(Mp4,Mp5)をそれぞれ直列形態で設けた。

(もっと読む)

スイッチ装置および試験装置

【課題】入力電圧範囲の大きな半導体スイッチ装置を提供する。

【解決手段】外部から入力される制御電圧に応じて第1端子および第2端子間を電気的に接続または切断するスイッチ装置であって、第1端子および第2端子の間にソースおよびドレインが接続され、当該スイッチ装置に入力される入力電圧とゲート電圧との差に応じてオンまたはオフとなるメインスイッチと、制御電圧および入力電圧に応じて第1基準電圧を電圧シフトさせた駆動電圧をメインスイッチのゲートに供給する制御部と、を備えるスイッチ装置を提供する。

(もっと読む)

ゲート駆動回路

【課題】ゲート駆動信号の伝達遅延時間のばらつきを低減することができるゲート駆動回路を提供する。

【解決手段】ゲート駆動回路1は、トランス2を駆動するトランス駆動回路部3と、トランス2の一次側の駆動タイミングを生成すると共に、入力ゲート駆動信号のON状態時とOFF状態時とでトランス2の一次側駆動電圧変化率を異なるように設定するタイミング生成部4と、トランス2の二次側電圧を微分することで、トランス2の二次側電圧変化率を検出する微分回路部5と、入力ゲート駆動信号のOFF状態時の微分値レベルを検出するレベル検出回路部6と、入力ゲート駆動信号のON状態時の微分値レベルを検出するレベル検出回路部7と、検出レベル検出回路部6,7と接続されたR端子及びS端子を有し、出力ゲート駆動信号を生成・保持するフリップフロップ回路部8とを有している。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

周波数監視回路

【課題】より適切に安定した周波数監視を行うことが可能な周波数監視回路を提供する。

【解決手段】ウォッチドッグタイマ回路16は、キャパシタCの充放電を行う充放電部161と、充電電圧VCを基準電圧Va〜Vcと比較して比較信号Sa〜Scを生成する比較部162と、クロック信号CLKの周波数監視結果に応じたリセット信号S2を出力するリセット出力部163と、クロック信号CLKと比較信号Sa〜Scに基づいて充放電部161とリセット出力部163を制御する制御部164と、を有し、比較部162は、基準電圧Va〜Vcとして、上限電圧Vaと下限電圧Vbのほかに、中間電圧Vcを備えており、制御部162は、充電電圧VCと上限電圧Va及び下限電圧Vbとの比較結果のほか、クロック信号CLKのパルスエッジ到来時における充電電圧VCと中間電圧Vcとの比較結果に基づいて、リセット信号S2の論理レベルを決定する。

(もっと読む)

負荷駆動回路

【課題】ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能な負荷駆動回路を提供する。

【解決手段】電源3と負荷1との間に接続されたハイサイドスイッチとしてパワーMOSFET2を用いた負荷駆動回路10であって、パワーMOSFET のゲート電圧Vgと電源3の電源電圧Vpとを比較する比較回路11と、パワーMOSFET2のターンオフ動作においてパワーMOSFET2のゲート端子から電荷を放電させる遮断回路12とを具備し、遮断回路12によってパワーMOSFET2のゲート端子から電荷を放電させる放電速度は、ゲート電圧Vgが電源電圧Vpより高い場合の放電速度よりも、ゲート電圧Vgが電源電圧Vpより低い場合の放電速度が遅くなるように設定されている。

(もっと読む)

電気回路および/または電子回路に関するコンフィギュレーション方法ならびにデバイス

【課題】同じタイプの特性量を有し、この特性量の値が相互に比例するいくつかの機能ブロックを備える電気回路をコンフィギュレーションする。

【解決手段】機能ブロックは、同様のタイプの少なくとも1組の電気素子(102a〜102d、104a〜104d)と、前記電気素子を互いに接続するおよび/もしくは電気回路100の残部に接続するための手段(106a〜106d、108a〜108d、110a〜110d)とにより構築され、テストされる1組の接続コンフィギュレーションのそれぞれに対して、電気回路のパラメータの値を測定するステップと、テストされる結合コンフィギュレーションの中から、測定されたパラメータの値が、少なくとも1対の機能ブロックの特性量の値間の不整合が最小の1つのコンフィギュレーションを選択するステップと、選択されたコンフィギュレーションに従って、接続する手段をポジショニングするステップとを含む。

(もっと読む)

プログラマブルロジックデバイス集積回路上の高速シリアルデータレシーバ用のデシリアライザ回路網

【課題】多数の異なるプロトコルに対して、および広範囲のデーターレートに対して、シリアル形式のデータをパラレル形式のデータに変換することが可能な、デシリアライザ回路網を提供する。

【解決手段】プログラマブルロジックデバイス(「PLD」)などの高速シリアルデータレシーバ回路網用のデシリアライザ回路網(10)は、シリアルデータを任意の複数のデータ幅を有するパラレルデータに変換するための回路網を含む。該回路網(10)はまた、広範囲の周波数の中の任意の周波数で動作可能である。該回路網(10)は様々な観点において構成可能/再構成可能であり、その構成/再構成の少なくとも1部分はダイナミックに(すなわち、PLDのユーザーモードオペレ−ションの間に)制御され得る。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

切替回路及び受信回路

【課題】2つのクロック信号を切り替えて出力する切替回路において、出力信号のデューティ比を、入力されるクロック信号のデューティ比に保つこと。

【解決手段】切替回路100は、制御信号CONTに応じて、入力信号IN1,IN2を切り替えて出力信号OUTとして出力する。具体的には、制御信号CONTが「Lレベル」のときには、クロックドインバーターX2が動作し、信号IN1が信号OUTとして出力され、制御信号CONTが「Hレベル」のときには、クロックドインバーターX4が動作し、信号IN2が信号OUTとして出力される。

(もっと読む)

ランプ波形生成装置および方法

【課題】本発明は、ランプ波形生成装置および方法に関する。

【解決手段】ランプ波形生成装置は、入力信号を用いて基準波形を生成し、負荷の電圧と基準波形の電圧を比較して第1端子が負荷に連結していて第2端子が電源に連結しているスイッチをオンオフさせる駆動制御信号を生成する。このような駆動制御信号に応じてスイッチのオンオフが反復しながらランプ波形が生成される。

(もっと読む)

駆動回路及びこれを含む電源装置及び電気装置

【課題】駆動回路及びこれを含む電源装置及び電気装置を提供する。

【解決手段】制御端子及び出力端子を有するスイッチング素子、及び制御端子と出力端子との間の電圧が臨界電圧以下に維持されるように、前記スイッチング素子を制御するための駆動電圧が目標レベルに達するのにかかる上昇時間を制御する制御部を含み、制御端子と出力端子との間の電圧が臨界電圧より高ければ、制御端子と出力端子との間に漏れ電流が発生する電源装置である。

(もっと読む)

電子回路、パワーオンリセット回路、集積回路装置及び電子機器

【課題】電源投入時に初期状態を確実に設定できる電子回路、パワーオンリセット回路、集積回路装置及び電子機器等を提供すること。

【解決手段】電子回路は、各回路素子がトランジスターで構成される複数の回路素子XA1〜XB2と、第1の高電位電源電圧VDDが供給され、VDDが所定の電圧レベルになるまでは、低電位電圧レベルに設定され、VDDが所定の電圧レベルを越えると、VDDに追従して電圧レベルが上昇する第2の高電位電源電圧VINTを出力する電源出力回路100とを含む。複数の回路素子のうち、初期状態においてその出力ノードが高電位電圧レベルになる回路素子である第1のグループの回路素子XA1、XA2には、VDDが供給され、初期状態においてその出力ノードが低電位電圧レベルになる回路素子である第2のグループの回路素子XB1、XB2には、VINTが供給される。

(もっと読む)

半導体集積回路

【課題】 ゲート酸化膜の信頼性を維持しながら、待機時のリーク電流を抑制でき、回路面積の増加を最小限にでき、欠陥を確実に検出することができる半導体集積回路を実現する。

【解決手段】 論理回路10と電源電圧Vddの供給端子との間にスイッチング回路20を設ける。動作時に、スイッチング回路20のトランジスタMP0のゲートに0Vの電圧を印加し、チャネル領域に電源電圧Vddと同じかまたは僅かに低いバイアス電圧VBを印加することで、トランジスタMP0のしきい値電圧を低くし、その電流駆動能力を大きくする。待機時にトランジスタMP0のゲートに電源電圧Vddと同じ電圧を印加し、ソースに電源電圧より低い電圧を印可し、チャネル領域に電源電圧Vddと同じかまたはそれより高いバルクバイアス電圧VBを印加し、トランジスタMP0のドレイン電流を最少化することにより、論理回路10の電流経路を遮断し、リーク電流の発生を抑制する。

(もっと読む)

出力ドライバ回路

【課題】通信速度の高速化に加えて、消費電力の低減や、あるいは伝送波形品質の向上が図れる出力ドライバ回路を提供する。

【解決手段】例えば、正極および負極出力ノード(TXP,TXN)を電圧で駆動する電圧信号生成回路ブロックVSG_BKと、データ入力信号DIN_P,DIN_Nの遷移を受けてパルス信号を生成するパルス信号生成回路PGEN1,PGEN2と、当該パルス信号のパルス幅の期間でTXP,TXNを電流で駆動する電流信号生成回路ブロックISG_BKp1,ISG_BKn1を備える。電流信号生成回路ブロックは、TXP,TXNの寄生容量(Cp1,Cp2)を高速に充電すると共に、パルス幅に応じたプリエンファシスを行う。VSG_BKは、TXP,TXNにおける定常状態の電圧レベルを定めると共に、TXP,TXNをインピーダンスZ0で終端する。

(もっと読む)

電気光学装置、シフトレジスタ回路および半導体装置

【課題】ゲート線駆動回路の領域を効率よく利用できると共に、ゲート線選択信号の立ち上がり速度の低下(立ち上がり遅延)を防止できる電気光学装置、並びに、それに適した単一導電型のトランジスタで構成されたシフトレジスタ回路を提供する。

【解決手段】ゲート線駆動回路30は、複数のゲート線GLの奇数行を駆動する奇数ドライバ30aと、偶数行を駆動する偶数ドライバ30bとから成る。奇数および偶数ドライバ30a,30bの単位シフトレジスタSRの各々は、2行前の選択信号Gk-2を受け、その2水平期間遅れて自己の選択信号Gkを活性化させる。偶数ドライバ30bのスタートパルスSP1は、奇数ドライバ30aのスタートパルスSP2よりも1水平期間だけ位相が遅れている。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

データ出力回路

【課題】プリエンファシスまたはディエンファシスのためのドライバの追加がなくても、プリエンファシスまたはディエンファシス動作を行えるデータ出力回路を提供すること。

【解決手段】インピーダンスコードによって各々オン・オフされ、出力ノードにデータを出力する複数の駆動手段311、312を備え、前記インピーダンスコードが、前記駆動手段をターンオンさせる値を有する第1のグループと前記駆動手段をオフさせる値を有する第2のグループとに分けられ、プリエンファシス期間の間には、前記第2のグループによる制御を受ける駆動手段の全部または一部がターンオンされる。

(もっと読む)

集積回路、電子機器

【課題】複数の回路に接続されることにより共用される共用回路を有する集積回路において、接続される回路の切り替えが起こった場合においてもデータの損失を低減できる集積回路及びこの集積回路を有する電子機器を提供することを目的とする。

【解決手段】本発明にかかる集積回路は、複数の他の回路に接続可能な共用回路を備え、共用回路は、接続されている回路のクロックと同一のクロックで動作する。また、本発明にかかる電子機器は、本発明にかかる集積回路と、共用回路に接続する回路を切り替える際に、本発明にかかる集積回路に供給するクロックを一旦停止し、本発明にかかる集積回路が動作するクロックを前記共用回路に新たに接続される回路のクロックに切り替えた後に、本発明にかかる集積回路へのクロックの供給を再開する制御部と、を備える。

(もっと読む)

21 - 40 / 197

[ Back to top ]