Fターム[5J055AX00]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153)

Fターム[5J055AX00]の下位に属するFターム

スイッチの基本性能向上 (933)

性能の向上 (482)

物理量(温度等)変化の補償 (146)

スイッチ状態の表示、マンインターフェイス (2)

スイッチの操作性向上、誤操作の防止 (16)

誤動作防止 (777)

故障対策 (573)

信頼性向上のための変形 (218)

電源電圧変動の対策 (81)

試験、調整 (60)

構造上の改善、配置、配線等 (18)

簡素化、小型化 (492)

特定の規格を考慮しているもの (2)

課題の発生する時、注目している時 (638)

課題の解決手段 (518)

Fターム[5J055AX00]に分類される特許

161 - 180 / 197

半導体装置

【課題】電源電圧を正確に検知してパワーオンリセット信号を出力する。

【解決手段】電源電圧を受けて基準電圧を発生する基準電圧発生回路10と、基準電圧の値が規定値に達したことを検知する基準電圧レベル保障回路20と、基準電圧レベル保障回路20の検知信号に基づいて動作が制御され、電源電圧に応じた値を持つ電圧を基準電圧と比較する電圧比較回路を有し、この電圧比較回路の比較結果に基づいてパワーオンリセット信号を出力する電源電圧検知回路30とを具備する。

(もっと読む)

サンプルホールド回路

【課題】高精度なサンプルホールド回路を提供する。

【解決手段】サンプル期間において、スイッチS1およびスイッチ回路S4はON状態、スイッチS3はOFF状態にされる。切替期間において、まず、スイッチ回路S4がOFF状態に切り替えられ、次にスイッチS1がOFF状態に切り替えられ、続いて、スイッチS3がON状態に切り替えられる。各トランジスタQ1,Q2は同一トランジスタサイズであり、各ゲート・ドレイン容量Cn,Cpは等しい。そこで、バイアス電圧TPHを適宜設定することにより、各スイッチS4a,S4bがOFF側に切り替わる際にクロック・フィールド・スルーによって各ゲート・ドレイン容量Cn,Cpに蓄積される各電荷Qn,Qpを互いに打ち消し合わせ、コンデンサC1に蓄積させないようにする。ホールド期間において、スイッチS1およびスイッチ回路S4はOFF状態、スイッチS3はON状態にされる。

(もっと読む)

PLL回路及びそのプログラム

【課題】チャージポンプ回路に入力されるUP/DN信号の入力波形等まで含めて、Isrc-Isnk誤差を補正する手段を有し、さらに高精度を実現できるPLL回路及びそのプログラムを提供する。

【解決手段】位相周波数検出回路(1.1 PFD)の出力信号UPB/UPを、常時ロック状態信号としてレプリカチャージポンプ回路(1.4 CPR)に入力し、積分した参照電圧信号(1.4-1 VpmpR)と、電圧制御発振回路(1.7 VCO)を所望の電圧にてコントロールするため、位相周波数検出回路の出力信号UPB/DNをチャージポンプ回路(1.3 CP)に入力し、積分したPLL回路制御電圧信号(1.3-1 Vpmp)とを、補正電圧発生回路(1.5 CMP)にて比較し、比較結果の補正電圧信号(1.5-1 Vcmp)にてチャージポンプ回路及びレプリカチャージポンプ回路のバイアス電流を制御するチャージポンプバイアス回路(1.2 CPBias)を制御する。

(もっと読む)

三値論理関数回路及び多値論理関数回路

【課題】 33^2=19683種類存在する全ての二変数三値論理関数回路を実現するために必要となる基本回路の種類を著しく削減するとともに、スイッチング時間の非対称性も著しく小さくすることができる三値論理関数回路を提供する。

【解決手段】 二変数三値論理演算を行う三値論理関数回路は、第1の入力aを構成する3つの論理値−1,0,1に応じて、一変数三値論理関数回路C1,D1,C2,D2,C3,D3によって3つのトランスファーゲートT1,T2,T3を導通又は遮断し、第2の入力bに接続される3つの一変数三値論理関数回路B1,B2,B3の出力を選択する。

(もっと読む)

半導体装置

【課題】一つの外部入力端子に接続される複数の入力回路を備える半導体装置を安定的に動作させる。

【解決手段】外部入力端子PADに抵抗素子R1、R2、R3、R4をそれぞれ介して接続される入力回路10、11、12、13は、それぞれ供給されるクロック信号CK10、CK11、CK12、CK13のレベル遷移に応じて活性化して入力信号を取り込む。外部入力端子PADに印加される信号を入力するために、それぞれの入力回路には、それぞれ位相の異なるクロック信号が供給される。外部入力端子に供給されるシリアルデータを位相の異なるクロック信号で順次入力回路に振り分けて入力することで一つの入力回路のサイクルタイムを長くすることができる。この時、抵抗素子R1、R2、R3、R4で各入力回路が分離されているため、各入力回路の初段で発生するキックバック信号の、他の入力回路への影響を極めて小さくすることができる。

(もっと読む)

耐圧入力バッファ回路

【課題】 電源電圧、温度、プロセス変動等によっても立上り遅延のバラツキが小さくなり、且つ、立上り遅延と立下り遅延の差も小さくなるようにすること。

【解決手段】 電源電圧VDDより高い入力電圧Vinを電源電圧VDDより低い電圧に低下させる耐圧回路2と、耐圧回路2の出力電圧から高周波ノイズ成分を除去するRCフィルタ回路4と、RCフィルタ回路4の出力電圧に応じて反転/復帰するシュミットインバータ回路5と、耐圧回路2の出力電圧V1がハイレベルで且つRCフィルタ回路4の出力電圧が所定の電圧以上のときRCフィルタ回路4のRC時定数を小さな値に切り替える時定数切替回路8を設けた。

(もっと読む)

半導体集積回路

【課題】外部クロックに同期して内部クロックを発生させ、この内部クロックを用いてオフチップドライバ回路におけるデータ出力動作を制御する際に、オフチップドライバ回路の出力データが“H”レベルと“L”レベルのどちらでもあっても、オフチップドライバ回路における信号遅延時間を補償する。

【解決手段】出力制御信号に基づいてデータを出力し、“H”レベルデータ出力時と“L”レベルデータ出力時における出力制御信号からデータ出力までの信号遅延時間が異なるオフチップドライバ回路92と、上記オフチップドライバ回路で“H”レベルデータの出力時に使用される第1の出力制御信号を発生する第1の出力制御信号発生回路94aと、上記オフチップドライバ回路で“L”レベルデータの出力時に使用される第2の出力制御信号を発生する第2の出力制御信号発生回路94bとを具備している。

(もっと読む)

過電流保護回路及びこれを備えるインバータ

【課題】過電流保護回路において、負荷のインダクタンス及び寄生容量による発振を抑制する。

【解決手段】MOSFET50のドレイン端子に負荷54が接続され、ゲート端子に駆動信号が供給される。MOSFET50のソース端子とゲート端子間にトランジスタ62を含むフォードバック回路を接続してドレイン電流を制限する。MOSFET50のドレイン端子とゲート端子間に、互いに直列接続された抵抗R72及びキャパシタC74を接続し、出力電圧の発振を抑制する。

(もっと読む)

セレクタ回路

【課題】配線面積の増大や信号波形の鈍り、信号伝達の遅延を抑制すること。

【解決手段】入力信号の導通を制御するパストランジスタ回路21a〜21dと、各パストランジスタ回路21a〜21dから出力された出力信号を配線24a,24bを介して受け付けてNAND演算をおこなうNAND回路22と、同一の配線24a,24bに接続されたすべてのパストランジスタ回路21a〜21dにより入力信号の導通が遮断された場合に、当該配線24a,24bの信号レベルを設定するpチャネルトランジスタ回路23a,23bと、導通させる入力信号を1つだけ選択するようパストランジスタ回路21a〜21dを制御する制御信号、および、配線24a,24bの信号レベルを設定するようpチャネルトランジスタ回路23a,23bを制御する制御信号を同一の入力信号に対して論理演算をおこなうことにより生成する制御信号生成回路とを備える。

(もっと読む)

誘導性負荷駆動装置および誘導性負荷駆動方法

【課題】 位置決め制御などで2つのモータを独立に駆動するような場合であっても、電源から供給される電流を平滑化するとともに、電源から大きな電流が供給される頻度を大幅に低減する。

【解決手段】 位相差が1/2波長の鋸波搬送波C、Dにもとづいて第1PWM制御信号生成部36、第2PWM制御信号生成部37が第1、第2PWM制御信号を生成し、該第1、第2PWM制御信号によって2つのDCモータを作動させることにより、どちらか一方のDuty比が50%を超えない限り、電源から2つのDCモータへの電流流入のタイミングが重なることがないので、双方のDuty比が刻々と変化するような場合であっても、電源から供給される電流を平滑化するとともに、電源から大きな電流が供給される頻度を大幅に低減することができる。

(もっと読む)

高周波スイッチ回路

【課題】 簡素化された回路構成を有し、信号伝送損失の増大が回避でき、半導体高周波スイッチ1の切替接続に3本の制御線13を用いて切替制御系を簡単な構成にした高周波スイッチ回路を提供する。

【解決手段】 信号伝送を第1送受信方式で行う第1通信システム、第1送受信方式より高レベルの信号伝送を第2送受信方式で行う第2通信システムを切替える高周波スイッチ回路で、切替制御手段によって可動接点4が第1乃至第3分岐端子3(1)乃至3(3)に切替接続される半導体高周波スイッチ1を用い、可動端子2に共用アンテナ5を、第1分岐端子3(1)に第1通信システムにおける送受信回路を、第2分岐端子3(2)に第2通信システムにおける送信回路を、第3分岐端子3(3)に第2通信システムにおけるの受信回路をそれぞれ接続し、選択的に可動接点4を第1乃至第3分岐端子3(1)乃至3(3)のいずれかに切替接続する。

(もっと読む)

パワー半導体スイッチを駆動するための集積回路装置

【課題】 単独パワー半導体スイッチ又はハーフブリッジ回路内のパワー半導体スイッチを駆動するための集積回路装置を紹介する。

【解決手段】 スイッチ(40)用の少なくとも1つの第1レベルシフタ(730)を少なくとも含んでいる複数の機能グループを有する第1駆動チップ(72)と、第2レベルシフタ(740)とスイッチ(40)のドライバ(746)とを少なくとも含んでいる複数の機能グループを有する少なくとも1つの第2駆動チップ(74)とから回路装置が構成されていて、少なくとも1つの第2駆動チップが第1駆動チップに後続接続されていて、第2駆動チップの基準電位が、第1駆動チップのレベルシフタの出力電位上に位置し、それらの駆動チップが互いに適切な絶縁状態をもって共通のハウジング(70)内に配設されていること。

(もっと読む)

電流出力型駆動回路および電子機器

【課題】比較的小規模なプログラムにより多種類の点滅パターンを実現することができる電流出力型駆動回路および電子機器を提供する。

【解決手段】制御レジスタ14に格納され、論理回路13により論理演算が行われた基準電流設定データに基づいて基準電流発生回路12の可変電流源VIS−iにより可変の基準電流IREFを出力し、電流出力型DAC2−iの基準抵抗回路Rrefに発生した基準電圧Vrefに基づいて誤差増幅回路3−iにより電流出力型DAC2−iの出力電流を制御してLED1−iを駆動する。

(もっと読む)

高周波スイッチ回路及び半導体装置

【課題】トランジスタに生じる寄生ダイオードを常にオフに保ち、寄生ダイオードを介して流れる電流による信号損失を抑える高周波スイッチ回路及び半導体装置を提供する。

【解決手段】一端が送信端子2に接続され、他端が高周波信号が入出力される入出力端子1に接続されたMOSFET4と、一端が受信端子3に接続され、他端が入出力端子1とMOSFET4の他端との接続点に接続され且つMOSFETと相補的に動作するMOSFET5と、一端が入出力端子1とMOSFET4との接続点に接続され、他端側に流れる高周波信号を制限するための抵抗R6と、抵抗R6の他端に接続され、所定の電圧を印加するためのバイアス印加用端子14とを備えた。

(もっと読む)

セレクタ回路及び半導体装置

複数の信号から選択した信号を精度良く出力することのできるセレクタ回路。ラッチ回路部(13)は、選択回路部(12)での選択動作を制御する内部選択制御信号(sn,sp)を生成する。選択回路部(12)は、第1及び第2のデータ入力信号(IN1,IN2)のレベルが互いに一致しないとき、内部選択制御信号(sn,sp)に従って各信号(IN1,IN2)のレベルが互いに一致するまで選択されている状態を保持して、選択信号(S)に基づく切替え動作を行わない。  (もっと読む)

(もっと読む)

可変減衰回路及び該可変減衰回路を用いた減衰制御システム

【課題】 減衰量の変化範囲においても歪みの発生が少ない可変減衰回路を提供する。

【解決手段】 入力端子11と出力端子12との間に縦続接続して介挿された二つのスイッチ素子13、14と、スイッチ素子13、14の出力端子12側の一端をグランドにシャントする充電コンデンサ15、16とを備え、スイッチ素子13、14にそれぞれ放電抵抗17、18を並列接続し、スイッチ素子13、14を減衰量に対応した繰り返し周波数でオン/オフすることで信号を断続し、オン時に信号の電圧を充電コンデンサ15、16に充電し、オフ時に放電抵抗17、18で放電した。

(もっと読む)

パワー・オン・リセット回路

【課題】 ゼロ閾値電圧トランジスタに決定的に依存しないで、前縁部分及び後縁部分を有するパワー・オン・リセット信号を発生する回路及び方法を提供する。

【解決手段】 回路は、パワー・オン・リセット信号の前縁部分を発生する起動回路と、パワー・オン・リセット信号の後縁部分を発生する第2の回路とを含む。パワー・オン・リセット回路は、パワー・オン・リセット信号の後縁部分を発生する回路を制御するためにゼロ閾値電圧を有する在来のデバイスに信頼を置かないプロセスによって履行される。

(もっと読む)

半導体集積回路

【課題】 低電源圧下でも高速動作し、待機時においてはサブスレッショルドリークを抑制し出力データを保持できる半導体回路装置の提供。

【解決手段】 信号入力端子INに共通に入力端が接続され、互いに等しい論理構成の第1及び第2の伝送系1、2を備え、第1の伝送系への入力値がロウレベルのときにオフとなるトランジスタが高しきい値とされ、オンとなるトランジスタが低しきい値とされ、第2の伝送系への入力値がハイレベルのときに、オフとなるトランジスタが高しきい値とされ、オンとなる側のトランジスタが低しきい値とされ、第1及び第2の伝送系は、制御信号に基づき、動作状態と待機状態とに制御され、第1及び第2の伝送系の出力INL、INHを受け、動作時は、低しきい値のトランジスタがオン状態となる側の伝送系から、待機時は、出力が不定状態の一方の伝送系からの出力を遮断し、伝送系から出力する出力選択部3を備えている。

(もっと読む)

インタフェース回路

【課題】 P1形およびP2形のうちの所望の形式で使用することができ、応答速度が速いインタフェース回路を提供する。

【解決手段】 インタフェース回路をP1形で使用する場合は端子T4とT6を接続し、P2形で使用する場合は端子T5とT6,T7とT8をそれぞれ接続する。車両感知信号/Dが活性化レベルの「L」レベルになると、P1形の場合はフォトトランジスタ6が導通せず、出力端子T2,T3間が非導通状態になり、P2形の場合はフォトトランジスタ6が導通し、出力端子T2,T3間が導通状態になる。従来のフォトMOSトランジスタの代わりにフォトトランジスタ6を使用したので、応答速度が速くなる。

(もっと読む)

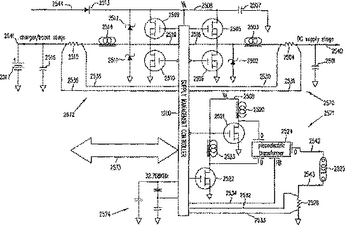

パワーコンバータ回路及び方法

複数のタイプが異なるスイッチングパワーコンバータの動作を同時に調整するコントロールシステムおよび方法。本システムは、パワーコンバータでサンプリングされたデータ及び非線形フィードバック制御ループの調整に用いる。  (もっと読む)

(もっと読む)

161 - 180 / 197

[ Back to top ]