Fターム[5J055AX66]の内容

Fターム[5J055AX66]に分類される特許

1 - 20 / 47

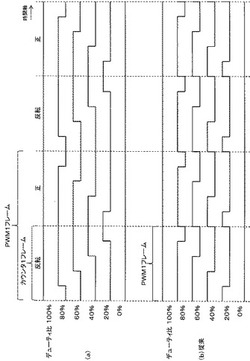

ドライバ及びその使用方法

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

スイッチ回路

【課題】多くの個別素子による回路を用いることなく、容易に簡素な回路構成で端子外れ検出を行うことが可能なスイッチ回路の提供。

【解決手段】ゲートがセンサ回路に接続され、ドレインが第1の電圧制限抵抗に接続された第1の出力ドライバと、物理量検出信号出力端子と接地端子の間に接続された第2の電圧制限抵抗と、非反転入力端子が第1の基準電圧回路に接続され、反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第1の比較器と、反転入力端子が第2の基準電圧回路に接続され、非反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第2の比較器と、ゲートが前記論理回路の出力に接続され、ドレインが断線診断信号出力端子に接続された第2の出力ドライバで構成した。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

半導体装置

【課題】駆動用のスイッチ素子によって出力端子からの出力を制御する半導体装置において、端子に静電気が印加されたときに、スイッチ素子をより確実に保護し得る構成を、装置構成の大型化を抑えて実現する。

【解決手段】半導体装置1は、高電位側電源又は低電位側電源の一方からなる基準部にスイッチ素子の第1端子が接続され、出力端子P1にスイッチ素子の第2端子が接続されている。また、スイッチ素子と並列に第1保護素子が設けられている。また、基準部とは逆側の電源(他方部)と出力端子の間には第2保護素子が接続されている。そして、基準部とは逆側の電源(他方部)側には無効化手段が接続され、出力端子へのサージ電圧の印加によって駆動電圧が発生した場合に、当該駆動電圧の発生後の所定時間、制御入力端子への通電信号の入力を無効化し、所定時間の経過後に無効化を解除するように機能している。

(もっと読む)

負荷駆動回路

【課題】簡単な構成で負荷オープン状態を検出することができる負荷駆動回路を提供する。

【解決手段】電源端子T1に入力される入力電圧Vinよりも低い基準電圧V1と出力端子T2の電圧Voutとを比較する第1のコンパレータ8と、スイッチング素子2がオフ状態で、且つ負荷オープン状態である場合に、出力端子T2の電圧Voutを基準電圧V1よりも高く、且つ入力電圧Vinよりも低いclamp電圧にクランプするクランプ回路7とを備えることにより、第1のコンパレータの出力によって、負荷オープン状態を検出する。また、入力電圧Vinよりも低く且つclamp電圧よりも高い基準電圧V2と出力端子T2の電圧Voutとを比較する第2のコンパレータ9を備えることにより、第1のコンパレータ及び第2のコンパレータ9の出力によって、負荷オープン状態と出力天絡状態とを検出する。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるスイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続され、第1のコンデンサC1と第1の抵抗R1とからなる並列回路と、スイッチング素子のゲートとソースとの間に接続され、制御信号のオフ信号に対して遅延させてゲートとソースとの間を短絡する短絡手段S4とを備える。

(もっと読む)

半導体装置

【課題】ハーフブリッジ回路のメインスイッチング素子が同時オンになることを確実に防止する。

【解決手段】ローサイド側の入力信号を遅延させてローサイド側遅延信号として出力する遅延回路20と、ハイサイド側の入力信号からハイサイド側セット出力信号と予備リセット信号とを生成して出力するパルス発生回路12と、ローサイド側の入力信号がアクティブになってからローサイド側遅延信号がアクティブになるまでの期間、又は予備リセット信号がアクティブである期間にハイサイド側リセット出力信号をアクティブにするリセット信号生成回路30と、を備えるハーフブリッジドライバとする。

(もっと読む)

スイッチング素子の駆動回路

【課題】パワーデバイス(メインスイッチM)のゲートの印加電圧をバッテリ12の正電圧より高い電圧と負電圧との双方の電圧とする場合、電源装置の小型化が困難なこと。

【解決手段】バッテリ12、端子T3、スイッチング素子SW1、コンデンサC、スイッチング素子SW2、逆流防止用ダイオードD1、端子T1および充電用抵抗体14によって、メインスイッチMのゲート充電経路が構成される。また、放電用抵抗体16、端子T2、逆流防止用ダイオードD2、スイッチング素子SW3、コンデンサC,スイッチング素子SW4、および端子T4によって、メインスイッチMのゲート放電経路が構成される。さらに、端子T3、スイッチング素子SW6、逆流防止用ダイオードD4、コンデンサC、逆流防止用ダイオードD3、スイッチング素子SW5および端子T4によって、コンデンサCの充電経路が構成される。

(もっと読む)

ゲートタイミング制御回路

【課題】半導体スイッチ,負荷電流,温度,主回路構成等によるサージ電圧の波形に応じて半導体スイッチの動作タイミングを調整することなく、各半導体スイッチの電圧分担を均等化させる。

【解決手段】直列接続された複数の半導体スイッチA,Bに出力されるゲート信号のタイミングを調整するゲートタイミング制御回路3において、コンパレータ4,4により、各半導体スイッチA,BのVce検出(A),(B)と、予め設定されたしきい値とを比較してVce検出における立ち上がりのタイミングを示すVce信号(A),(B)を出力する。そして、時間差制御部8において、ゲート信号に基づいて、前記各Vce信号(A),(B)の変化のタイミングが整合するように生成されたゲート出力(A),(B)をゲートドライバ2に出力する。

(もっと読む)

スイッチング回路

【課題】スイッチング素子の動作に起因するノイズの大きさが低減された、小型で製造コストの低いスイッチング回路を提供する。

【解決手段】スイッチング素子と、一定周期でパルス波のドライバ信号を出力するドライバ信号出力回路と、ドライバ信号のパルス波の周期を複数含む一定期間内において駆動力を変化させながら、ドライバ信号の周期に同期してスイッチング素子を駆動する駆動回路とを備える。

(もっと読む)

ドライバ回路

【課題】単電源駆動で、歪が小さく、大振幅の信号出力電圧が得られるドライバ回路を提供する。

【解決手段】1は入力端子、2、3は出力端子、4は第1の反転型オペアンプ、5は第2の反転型オペアンプ、6は非反転型オペアンプ、7はトランス、8は正電源電圧VCC、9はアナロググランドAGND(VCC/2)、10はグランドGND(0V)を示す。第1の反転型のドライバ用オペアンプの出力を第2の反転型のドライバ用オペアンプと非反転型のドライバ用オペアンプで受け、それらの出力を差動構成とすることで、低電圧での単電源駆動でも大振幅で、歪の小さい出力信号電圧が得られる構成とした。

(もっと読む)

駆動回路

【課題】電圧駆動型素子のスイッチング特性におけるトレードオフ関係を改善する駆動回路を提供すること。

【解決手段】駆動回路1は、ゲート抵抗R1とそのゲート抵抗R1に対して並列に接続されている分岐回路部23を備えている。分岐回路部23は、分岐ゲート抵抗R3とツェナーダイオードZD1を有するとともに、分岐ゲート抵抗R3とツェナーダイオードZD1が直列に接続されている。ツェナーダイオードZD1のカソードが駆動電源V1の正極端子14側に接続されており、ツェナーダイオードZD1のアノードがトランジスタTr1の制御端子12側に接続されている。

(もっと読む)

スイッチング駆動回路

【課題】オンオフ動作させる外部機器のEMIによる誤作動を確実に防ぐスイッチング駆動回路を提供する。

【解決手段】スイッチング駆動回路1は、LED4をオンオフ動作させるスイッチ素子であるpMOSトランジスタT1と、pMOSトランジスタT1のゲートソース間の抵抗10と、抵抗10に制御電流を供給するnpnトランジスタT4を含むカレントミラー回路と、抵抗10及びnpnトランジスタT4との間に設けられる遮断回路としてのnMOSトランジスタT5とを備える。制御信号がLED4を消灯制御するローレベルLのときにnMOSトランジスタT5を同時にオフすることで、EMIの影響により抵抗10から流れ込出す電流を遮断する。これにより、LED4の誤点灯を確実に防ぐ。

(もっと読む)

サンプルホールド回路

【課題】インバータなどの遅延が無視できない高速動作時において、クロックフィールドスルーの影響を改善するのが困難

【解決手段】MOST4はソース端子に入力されるアナログ入力信号を矩形波パルスのサンプル信号によりオンオフしてサンプリングする。MOST5はMOST4のドレイン端子にソース端子およびドレイン端子が接続されサンプル信号の極性を反転した反転サンプル信号によりオンオフしてMOST4の寄生容量を補償する。論理回路10,11はサンプル信号と反転サンプル信号の位相差を検出して誤差信号を出力する。MOST6,7はMOST5のソース端子およびドレイン端子にソース端子およびドレイン端子が接続され、位相差を補償する。

(もっと読む)

半導体スイッチ及び充電回路

【課題】保護回路を内蔵した半導体スイッチ及び充電回路を提供する。

【解決手段】実施形態によれば、スイッチ素子と駆動回路と保護回路と制御回路とを備えた半導体スイッチが提供される。スイッチ素子は、電源線と出力線との間に接続される。駆動回路は、入力信号に応じて前記スイッチ素子をオンまたはオフに駆動する。保護回路は、前記スイッチ素子の過電流を検出したとき前記スイッチ素子の電流を上限値に制限するクランプモードと、前記スイッチ素子を交互にオンとオフとに切り替えるスイッチングモードと、を有する。制御回路は、前記スイッチ素子がオンしたとき前記保護回路を前記クランプモードに制御し、前記スイッチ素子がオンしてから規定時間経過後に前記出力線の短絡を検出したとき、または前記出力線の短絡を検出せずに前記出力線の電圧が規定値に達したとき前記保護回路をスイッチングモードに制御することを特徴とする。

(もっと読む)

誘導性負荷を接続するための方法、及び、その方法を実行するための接続回路

【課題】最小限の突入電流の発生にとどめることを課題としている。

【解決手段】

本発明は、誘導負荷、特に発電機(12)の巻き線(13)を所定の交流中間電圧に接続するための方法に関し、誘導負荷は、ブレーカー(17)を用いて中間電圧に接続されている。突入電流を減少させるために、中間電圧が所定の位相にある場合に、接続がなされるように調節される。

(もっと読む)

電源復帰検出回路

【課題】電圧比較器を用いることなく、電源遮断ブロックの電源復帰を検出する。

【解決手段】電源遮断ブロック1に配置された信号遅延回路11と、電源が常時供給される常時オンブロック9に配置された測定パターン生成回路13、測定パターン検出回路15及び遅延時間測定回路17を備えている。遅延時間測定回路17は、測定パターン生成回路13から送信された測定パターンが信号遅延回路11を介して測定パターン検出回路15に到達するまでの遅延時間を測定する。電源遮断ブロック1の電源が遮断状態から投入状態に切り替えられた後、上記遅延時間が信号遅延回路11の設計値に基づく所定の遅延量以内になったときに、電源遮断ブロック1の電源が復帰したと判断する。

(もっと読む)

ゲート駆動回路及びゲート駆動方法

【課題】トランジスタの駆動電力の損失を防ぎ且つスイッチング時間の高速化を図る。

【解決手段】接合型トランジスタ2の駆動に必要な基準駆動能力レベル電圧からなる基準波形Sg′及び駆動能力のより高い高駆動能力レベル電圧からなる重畳パルスSpを生成し、重畳パルスSpのパルス幅を、接合型トランジスタ2のスイッチング時間に、若しくはドレイン電位VDの遷移収束タイミングを表す閾値により設定する。基準波形Sg′と重畳パルスSpとを重畳しこれを、接合型トランジスタ2のゲート駆動信号Sgとする。ゲート駆動信号Sgは、接合型トランジスタ2の遷移終了とみなすことの可能なタイミングで基準駆動能力レベル電圧に切り換わることになるため、遷移終了後も高駆動能力レベル電圧で駆動されることにより、接合型トランジスタ2に形成されるダイオードに順方向電流が流れることに伴う電力損失の発生を回避することができる。

(もっと読む)

1 - 20 / 47

[ Back to top ]