Fターム[5J055DX01]の内容

Fターム[5J055DX01]に分類される特許

41 - 60 / 187

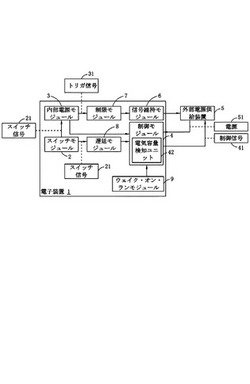

電子装置およびその外部電源供給装置の制御方法

【課題】電子装置およびその外部電源供給装置の制御方法を提供する。

【解決手段】本発明による電子装置1は、オン状態とオフ状態を有する外部電源供給装置5と電気接続し、該電子装置はスイッチモジュール2と、内部電源モジュール3とを含み、スイッチモジュールが触発されると、スイッチ信号を生成する。内部電源モジュールは、スイッチ信号を受信し、トリガ信号を生成して、外部電源供給装置に伝送することにより、外部電源供給装置をオフ状態からオン状態に切り換え、該外部電源供給装置は、電子装置に電源を供給する。

(もっと読む)

バーストモード制御回路

【課題】バースト動作区間で一定区間ごとにパルスを発生させるために用いられるクロックシフターの数を減少させることによって、LPDDR2で回路の具現が容易で且つ電流消耗を節減できるようにするバーストモード制御回路を提供する。

【解決手段】バーストモード動作区間の間にイネーブルされるバースト区間信号を生成するバースト区間信号生成部と、リードコマンド及びライトコマンドに応答してバースト区間信号のイネーブル区間の間に所定周期ごとに生成されるパルスを含むバーストパルスを生成するバーストパルス生成部と、バーストパルス及びクロック信号を受信してバーストモード動作区間の間にデータ入出力を制御するカラムアクセス信号を生成するカラムアクセス信号生成部と、を含む構成とした。

(もっと読む)

相互接続構造および論理回路装置

【課題】外部配線と複数の論理セルを含む論理セル群とを相互に接続する相互接続構造、および相互接続構造を有する論理回路装置に関し、論理のファンクション表現の柔軟性を低下させることなく配線リソースのオーバヘッドを低減させることを目的とする。

【解決手段】論理回路装置における相互接続部1が、外部配線と論理セル群2の入力線と相互接続関係を規定する接続規定手段を有し、論理セル群の複数の論理セルの中で対象となるファンクションを考慮して、論理のファンクション表現に関する柔軟性を保ちつつ、相互接続部の入力線の数が相互接続部の出力線の数より少ない構成、および、接続規定手段により規定される組み合わせ数が相互接続部の入出力の全ての組み合わせ数より少ない構成の少なくとも一方が実現されるように構成される。複数の論理回路装置のクラスタ化により形成されるクラスタ構造を有する論理回路装置も提供される。

(もっと読む)

半導体集積回路

【課題】製造後であっても、電源スイッチの特性を変更できるようにする。

【解決手段】本発明に係る半導体集積回路1は、複数の電源線2,3間の接続を切り換える複数の電源スイッチ5を有する半導体集積回路1であって、前記電源スイッチ5の少なくとも1つは、複数の前記電源線2,3間に接続されたトランジスタ40と、設定値を保持する設定値保持部42と、前記設定値に基づいて、前記トランジスタ40の接続状態を切り換える接続制御信号を、複数の制御信号の中から選択する選択部41とを有する。

(もっと読む)

自己タイミング型時分割多重化バスを使用した相互接続

集積回路の通信バス上のトランスポートユニット間でデータ及びタイミング情報を含む信号を送信する方法は、バス上のすべてのトランスポートユニットのクロックトリガを生成するステップであって、それによって、各先行トランスポートユニットを起動して、隣接する後続トランスポートユニットへウェイブ-フロントで前記信号の送信を開始し、該ウェイブ-フロントはトランスポートユニットのそれぞれにおいて共通の時点で起動される、生成するステップと、すべてのトランスポートユニットが、自身が前記先行トランスポートユニットから前記信号で受信するデータ及びタイミング情報の少なくとも一方にタイミング調整を適用するステップを備えており、該適用するステップは、(1)先行トランスポートユニットからの前記データをキャプチャすること、(2)先行トランスポートユニットから前記後続トランスポートユニットへ通信バス上で前記データを変更することなく中継すること、及び(3)通信バスへ新たなデータをロードすること、の少なくとも1つを、更新されたタイミング情報を用いて後続のウェイブ-フロントで行う。  (もっと読む)

(もっと読む)

カウント装置

【課題】 カウント入力回路への被カウント信号配線は変更することなく、その被カウント信号をカウントするカウンタを変更したり、あるいは1のカウンタ入力回路へ供給される被カウント信号を、複数のカウンタへ並列に供給することを可能とする。

【解決手段】 入力回路(11−1〜4)の各出力端とカウンタ(13−1〜4)の各入力端との間には分配切替回路(12)が介在され、分配切替回路は、入力回路の各出力端のそれぞれに接続される入力側端子(IN0〜IN1)と、カウンタの各入力端のそれぞれに接続される出力側端子(OUT1〜OUT4)とを有し、かつ入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通は、任意に設定可能とされる。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

半導体装置

【課題】プログラムの変更を行わずに、ウォッチドッグタイマの動作を検証する。また、ウォッチドッグタイマのタイムアウトを外部で確認する。

【解決手段】本発明の半導体装置(1)は、ウォッチドッグタイマ(2)と中央処理装置(3)とモード端子(4)とを有する。前記中央処理装置は、前記ウォッチドッグタイマのタイムアウト制御を制御する。前記ウォッチドッグタイマは、前記モード端子を介して、前記ウォッチドッグタイマのタイマ周期を前記中央処理装置のタイムアウト制御による周期よりも短くする指示を外部から与えられる。前記ウォッチドッグタイマは、前記指示に応答して、前記中央処理装置によるタイムアウト制御よりも先に、タイムアウトを検出する。

(もっと読む)

受動キーパッドにおける入力範囲間での区別化

【課題】受動キーパッドにおける入力範囲間での区別化をする。

【解決手段】スイッチS1...Snを有する受動回路網100のスイッチ投入を処理する方法および回路。受動回路網100は、スイッチ投入に応じて出力電圧を発生する。この回路は、受動回路網に結合され、出力電圧を基準電圧と比較する比較回路206を備えている。比較回路に結合されたデコーダ212は、出力電圧が所定の範囲内にある場合、スイッチ投入を復号化し、出力電圧が所定の範囲内にない場合、前記スイッチ投入を復号化しない。この回路は、意味あるキープレスの適切な処理ができると同時にうっかりとやったあるいは不注意なキープレスを無視し、それによって電力およびプロセッサ時間を確保する受動回路網キーパッドの入力範囲間で区別する。

(もっと読む)

プログラマブルロジックデバイス、カード及び伝送装置

【課題】 冗長構成とすることなく、デバイスの運用を中断せずに機能の更新が可能となると共に、冗長分のコスト及び消費電力を削減できるプログラマブルロジックデバイス、カード及び伝送装置を提供する。

【解決手段】 FPGA10は、入力される入力信号を複数に分配し、論理ブロックに既に構成された論理回路1及び論理ブロックに新規に構成される新規な論理回路11に対して、分配された信号を出力する分配回路部2と、論理回路1及び新規な論理回路11からの各出力信号のうちいずれかを選択するセレクタ回路部3と、新規な論理回路11に出力信号を出力するように分配回路部2を制御すると共に、新規な論理回路11からの出力信号を出力するようにセレクタ回路部3を制御する切り替え制御部4と、を備える。

(もっと読む)

家電用制御回路

【課題】点検時期を定刻以内に報知させ得る家電用制御回路を提供する。

【解決手段】家電用制御回路100は、電池12の電力を伝達させるバッテリラインLaと、電池12から供給された電力によって駆動され且つ電池12による電力の供給開始時点から起算して電力供給の経過時間を計数する時間カウント回路11とを備え、バッテリラインLaは、時間カウント回路11と、電池12の電圧値を検出するAD変換回路A/Dとに接続されることとする。これにより、マイコンCOMでは、電池12の電圧値が認識され、当該電池の消耗状態の判定を行うことが可能となる。

(もっと読む)

電子部品装置

【課題】少ない制御線で複数個のスイッチの自在な制御を実現する。

【解決手段】電子部品装置は、複数個のスイッチSW−1〜SW−Nと、スイッチ制御回路1とを備える。スイッチ制御回路1は、複数のスイッチ制御パタンを記憶するスイッチ制御パタン記憶部11と、外部から入力されるスイッチ制御パタン選択信号に応じて複数のスイッチ制御パタンのうち1つのスイッチ制御パタンを選択してスイッチSW−1〜SW−Nに出力するスイッチ制御パタン選択回路12とから構成される。

(もっと読む)

電流変動制御装置、半導体集積回路、電流変動制御方法および電流変動制御プログラム

【課題】面積を小さくでき、かつ、消費電流の変化を抑制して安定した動作を行う半導体集積回路の全体消費電流を制御する電流変動制御装置を提供する。

【解決手段】電流変動制御装置は、本来的用途に応じて設けられている複数の既存内部回路Bを選択的に活性化させて調整用の消費電流を生じさせる電流制御回路と、内部回路Aのリセット解除およびリセット投入を制御するリセット制御信号を出力するとともに電流制御回路に動作許可を与える動作許可信号を出力するリセット制御回路と、を備える。電流制御回路は、既存内部回路Bに活性化制御信号を出力し、内部回路Aのリセット解除前に既存内部回路Bを順次選択して活性化させることによりこれら既存内部回路Bによる調整用消費電流を徐々に上昇させ、内部回路Aのリセット解除時に既存内部回路Bの活性化を停止させる。

(もっと読む)

接続状態診断装置

【課題】電源投入を契機として、コネクタインタフェースの接続状態の全てを自律的に診断可能にする。

【解決手段】コネクタインタフェースCIFを診断対象とする接続状態診断装置は、第1の基盤1への電源投入を契機として、複数の第1の運用信号線1A−1Dのそれぞれに診断電位信号を自律的に出力する手段13と、コネクタインタフェースを通して複数の第2の運用信号線2A−2Dにそれぞれ伝送される診断電位信号を全て受信したときは、コネクタインタフェースの正常接続状態を示す第1の状態監視信号を出力する手段20と、第1の状態監視信号が受信されたときは、複数の第1の運用信号線への診断電位信号の出力を停止制御して、自律的に診断モードから運用モードに切替設定し、異常接続状態を示す第2の状態監視信号が受信されたときは、複数の第1の運用信号線への診断電位信号の出力を維持制御する手段14とを備える。

(もっと読む)

半導体集積回路及びそのデータ出力方法

【課題】本発明は、回路構成を簡素化することで、外部リード命令によって迅速なデータの出力が可能である半導体集積回路及びそのデータ出力方法を提供する。

【解決手段】本発明は、内部クロックによってリード命令をラッチし、コアストロボ信号を生成するように構成されるストロボ信号生成部;メモリセルに格納されたデータをコアストロボ信号に応じて出力するように構成されるコアブロック;コアブロックから出力されたデータを複数の制御信号によってラッチし、ラッチされたデータを所定の順序に従って出力するように構成されるデータ出力部;及び、コアストロボ信号及び内部クロックを用いて、複数の制御信号を生成するように構成される制御部を備えることを特徴とする。

(もっと読む)

半導体集積回路装置および消費電力制御方法

【課題】追加回路を最小限に抑えた設計で消費電力を効果的に削減する消費電力制御を行う半導体集積回路装置を提供する。

【解決手段】バスマスタ3、4は、バスアクセス要求を発行して、かつアクセス許可がない場合は、クロックゲーティング回路6にクロック遮断要求を発行し、バスアービタ2は、バスアクセス許可を発行したとき、該バスアクセス許可の発行先のバスマスタに関するクロック遮断解除要求をクロックゲーティング回路に発行し、クロックゲーティング回路6は、クロック遮断要求を発行したバスマスタへのクロック供給を遮断し、クロック供給が遮断されたバスマスタに関するクロック遮断解除要求が発行されたとき該バスマスタへのクロック供給の遮断を解除する。

(もっと読む)

スイッチ装置

【課題】スイッチと判定部とを接続する電線の削減、並びに小型化及び軽量化が可能なスイッチ装置の提供。

【解決手段】複数のスイッチの各接点SW1,SW2,・・・SWnに信号を与えて、スイッチのそれぞれのオン/オフ状態を検出するスイッチ装置。各接点SW1,SW2,・・・SWnは並列に接続されており、各接点に同一の信号を与える信号出力部2と、各接点SW1,SW2,・・・SWn及び固定電位部間に接続された互いに異なるインピーダンス回路Y1,Y2,・・・Ynと、信号出力部2が与えた信号を検出する信号検出部1と、信号検出部1が検出した信号に基づき、スイッチのそれぞれのオン/オフ状態を検出する状態検出部3とを備えている。

(もっと読む)

パワー半導体の駆動回路装置およびそれに用いる信号伝達回路装置

【課題】制御出力信号が制御入力信号を忠実に復元しているか否かを検出、監視する自己診断機能を備えたパワー半導体の駆動回路装置および信号伝達回路装置を提供する。

【課題を解決するための手段】

パワー半導体の駆動回路装置30は、制御入力信号Sinを生成する電子制御装置32と、主経路34と自己診断機能38を有する信号伝達回路装置300と、信号伝達回路装置300からの制御出力信号Soutで駆動されるパワー半導体40とを備える。自己診断機能38は帰還パルス送信回路360、第2信号伝達回路370および第2受信回路380を有する。第2受信回路380では制御出力信号Soutが制御入力信号Sinに一致しているか、または不一致であるかを比較し、比較した結果を比較信号出力端子390に出力する。比較信号出力端子390に出力された信号は電子制御装置32に伝達される。

(もっと読む)

信号処理装置および信号処理方法

【課題】 相互に異なる周期のクロック信号が与えられ、かつ相互に非同期で所定の処理を行う複数の処理部のリセットを、簡単な構成で、確実に行うことができる信号処理装置および信号処理方法を提供する。

【解決手段】 モジュール回路部14は、モジュールA,B,Cのうちのいずれかに対するリセット指令が与えられると、指令されたモジュールを指定する信号を含み、かつCPUCLKの1周期分の長さを有する1shotリセット信号を生成する。同期リセット生成回路部15は、1shotリセット信号が与えられ、この1shotリセット信号の長さを指令されたモジュールに対応する長さに引き延ばした伸長リセット信号を生成し、生成した伸長リセット信号を指令されたモジュールのクロックに同期させて同期リセット信号を生成し、指定されたモジュールでは、同期リセット信号が与えられた状態で、クロック信号が立上がりまたは立下ると、リセットされる。

(もっと読む)

電子機器、及び電子機器における切換制御方法

【課題】複数種のどの周波数でも最適化された状態で信号を伝送することを可能した電子機器、及び電子機器における切換制御方法を提供する。

【解決手段】本願は、複数の電子部品と、前記電子部品に接続され信号が伝送される伝送線路と、前記伝送線路においてインピーダンスマッチングを行うためのマッチング回路と、前記伝送線路のインピーダンスが、何れかの前記電子部品に入力される信号の周波数に応じた値になるように、前記マッチング回路の回路構成を切り換える制御を行う切換制御手段と、を備える。

(もっと読む)

41 - 60 / 187

[ Back to top ]