Fターム[5J055DX01]の内容

Fターム[5J055DX01]に分類される特許

141 - 160 / 187

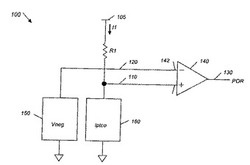

温度係数が小さいパワー・オン・リセットを生成する方法及び装置

【課題】実質的に温度変化に無関係なパワー・オン・リセット信号を生成する方法及び装置を提供すること。

【解決手段】リセット回路は、電圧生成器、第1の抵抗素子、電流生成器及びコンパレータを備える。電圧生成器は負の温度係数を有する第1の電圧信号を生成する。第1の抵抗素子は供給電圧と第2の電圧信号との間に結合される。電流生成器は第2の電圧信号に結合され、且つ、オフセット電流と正の温度係数を有する基準電流とをシンクするように構成される。コンパレータは、第1の電圧信号と第2の電圧信号とを比較してリセット信号を生成するように構成される。本発明は更に、パワー・オン・リセット信号を生成する方法又は装置を含む半導体デバイス、半導体ウェーハ及び電子システムを含む。

(もっと読む)

クロック切り換え回路

【課題】

複数のクロックソースから1本のクロックを時分割に選択して対象の機能ブロックに供給する従来のクロック選択回路では、クロックの切り換え時やリセット信号およびリセット信号に同期している動作クロックを供給するためにクロック選択回路のリセットのタイミング等をLSI設計のたびに考慮するのは非常に効率が悪く、また不具合作りこみの原因となる。

【解決手段】

LSIがどのようなモードにおいても常に入力されている常時入力クロックを入力し、機能ブロックにリセットをかけている間は、クロック選択回路が選択した出力クロックに代えて、入力された常時入力クロックを出力クロックとして出力するリセット制御信号回路をクロック切り換え回路に追加することにより、リセット入力時はクロック選択回路の動作に依存することなく常時入力クロックを機能ブロックへ供給する。

(もっと読む)

プログラマブルロジックデバイス集積回路上の高速シリアルデータレシーバ用のデシリアライザ回路網

【課題】多数の異なるプロトコルに対して、および広範囲のデーターレートに対して、シリアル形式のデータをパラレル形式のデータに変換することが可能な、デシリアライザ回路網を提供する。

【解決手段】プログラマブルロジックデバイス(「PLD」)などの高速シリアルデータレシーバ回路網用のデシリアライザ回路網(10)は、シリアルデータを任意の複数のデータ幅を有するパラレルデータに変換するための回路網を含む。該回路網(10)はまた、広範囲の周波数の中の任意の周波数で動作可能である。該回路網(10)は様々な観点において構成可能/再構成可能であり、その構成/再構成の少なくとも1部分はダイナミックに(すなわち、PLDのユーザーモードオペレ−ションの間に)制御され得る。

(もっと読む)

マトリックス表示装置のノイズ除去回路およびこれを用いたマトリックス表示装置

【課題】 液晶表示装置のノイズ除去回路に関し、特に、液晶表示装置に入力される表示制御信号に重畳されたノイズを除去する回路を提供する。

【解決手段】 ノイズを除去する信号の立上り検出回路部21と規定期間カウントするカウンタ27と、該カウンタの初期化信号を作成する初期化回路部25と、カウンタ27のカウント許可信号を作成するカウントイネーブル回路部26と、カウンタ27が初期状態であるかを検知する初期状態検出回路部24を内蔵しており、立上り検出回路部21の立上り検出によって、カウンタ27が初期値からカウントを開始して、前記規定期間分のカウントを終了後、前カウンタ27を再び初期化するよう構成し、初期状態検出回路部24の初期状態検出信号をノイズが除去された信号とする。

(もっと読む)

リセット回路及びそのリセット回路の動作方法

【課題】電源電圧がCPUの動作電圧を下回っている場合に、外部からのスタンバイモード解除信号を受け付けないようにするマイクロコンピュータを提供する。

【解決手段】電源電圧の状態を示す信号を出力する電圧検出部2と、複数の動作モードで動作するデータ出力回路3とを具備するリセット回路1を構成する。複数の動作モードは、電源電圧が第1閾値電圧以上の電圧であることを示す通常モードと、電源電圧が第1閾値電圧から第2閾値電圧の範囲であることを示すデータ保持モードと、電源電圧が前記第2閾値電圧以下であることを示すデータ消去モードとを含む。データ出力回路2は、データ保持モードからデータ消去モードへの遷移に応答して、保持している前記データをリセットし、データ消去モードへ移行せずに前記データ保持モードから前記通常モードへ遷移するときに、保持されていた前記データを出力する。

(もっと読む)

電子回路および信号供給方法

【課題】 ホストデバイスとスレーブデバイスとを備えた電子回路において、スレーブデバイスに供給する信号波形に生じる欠陥を軽減する。

【解決手段】 フレキシブル配線13を介してスレーブデバイス40に供給する信号に基づいてハイレベルまたはローレベルの信号を出力する出力バッファ22aと、スレーブデバイス30に供給する信号に基づいてハイレベルまたはローレベルの信号を出力する出力バッファ22bと、出力バッファ22a,23aのドライブ能力をそれぞれ設定するバッファ設定部23a,23bと、バッファ設定部23a,23bによる上記ドライブ能力の設定を制御するホストCPU21とを備える。ホストCPU21は、各スレーブデバイスへの供給信号に波形鈍り,オーバーシュート,アンダーシュート等の欠陥が生じることを防止または軽減するように各出力バッファ22a,22bのドライブ能力を制御する。

(もっと読む)

表示駆動回路

【課題】 ブランク制御機能を有する表示駆動回路のピーク電流を抑制する。

【解決手段】 表示データD1〜Dnは、データラッチ11にラッチされ、ブランク信号/BLKでゲート制御されるANDゲート121〜12nに与えられる。ANDゲート121〜12nの出力信号は、それぞれ異なる遅延時間τ1〜τnを有する遅延回路131〜13nで遅延された後、ドライバ141〜14nに与えられ、駆動信号Q1〜Qnとして表示器に供給される。各ドライバ141〜14nに与えられる信号S1〜Snの変化のタイミングは、遅延回路131〜13nによって分散されるので、これらのドライバ141〜14nに流れる電流i1〜inのタイミングも分散され、電流i1〜inの総和Σiは、なだらかな時間的変化を示し、ピーク電流値は減少する。

(もっと読む)

可動素子、ならびにその可動素子を内蔵する半導体デバイス、モジュールおよび電子機器

【課題】パッケージサイズの縮小化を妨げることがなく、しかも低電圧・低消費電力系の素子と一体的に形成することが可能な程度に低電圧・低消費電力の可動素子、ならびにその可動素子を内蔵する半導体デバイス、モジュールおよび電子機器を提供する。

【解決手段】半導体基板10上に、信号を伝送するための信号線路11と、信号線路を機械的に継断するための継断部12と、継断部12を切り替えるための切替部13と、継断部12の切り替え後の状態を保持するための保持部14とを備える。継断部12および保持部14は互いに対向配置された一組の固定子12A,14Aおよび可動子12B,14Bを、切替部13は保持部14の可動子14Bと対向配置された可動子13Bをそれぞれ有する。切替部13の可動子13Bおよび保持部14の可動子14Bの少なくとも一方が、弾性部15を介して継断部12の可動子12Bと接続されている。

(もっと読む)

車両の電子制御装置

【課題】 複数の系統(グループ)に区分された複数のECUから構成される車両の電子制御装置において、グループごとに設けられたリレーの異常を簡易な構成で検出する。

【解決手段】 複数の電子制御ユニット(ECU)1A〜1C,2A〜2Cは、複数のECUグループ10A,10Bに区分される。リレーRL1,RL2は、ECUグループごとに設けられ、対応のグループにおいて各ECUと電源30との間に接続される。各ECU間は、通信ネットワーク60に接続され、電源投入時には、通信機能に異常が発生しない限り、自身が通信可能であることを示すフラグを出力する。リレー異常検出部70は、それぞれのECUについて通信可能または通信不能を示す通信状態情報に基づき、ECUグループ間で通信状態情報が不一致であるときにリレーRL1,RL2の異常を検知する。

(もっと読む)

共通電源を用いた2経路増幅回路

【課題】 共通電源5を使用し、高周波信号と直流電力とを有効に分離可能にして、端末の小型化や軽量化を図った共通電源を用いた2経路増幅回路を提供する。

【解決手段】 DCSの高周波信号を増幅する第1電力増幅回路2と、GSMの高周波信号を増幅する第2電力増幅回路4と、共通電源5を備え、第1電力増幅回路2の出力と共通電源5間に第1の電源供給用ストリップライン6を接続すると共に、第1電力増幅回路2の出力と第2電力増幅回路4の出力間に第2の電源供給用ストリップライン7を接続し、第1及び第2の電源供給用ストリップライン6、7の信号ライン長をそれぞれDCSの高周波信号波長の1/4に選定し、第1の電源供給用ストリップライン6に第2の電源供給用ストリップライン7を合わせた信号ライン長をGSMの高周波信号波長の1/4に選定した。

(もっと読む)

同期回路

【課題】 リセット端子を持たない1:nDEMUXやn:1MUXの複数個を同期させて並列動作させることが可能な同期回路を実現する。

【解決手段】 クロック信号を入力して作動する複数のカウンタIC手段の動作タイミングを一致させる同期回路において、前記複数のカウンタIC手段のうち、基準となるカウンタIC手段のクロック信号と同期対象となる他のカウンタIC手段のクロック信号との位相差を検出する位相差検出手段と、検出された前記位相差に基づいて前記他のカウンタIC手段のクロック信号の位相を制御する位相制御手段と、を備える。

(もっと読む)

半導体論理装置およびこれを備える電子機器

【課題】 消費電力が少なく、転送されるデータを漏れなく正確に取得できる半導体論理装置を提供することを目的とする。

【解決手段】 データ入力保持部2に入力されるデータは、カウンタ13のカウント値に応じて指定されるアドレスに保持される。一方、データ出力部3より出力されるデータは、カウンタ21のカウント値に応じて指定されるアドレスより読み出される。カウンタ13は、データイネーブル信号の立ち上がりとともにリセット処理が施され、カウンタ21はデータイネーブル信号が遅延回路4によって所定時間遅延された信号の立ち上がりとともにリセット処理が施される。遅延回路4によって遅延処理が施されるため、読出し指示が与えられる時点では、入力されたデータがすでに確定しており、これによってデータを正しく転送することが可能となる。

(もっと読む)

非同期デジタル回路用スリープ・ウォッチドッグ回路

本発明の非同期回路用スリープウォッチドッグ回路は、クロック手段、多数のトリガ入力機能有するカウント手段、およびデジタル供給手段を備える。回路が通常モードにある場合は、周期的なリセットまたはウォッチドッグカウンタをリセットするアクティビティ信号が存在する。その結果、クロック手段が動作し続け、デジタル供給手段が“通常”モードで駆動する。回路が“スリープ/スタンバイ”状態に入った場合は、“アクティビティ”信号が非アクティブとなり、カウンタが終了する前にウェイクアップイベントが発生しなかった場合は、クロック手段が停止され、デジタル供給手段が低電力モードへと変化する。  (もっと読む)

(もっと読む)

クロック制御回路

【課題】 周波数とタイミングの切り替えが容易で、動作ノイズの少ないクロック信号を選択することができるクロック制御回路を提供する。

【解決手段】 マスタクロック信号CLKをその立下がりのタイミングで分周して分周クロック信号DCKを生成する分周部(21〜24)と、マスタクロック信号CLKの立上がりのタイミングでn逓倍し、n番目のクロックパルスを間引いて逓倍クロック信号MC1を生成する逓倍部(25〜29)と、逓倍クロック信号MC1から派生された各種のタイミングの逓倍クロック信号、または分周クロック信号DCKの内から、選択信号SL1〜SL3に従ってバスクロック信号BCKを選択し、プロセッサ11等に供給する選択部(30〜35)を設ける。

(もっと読む)

メモリ制御装置

【課題】 メモリ制御装置が実装されるべきICチップの面積の減少を図る。

【解決手段】 ダブルデータレート同期式ダイナミックランダムアクセスメモリ(DDR−SDRAM)の動作クロックx1Clkの周波数より高い周波数をもつクロック信号x4Clkを用いて、ストローブ信号エッジ検出部1303が、データストローブ信号Dqsをサンプリングして、データストローブ信号Dqsの切り替わりエッジを検出し、エッジ切り替わり検出信号を出力する。データサンプリング部1302は、エッジ切り替わり検出信号を用いて、データ信号Dqから、該データ信号Dqに含まれる2系統のデータ信号を抽出する。

(もっと読む)

多重周波数同期クロック信号発生器

装置(例えば、半導体の記憶装置)に配置されるデバイス動作を同期するために、複数の同期信号を生成するための装置(図2)および方法。該装置は、対応する複数の入力クロック信号(CLK)に依存する複数の同期信号(CLKSYNC)を生成し、および同期クロック信号(CLK DEL)として提供されるように該同期信号のうち1つを選択し得る。もしくは、該装置は、入力クロック信号(CLK)に依存する複数の内部クロック信号(CLK1、CLK2)を生成し、および複数の内部クロック信号から、対応する複数の同期信号を生成し得る。同期信号のうち1つが、該装置によって同期クロック信号として選択される。もしくは、該装置は、クロック信号を受け取り、ここから同期クロック信号を生成し、および該同期クロック信号の周期の数(該数は、該装置に提供される選択信号に依存する)に応答して、同期パルスを得る。  (もっと読む)

(もっと読む)

半導体集積装置

【課題】内部の機能切替における必要なクロックの切替にかかる煩雑さを解消し、外部から内部の機能切替の命令のみで精密なクロック設定を実現する半導体集積装置を提供する。

【解決手段】外部から入力される内部機能の切替の命令100の内容を判別し、特定の機能ブロック118に対して必要なクロックの周波数を判別するクロック周波数判定回路114と、切り替え前後の周波数の関係により、機能切り替えとクロック切り替えのタイミングを制御し、切り替えの状態を表す機能切替・クロック切替完了フラグ110を外部に出力するクロック切替制御回路113とを備えることにより、クロック切り替えの制御を外部から行う必要がなくなるようにした。

(もっと読む)

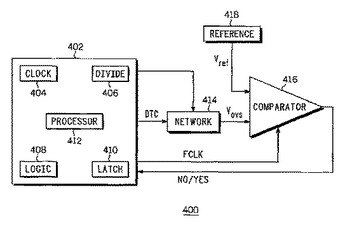

デジタル時定数トラッキング技術及び装置

プロセス、電圧及び温度の変動に起因して回路網(414)の時定数偏差を調整して雑音を無くす方法及び装置を提供する。当該装置(400)は、デジタル時定数が回路網(414)の公称時定数に対して相関されるクロック基準手段(404)を備える。相関されたデジタル時定数は、回路網(414)に印加され、そして出力充電/放電波形スイングが、所定の基準電圧と比較される。当該充電/放電波形スイングが基準電圧と一致しない場合、オフセット信号を発生する。オフセット信号が、制御回路(402)に印加され、当該制御回路(402)は、対応の同調信号を発生する。同調信号は、回路網(414)に印加されて、一致が達成されるまで内部部品を増分的又は減分的に調整する。当該装置(400)は、内蔵型で自己試験型のデジタル時定数トラッキング回路として構成されることでき、且つICチップ上に回路網(414)と一緒に統合化されることができる。  (もっと読む)

(もっと読む)

ゼロクロス検出回路

【課題】

商用電源の交流電圧に対する重畳ノイズ及び波形歪みに対して、ゼロクロスを定周期にかつ安定に検出することができるゼロクロス検出回路を実現する。

【解決手段】

交流電圧がゼロ電位をクロスするタイミングに同期したパルス信号を生成するゼロクロス検出回路において、前記交流電圧の正の半サイクル又は負の半サイクルの少なくともいずれかに同期した矩形波信号を生成する矩形波変換手段と、前記矩形波信号によりトリガされるモノステイブルマルチバイブレータ手段とを備える。

(もっと読む)

配線中継装置

【課題】 信号を中継する外部接続先の増大に対応できる、拡張性の高い配線中継装置を提供する。

【解決手段】 2入力端子と2出力端子とを有するブロック複数個を1列とし、これを多数列組み合せて、配線の中継をする配線中継装置であって、各列のブロックは、1つのブロックの2つの出力端子のそれぞれが、後列の2つのブロックの一方の入力端子と接続される状態で組み合わされ、いずれのブロックとも、内部に各入力端子を何れの出力端子とも接続することが出来る配線網と、外部からの指示に従ってその配線網に所望の端子間の配線路を有効にさせる選択部とを備える。

(もっと読む)

141 - 160 / 187

[ Back to top ]