Fターム[5J055DX01]の内容

Fターム[5J055DX01]に分類される特許

61 - 80 / 187

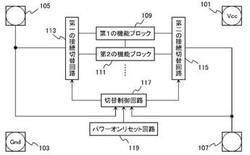

水晶発振器

【課題】確実に端子機能の切替えが可能であり、かつ、ノイズによる誤動作のない水晶発振器を提供すること。

【解決手段】機能ブロック(109、111)のそれぞれが、第1の接続切替回路113を介して第1の端子105に接続され、第2の接続切替回路115を介して第2の端子107に接続されている。そして、第1の端子105に接続される機能ブロックを切り替えるための信号および第2の端子107に接続される機能ブロックを切り替えるための信号が、これら第1および前記第2の端子に同時に入力される信号によって生成される。本発明の水晶発振器では、切替えの対象である複数の端子自身への信号の同時入力が端子機能切替のための信号生成になっているため、端子機能の切替えに際して電源端子の電圧を端子機能切替の判定に使用する必要がなくなり、1つの電源電圧を切替えの判定に使うことによる動作の不安定性を解消することができる。

(もっと読む)

スイッチ制御装置、開閉器及びスイッチ制御方法

【課題】スイッチを閉じた場合に、電源から負荷装置に突入電流が流れ込んで、スイッチに大きな負荷がかかることを防ぐことができるスイッチ制御装置、開閉器及びスイッチ制御方法を提供する。

【解決手段】電源と負荷装置との間に接続されるスイッチ21を制御するスイッチ制御装置22であって、スイッチ21の閉命令を取得する開閉命令取得部221と、開閉命令取得部21が閉命令を取得した場合にスイッチ21を閉時間だけ閉じる第1の処理と、スイッチ21を開時間だけ開く第2の処理とを交互に行なう制御部225とを備え、閉命令を取得後の通電開始時にスイッチ21の開閉を繰り返すことによってスイッチ21に流れる突入電流を抑制する。

(もっと読む)

半導体装置

【課題】半導体装置において、ユーザボードの違いや製造ばらつきがあっても、電源共振ノイズによる問題を回避することができる技術を提供する。

【解決手段】半導体装置内の電源ノイズを観測する電源ノイズ観測回路1と、電源ノイズ観測回路1の出力に基づいて、生成クロック301の周波数が変化するクロック生成回路2と、生成クロック301が入力される演算回路ブロック3と、を備える。そして、前記電源ノイズ観測回路1によって観測される電源ノイズが低減するように、生成クロック301の周波数が調整される。

(もっと読む)

ラダー抵抗回路、基準電圧生成回路、ドライバ、電気光学装置及び電子機器

【課題】高精度な抵抗分割を小規模な回路面積で実現できるラダー抵抗回路、基準電圧生成回路、ドライバ、電気光学装置及び電子機器を提供すること。

【解決手段】ラダー抵抗回路は、複数の抵抗ユニットRA1〜RAmn(m、nは2以上の整数)と複数の選択ユニットSLA1〜SLAmnを含む。直列に接続された抵抗ユニットRA1〜RAnは方向D1に沿って配置され、方向D1の反対方向を方向D3とする場合に、直列に接続された抵抗ユニットRAn+1〜RA2nは方向D3に沿って配置される。方向D1に直交する方向を方向D2とする場合に、抵抗ユニットRAn+1は抵抗ユニットRAnの方向D2に配置される。選択ユニットSLAiは、抵抗ユニットRAiの方向D2に配置され、抵抗ユニットRAiに対応するタップに接続される。

(もっと読む)

クロック発振回路

【課題】簡単な回路構成でスペクトラム拡散を行うことが可能なクロック発振回路を提供する。

【解決手段】基本クロック信号を発振する基本クロック発振器と、基本クロック信号と非同期で、かつ基本クロック信号より短い周期としたクロック調整信号を発振する調整クロック発振器と、基本クロック信号をクロック調整信号の1周期分シフトして、クロックシフト信号として出力するシフト回路23cと、基本クロック信号およびクロックシフト信号を1周期ごとに切り替えて、調整クロック信号として出力する切替回路として機能するカウンタ回路23aおよびセレクタ回路23bとを備えている。シフト回路23cは、基本クロック信号をクロック調整信号の立ち上がりで同期する第2フリップフロップ23c1で形成され、カウンタ回路23aは、基本クロック信号を2分周する第1フリップフロップ23a1および第1インバータ23a2で形成されている。

(もっと読む)

多値出力回路及びこれを用いた液晶駆動装置

【課題】本発明は、小規模な回路構成でありながら、設定電圧の増加や変更にも柔軟に対応することが可能な多値出力回路を提供することを目的とする。

【解決手段】本発明に係る多値出力回路は、デジタル信号(電圧設定信号SET)からアナログ電圧Va〜Vdを生成するデジタル/アナログ変換部3と;電圧選択信号A1に基づいて、アナログ電圧Va〜Vdのいずれか一を選択的に出力する電圧選択部41〜4nと;電圧選択部41〜4nの出力電圧を液晶パネル7に供給するバッファ51〜5nと;を有して成る構成とされている。

(もっと読む)

半導体集積回路装置及び半導体集積回路装置の試験方法

【課題】配線領域の増大を抑制しつつも、電源遮断回路が正常に機能しているかを試験することのできる半導体集積回路装置を提供する。

【解決手段】内部回路10と電源遮断回路20との間のノードAの仮想電源電圧VD1を比較電圧Vnに変換する電圧シフト回路40と、電源遮断回路20の電源通電動作時に高電位基準電圧を生成し、電源遮断動作時に低電位基準電圧を生成する基準電圧生成回路50が備えられる。また、電圧シフト回路40からの比較電圧Vnと、基準電圧生成回路50からの基準電圧VRとを比較して判定信号JSを生成し、その判定信号JSを出力パッド75に出力する電圧比較回路60が備えられる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置のクロック制御方法

【課題】消費電力削減の効果を発揮すること。

【解決手段】パイプライン接続された複数の演算装置4と、データ通知信号が入力されると処理制御信号を生成し出力する処理制御装置2と、処理制御信号が入力されるとクロック制御信号を生成し出力するクロック制御信号生成装置3と、を備え、演算装置4は、クロック制御信号が入力されると、クロック制御信号に基づいて、演算装置を動作させるゲーテッドクロック信号を生成し出力するクロックゲーティング回路5と、ゲーテッドクロック信号に同期して動作し、データおよび処理制御信号が入力されると、データに対して処理制御信号が指示する処理を行い、処理後のデータおよび処理制御信号を後段に接続された演算装置4へ出力する演算ブロック6と、クロック制御信号が入力されると、クロック制御信号を処理後のデータおよび処理制御信号と同期するように、演算ブロック6での処理時間分遅延して、後段に接続された演算装置4へ出力する遅延回路7と、を備える。

(もっと読む)

データ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラム

【課題】過渡遷移に基づく解析を困難とし、例えばDPA攻撃に対する耐性の高い演算構成を実現する。

【解決手段】非線形変換処理などのデータ変換処理を行う演算装置において、論理回路を構成するセレクタ入力値をすべて同一値に維持したプリチャージ・フェーズにおいて入力ビット遷移処理を実行させ、遷移処理終了後にエバリュエーション・フェーズへ移行してデータ変換処理に基づく出力ビット生成を行なう。プリチャージ・フェーズにおいては全てのセレクタ入力値を同一値とするリセットを実行するので、入力ビット遷移処理時の過渡遷移に基づく解析が困難となり、例えばDPA(Differential Power Analysis)攻撃に対する耐性の高い演算装置が実現される。

(もっと読む)

パワーオンリセット回路

【課題】 チップ面積の増大防止及び基板上の部品点数の増加防止の両方を図り、クロック信号に同期したパワーオンリセット信号を生成する。

【解決手段】 電源電圧印加により動作するフリップフロップ回路を複数段備え、初段のフリップフロップ回路のデータ入力端子Dが外部電源端子VDDまたは外部リセット端子RSTに、他のフリップフロップ回路のデータ出力端子Qが、夫々後段のフリップフロップ回路のデータ入力端子Dに接続され、クロック信号CLKの入力によりシフト動作するフリップフロップ回路群と、電源電圧印加により動作し、初段のフリップフロップ回路の出力信号Q1と最終段のフリップフロップ回路の出力信号Qnの排他的否定論理和を演算する排他的否定論理和回路21を備えるリセット信号生成回路20と、を備えてなる。

(もっと読む)

音声出力切替装置

【課題】BGM等を流している店舗等でも、店舗内の人に緊急地震速報を確実に伝えることができ、且つ店舗内にいる人を慌てさせることなく、適当な対応を取らせることができる音声出力切替装置を提供する。

【解決手段】音声出力切替装置1は、通常時、外部入力部6に入力されている音声信号を、音声出力部8から出力する。また、音声出力切替装置1は、チューナ部3で緊急地震速報を受信すると、音声出力部8から出力する音声信号を、チューナ部3で受信しているラジオ放送に切り替える。また、音声出力切替装置1は、操作部9のリセットボタンが操作されたとき、外部入力部6に入力されている音声信号を、音声出力部8から出力する。

(もっと読む)

電気的に制御される磁気回路を備えた装置の駆動回路

【課題】

部品の着脱作業を要することなく、簡単に、発振器等磁気回路を備えた装置単体での、周波数特性の検査を可能とした電気的に制御される磁気回路を備えた装置の駆動回路を提供する。

【解決手段】

信号レベル調整部14と積分回路部15とを具備する電気的に制御される磁気回路を備えた装置の駆動回路であって、前記積分回路部がOPアンプ23と、該OPアンプに対して並列に接続されたコンデンサ27と、並列に接続された負帰還用の抵抗28と、該抵抗を前記OPアンプに対して継断するスイッチング手段33,32とを有し、該スイッチング手段が前記抵抗を断状態とすることで、前記積分回路部が積分回路として動作し、前記スイッチング手段が前記抵抗を継状態とすることで、前記積分回路部が増幅回路として動作する様構成した。

(もっと読む)

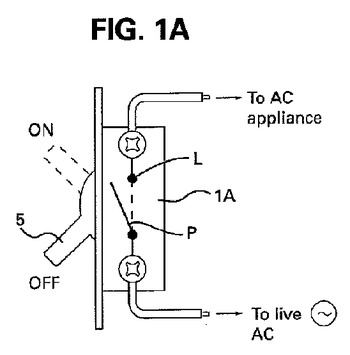

ビデオインターホンまたはショッピング端末からAC電源方式の器具を遠隔操作するための方法および装置

手動で作動する電気SPDTスイッチに接続されたAC器具の電源回路に遠隔操作SPDTリレーを追加して接続するための方法であって、前記AC器具はホームオートメーションネットワーク内に組み込まれ、それぞれの前記リレーおよび前記SPDTスイッチは極端子と二重トラベラ端子とを備え、前記リレーは標準電源ボックス内への取り付けに適合するACスイッチに類似した形状およびサイズを有する、方法を提供する。  (もっと読む)

(もっと読む)

クロックトランスファ機能を有するクロック回路及び方法

装置(10)は、移行元クロックと移行先クロックと移行クロックとから選択した出力クロックを出力するマルチプレクサ(20)を含む。さらに、移行元クロックと移行先クロックとの間の位相差を計算する位相差計算モジュール(22)と、複数のクロックを生成するように構成されたクロック生成モジュール(12)とを含む。さらに、複数のクロックのうち1つのクロックを移行トラックとして選択するクロック選択モジュール(14)と、(1)移行元クロックと移行先クロックとの間の位相差に基づき、複数のクロックのうちの1つのクロックを移行クロックとして選択する信号をクロック選択モジュールに出力し、(2)移行元クロックと移行先クロックと移行クロックとのうち1つのクロックを出力クロックとして出力する信号をマルチプレクサに出力する制御回路(16)とを含む。

(もっと読む)

(もっと読む)

クロック制御回路およびそれを搭載した半導体集積装置

【課題】ダブルエッジトリガ型フリップフロップ回路に対するクロック信号の供給を停止させるとき、当該フリップフロップ回路が保持するデータが不必要に更新されてしまうことがある。

【解決手段】エッジ検出回路61は、第1クロック信号を受け、そのエッジを検出すると、所定幅のパルス信号を出力する。論理ゲートは、エッジ検出回路61の出力信号と、ダブルエッジトリガ型フリップフロップ回路の使用状態を示すイネーブル信号とを受け、イネーブル信号が有意な期間、エッジ検出回路61の出力信号に追従する信号を出力し、イネーブル信号が非有意な期間、非有意なレベルの信号を出力する。トグル型フリップフロップ回路は、論理ゲートの出力信号を受け、所定幅のパルス信号を検出するたびに、論理レベルが反転する信号を、第2クロック信号として出力する。

(もっと読む)

スキュー調整回路

【課題】リセット動作時に大きな雑音を発生する可変遅延回路を用いたスキュー調整回路において、他の可変遅延回路のリセット動作時の雑音干渉による遅延時間の変動を防ぎ、高集積、低消費電力、高分解能、高精度なスキュー調整回路を実現すること。

【解決手段】リセット動作時に大きな雑音を発生する可変遅延回路を用いたスキュー調整回路において、全ての可変遅延回路の遅延発生動作が終了してから全ての可変遅延回路のリセット動作を行うことを特徴とするもの。

(もっと読む)

電気集塵機

【課題】集塵負荷1に印加する印加電圧する電圧を制御器で調整することで、スパーク頻度を少なくする方法において、スパークの頻度を減らすことはできるが、完全にはスパークを防止することが難しく、スパークが避けられない、という課題があった。

【解決手段】集塵負荷1に印加する電圧をベース電圧とパルス電圧に区分し、印加する電力を調整して予め設定した電力値以上の電力を印加しないようにすることで、スパークの発生を防止した電気集塵機が得られる。

(もっと読む)

遅延回路を用いるクロックのない直列化

各直列ビットについてレジスタ及び遅延回路を組み込んだ直列変換器が記述される。直列変換器は、データビットとタイミング信号のタイミングがぴったりと一致するように、タイミング信号を生成してデータビットの出力と同時に出力する。クロックは使用されない。これによって、並列変換器/受信器はデータビットを確実に受信することが可能になる。例示した各々の遅延回路は、次のレジスタ/遅延回路を作動させて、次の一連のビット及びそのタイミング信号を出力するように構成される。 (もっと読む)

PLLシンセサイザー回路

【課題】 電源変動等が生じると、外部からの割込信号により不定期間を待って再度分周データをPLLシンセサイザーICに書き込むことで、安定的にロック状態に復帰させることができるPLLシンセサイザー回路を提供する。

【解決手段】 PLLシンセサイザーIC106の電源投入時又は電源変動時にマイクロプロセッサ(CPU)104への割込を監視手段が発生させ、CPU104はPLLシンセサイザーIC106の電源投入後又は電源変動後の不定期間に相当する期間を待って、分周データをPLLシンセサイザーIC106に出力して書き込みを行い、更に分周データ出力後にロック状態となるまでの期間ウエイトするPLLシンセサイザー回路である。

(もっと読む)

クロック供給回路及びクロック供給方法

【課題】クロック信号のシームレスな切り替えが可能なクロック供給回路を提供する。

【解決手段】マルチプレクサ110は、供給された複数のクロック信号のうちクロック指定信号SELにより指定されたクロック信号を第1の中間クロックCLK_M1として出力する。反転回路120は、クロック反転信号INVERTに応答して、供給された第1の中間クロックCLK_M1を、そのまま、又は、信号レベルを反転させて第2の中間クロックCLK_M2として出力する。Dフリップフロップ130、131は、停止信号STOPを第2の中間クロックCLK_M2の立ち上がりエッジ及び立ち下がりエッジに同期させてマスク信号MASKを生成する。ANDゲート140は、第2の中間クロックCLK_M2とマスク信号MASKとから出力クロックCLK_Oを生成し、出力する。

(もっと読む)

61 - 80 / 187

[ Back to top ]