Fターム[5J056AA11]の内容

Fターム[5J056AA11]の下位に属するFターム

ECLから (6)

TTL、DTLから (1)

I2Lから (1)

MOSから (9)

MES、ショットキーFETから

その他から (3)

ECLへ (1)

TTL、DTLへ

I2Lへ

MOSへ (18)

MES、ショットキーFETへ

信号線 (3)

その他へ (1)

振幅拡大 (172)

振幅縮小 (38)

正電位の振幅→負電位の振幅 (2)

負電位の振幅→正電位の振幅

一方の電位の振幅←→正負の電位の振幅 (5)

直流レベルのシフト (74)

信号幅の変換 (3)

タイミングの調整、遅延、同期 (148)

整合 (285)

Fターム[5J056AA11]に分類される特許

201 - 220 / 246

レベル変換用半導体集積回路装置

【課題】 論理機能を有しシステムの小型化を図ることが容易なレベル変換用ICを提供する。

【解決手段】 入力信号のレベルをシフトする複数のレベルシフト回路(LS1,LS2)を有するレベル変換用半導体集積回路装置において、レベルシフトされた信号の論理をとる論理機能を設けるとともに、入力信号のレベルに対応した第1の電源電圧(Vcc1)を印加する第1の電源電圧端子(Ps1)と出力信号のレベルに対応した第2の電源電圧(Vcc2)を印加する第2の電源電圧端子(Ps2)とを設けるようにしたものである。

(もっと読む)

半導体装置

半導体装置は、第1の電位と、第1の電位より低い第2の電位と、第2の電位より低い第3の電位により駆動される半導体装置であって、第1の電位と第3の電位との間に直列に接続される第1のPchトランジスタと第1のNchトランジスタと、第1のNchトランジスタのゲート端にドレイン端が接続される第2のPchトランジスタと、第2のPchトランジスタのソース端にソース端が接続される第2のNchトランジスタを含み、第2のNchトランジスタのドレイン端及びゲート端はそれぞれ第2の電位及び第1の電位に固定されることを特徴とする。  (もっと読む)

(もっと読む)

半導体装置及びレベルシフト回路

【課題】 多ビット化でもチップサイズの増大を抑える半導体装置を提供する。

【解決手段】 電位VHと電位VLの間に生じる電圧が分圧され、入力信号D0〜DN−1に基づいて分圧により生じた複数の電位3〜9のいずれかを出力可能な高耐圧デジタル/アナログ変換器1は、複数の素子群11,13と、出力素子群15と、入力信号の電位を出力素子群15と複数の素子群11,13のそれぞれが動作するために必要な電位にレベルシフトして印加するレベルシフト部17を備え、複数の電位3〜9が電位レベル順に複数にグループ化され、複数の素子群11,13のそれぞれは各グループに対応して設けられて対応するグループの電位間の電圧が印加されて動作して入力信号に基づいて対応するグループ内の電位のいずれかを出力し、出力素子群15はVHとVLの間の電圧が印加されて動作して入力信号に基づいて複数の素子群11,13が出力可能な電位のいずれかを出力する。

(もっと読む)

半導体装置、表示装置及び電子機器

【課題】

レベルシフタや作動増幅回路などを有する半導体装置において、余計に流れる貫通電流を減らして消費電力を低減し、且つ出力波形のなまりなどを抑えることができる半導体装置を提供することを課題とする。

【解決手段】

第1のトランジスタのゲート端子を第1の入力端子、第2のトランジスタのゲート端子を第2の入力端子とし、第1のトランジスタのゲート端子を第2のトランジスタのソース端子に接続する。また、第2のトランジスタのゲート端子を第1のトランジスタのソース端子に接続する。

(もっと読む)

インターフェース回路

【課題】 レイアウト面積を小さくすることができるインターフェース回路を実現する。

【解決手段】 −1V〜6Vの外部入力端子VINには、NMOSトランジスタN1のソースが接続されており、そのドレインには、PMOSトランジスタP1のソースが接続されており、そのドレインにはインバータが接続されている。N1およびP1の各閾値電圧VTN1、VTP1をそれぞれ1V、各ゲート電圧VGN1、VGP1をそれぞれ4V、0Vに設定すると、ノードAに与えられる電圧は、−1V〜3Vの範囲に制限される。また、ノードBに与えられる電圧は、1V〜3Vの範囲に制限される。つまり、N1、P1の出力電圧の範囲を、外部入力端子VINに与えられる電圧の範囲よりも狭い範囲に抑えることができる。

(もっと読む)

半導体集積回路

【課題】バス幅が変更可能な複数の出力モードをもつ半導体集積回路において、バス幅が小さな出力モードで特別な外部出力回路を用いずに電流駆動能力を高め、高速動作を行うことを可能にする。

【解決手段】m×nビットで出力するモードとnビットで出力するモードを有し、外部に信号を出力するm×n個のIO群103を備え、m×nビットで出力するモードではセレクタ群101にm×nビットのバス幅のデータを選択させることにより、m×n個のIO群103がm×nビットのバス幅のデータを出力させ、nビットで出力するモードではセレクタ群101にnビットのバス幅のデータを多重に選択させることにより、m×n個のIO群103がnビットのバス幅のデータをビット毎に少なくとも2個のIO部に多重に出力させ、同一ビットを出力するIOを外部でショートして電流駆動能力を高める。

(もっと読む)

レベルシフタ回路

【課題】CMOSゲートのみで貫通電流を防止するレベルシフタ回路を提供する。

【解決手段】入力端子50からの入力信号Vinと遅延部21で遅延させた入力信号Vin’を、第1の電源電圧の低電位電圧VDDLが供給されるNORゲート22とANDゲート23に入力、各々出力をゲート電圧VG1とゲート電圧VG2とする。レベルシフト部10用で、第2の電源電圧の高電位電圧VDDHが供給される第2の電源電圧端子30に接続されたPMOSトランジスタ1,2のゲートとドレインを交差接続し、各々のドレインとソースが接地端子40に接続されたNMOSトランジスタ4,5のドレインとを接続する。NMOSトランジスタ4,5のゲートにはNORゲート22出力とANDゲート23出力を接続する。NMOSトランジスタ5のドレイン電圧VD2をPMOSトランジスタ3とNMOSトランジスタ6に接続し、出力信号Voutを出力端子70から出力する。

(もっと読む)

半導体装置

第1電源電圧VDD1の振幅を有する入力信号INを、第1電源電圧より高電圧の第2電源電圧VDD2で動作するPMOSトランジスタPM51のゲート端子に入力する際、PMOSトランジスタPM1乃至PM4でレベル変換を行う。該トランジスタPM1、PM3、およびPM2、PM4のソース端子は第1電源電圧および第2電源電圧に接続され、PM4のゲート端子はPM1、PM2のドレイン端子に接続される。PM2のゲート端子はPM3、PM4のドレイン端子に接続される。PM1およびPM2のゲート端子には入力信号INの反転信号および入力信号INが入力される。入力信号INにおける基準電圧VSSと第1電源電圧VDD1との間の振幅は、第1および第2電源電圧間の振幅にレベル変換されてPM1、PM2から出力され、PM51を導通制御させる。  (もっと読む)

(もっと読む)

レベルシフト回路

【課題】 レベルシフト回路において、低電圧源を電源とする信号のレベルを高電圧源の電圧レベルにシフトする場合に、低電圧源を低電圧化した場合にも、前記高電圧源の電圧に起因してトランジスタが破壊することなく、レベルシフト動作を確実に行う。

【解決手段】 相補信号入力用の2個のN型トランジスタN1、N2は、低い閾値電圧を有する低電圧側の素子で構成される。従って、低電圧源VDDを電圧源とする相補信号IN、XINが一層に低く設定される場合であっても、前記N型トランジスタN1、N2は確実に動作して、レベルシフト動作は所期通り行われる。前記相補信号入力用のN型トランジスタN1、N2のドレインは、そのかかる電圧値が、保護回路Aにより、低電圧源VDDの電圧以下(N型トランジスタN1、N2の耐圧以下)に制限される。

(もっと読む)

半導体装置

【課題】異なる電圧ドメインに属する回路間において、高速に信号を伝播することが困難であった。

【解決手段】第1のインバータ回路INV1は、電流通路の一端が接地された第1導電型の第1のトランジスタN1の電流通路の他端に第2の導電型の第2のトランジスタP1の電流通路の一端が接続され、各ゲートに接地電位より高い第1の電圧V1の一方からなる第1の信号CKIが供給される。第2導電型の第3のトランジスタP2は、第2のトランジスタP1の電流通路の他端と第1の電圧より高い第2の電圧V2が供給されるノードとの間に接続され、ゲートに第1の信号の変化から遅れて接地電位と、第2の電圧の一方からなる制御信号LSOが供給され、第1のインバータ回路INV1の出力端から接地電位と前記第2の電圧の一方からなる第2に信号CKOを出力する。

(もっと読む)

レベルシフト回路及びこれを用いた携帯無線通信装置

【課題】

異なる電源で構成されるレベルシフト回路及びこれを用いた携帯無線通信装置では、一方の電源電圧が低下した場合、他方の電源で動作する後段回路の出力電圧を固定させ、動作を安定させる。

【解決手段】

入力信号が供給され、第1の電源電圧で動作し、入力信号に応じた第1の出力信号を出力する入力回路(16)と、入力信号と第1の出力信号の差を増幅して第2の出力信号を出力する増幅器14,15と、増幅器からの第2の出力信号のレベルに応じてラッチされた第3の出力信号を出力する第2の電源電圧で駆動されるラッチ回路17と、第2の電源電圧が供給され、第1の電源電圧に応じて出力電圧をラッチ回路の出力に供給するレベル設定回路18とを有し、第1の電源電圧が第2の電源電圧より低下した時にレベル設定回路を動作させて出力電圧を固定し、貫通電流を阻止する。

(もっと読む)

レベルシフト回路およびこれを含む半導体集積回路装置

【課題】入力信号の電圧振幅が小さい場合にも十分な振幅変換能力を有し、低消費電力でありかつ高速動作が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路を構成するNチャネルMOSトランジスタTN‐A、TN‐BおよびPチャネルMOSトランジスタTP‐A、TP‐Bにおいて、TP‐A、TP‐Bのドレインにカレントミラー回路を構成するPチャネルMOSトランジスタTP‐CおよびTP‐Dを構成する。これにより、VDDHからVSSへの貫通電流を防止し、高速動作が可能なレベルシフト回路を提供できる。

(もっと読む)

レベルシフタ回路及びそれを具備する半導体集積回路

【課題】 負荷の影響を受けにくく、動作速度の向上等が可能なレベルシフタ回路等を提供する。

【解決手段】 電源電位VDDに接続されたトランジスタP1及びP2と電源電位VSSに接続されたトランジスタN3及びN4との間にトランジスタP5及びP6をそれぞれ挿入する。トランジスタP1のドレインと電源電位VSSとの間にトランジスタP3及びN1を挿入する。トランジスタP2のドレインと電源電位VSSとの間にトランジスタP4及びN2を挿入する。トランジスタP5とトランジスタN3との接続点をトランジスタP2のゲートに接続し、トランジスタP6とトランジスタN4との接続点をトランジスタP1のゲートに接続する。トランジスタP3とトランジスタN1との接続点及び/又はトランジスタP4とトランジスタN2との接続点から出力信号OUT及び/又はその反転信号OUTバーを外部に供給する。

(もっと読む)

レベルシフタ

【課題】入力信号にかかわらず動作し、かつ、各素子がばらついた場合でも安定して動作するレベルシフタを提供する。

【解決手段】N型トランジスタ11およびP型トランジスタ12は、所定のオフセット電位Vofsを保つように動作し、その出力であるノードn1が変動すると、N型トランジスタ15およびP型トランジスタ16によって定まるノードn2の電位によってP型トランジスタ13またはN型トランジスタ14に対してフィードバック制御する。

(もっと読む)

レベルシフト回路

【課題】 高耐圧スイッチング素子に流れる電流値の設定を容易に行うことができるレベルシフト回路を得る。

【解決手段】 低電圧側である第1電源電圧VCC1の振幅を有する2値の入力信号Sinの信号レベルに応じて定電流の供給を行う定電流回路2を用いて、高耐圧スイッチングトランジスタであるDMOSトランジスタDM1に流れる電流の供給制御を行ってDMOSトランジスタDM1のスイッチング制御を行うと共に、定電流回路2の定電流値を設定してDMOSトランジスタDM1に流れる電流値の設定を行うようにした。

(もっと読む)

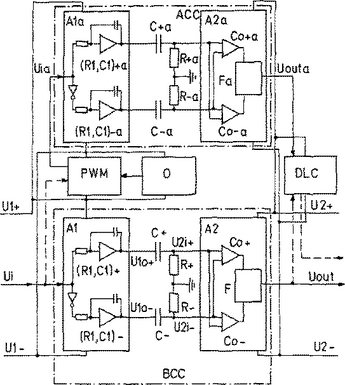

容量性障壁を備えた分離インターフェース及び該分離インターフェースによる信号の伝送方法

容量性障壁を備えた分離インターフェースを通しての信号の伝送が行われると、インターフェースの入力回路において、適切な時定数の積分による容量性障壁を備えた基本分離インターフェースの入力回路によって、伝送された入力信号UiのレプリカであるU1o+とU1o-の端の傾斜変化率または、上昇と減少時間が調整され、そして上記の信号レプリカは適切な微分ユニットで微分されて、これらの微分ユニットの時定数は信号レプリカの上昇と減少時間、よりも短かく、有利には約1ナノセカンドか、またはそれ以下である。したがって、パルス幅を非常に正確に維持できるので、容量性障壁の出力側面の上の回路では、電圧比較器のアンプは全く必要ではない。入力と出力回路に関する電圧供給ソースの間の電位差の約10kV/μsの速い変化から、データ伝送が守られる。本発明によって、100MHzの周波数までのデジタルデータ伝送が可能になる。  (もっと読む)

(もっと読む)

寄生キャパシタンスの影響を減らした電圧分配回路及びそれを含んだワードライン電圧発生回路

【課題】 本発明は電圧分配回路及びそれを含んだワードライン電圧発生回路に関する。【解決手段】 本発明による電圧分配回路は出力電圧ノードと分配電圧ノードとの間に連結された第1抵抗器、前記分配電圧ノードと接地との間に並列に連結された複数個の第2抵抗器、および選択手段を含む。前記複数個の第2抵抗器は順次に活性化されるステップ制御信号に応答して順次に選択される。そして前記選択手段は前記第2抵抗器に存在する寄生キャパシタンスの和を減らすために前記ステップ制御信号が印加されるごとに前記第2抵抗器のうちで選択された抵抗器を含んだ一部の抵抗器だけ前記第1抵抗器に連結されるようにする。

本発明による電圧分配回路によると、複数個の第2抵抗器に存在する寄生キャパシタンスの影響を減らすことができる。そして前記電圧分配回路を含んだワードライン電圧発生回路はメモリセルに安定的なワードライン電圧を提供することができる。

(もっと読む)

容量結合による高電圧レベルのシフト

【課題】簡単な回路構成で、高電圧のレベルシフトを行う。

【解決手段】アース電圧(アース1)を基準とする入力回路(10)と、コンデンサ(C1またはC2)を介して入力回路に結合された別のアース電圧(アース2)を基準とする出力回路(12)とを備える回路構造である。

(もっと読む)

シフトレジスタ及びその駆動方法

本発明は、インバータの入力部をインバータの閾値電位にし、インバータの入力部に容量手段を介してCK信号を入力することで、CK信号は増幅され、その増幅されたCK信号をシフトレジスタに用いる。つまり、インバータの閾値電位を取得することで、トランジスタの特性ばらつきに殆ど影響しないシフトレジスタを提供することができる。  (もっと読む)

(もっと読む)

レベルシフト回路

【課題】 耐圧の低い素子を使用でき、素子定数のばらつきの影響を受けにくいレベルシフト回路を提供する。

【解決手段】 駆動制御信号SHがLからHになると、レベルシフト回路18のトランジスタQ11、Q12がオフし、Q13、Q14、Q15がオンする。これによりノードNc、Neの電位が上昇し、駆動回路15のトランジスタQ17がオン、Q18がオフする。このとき、ノードNdの電圧V(Nd)はVDD−Vf(D14)−Vz(D12)までしか低下しないため、トランジスタQ5のゲート・ソース間を高電圧から保護することができる。また、トランジスタQ12のゲートにVHS−Vf(D14)なる中間的な電圧が与えられているため、トランジスタQ12とQ11は電圧VBSを分担する。このため、トランジスタQ11、Q12を高電圧から保護することができる。

(もっと読む)

201 - 220 / 246

[ Back to top ]