Fターム[5J056AA11]の内容

Fターム[5J056AA11]の下位に属するFターム

ECLから (6)

TTL、DTLから (1)

I2Lから (1)

MOSから (9)

MES、ショットキーFETから

その他から (3)

ECLへ (1)

TTL、DTLへ

I2Lへ

MOSへ (18)

MES、ショットキーFETへ

信号線 (3)

その他へ (1)

振幅拡大 (172)

振幅縮小 (38)

正電位の振幅→負電位の振幅 (2)

負電位の振幅→正電位の振幅

一方の電位の振幅←→正負の電位の振幅 (5)

直流レベルのシフト (74)

信号幅の変換 (3)

タイミングの調整、遅延、同期 (148)

整合 (285)

Fターム[5J056AA11]に分類される特許

81 - 100 / 246

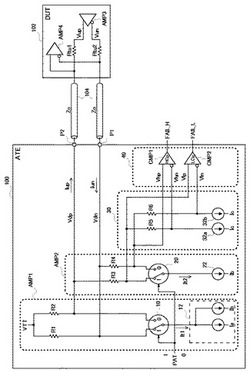

試験装置

【課題】双方向差動インタフェースを有するDUTの試験装置を提供する。

【解決手段】第1抵抗R1は、第1入出力端子P1と電源端子VTTの間に設けられる。第2抵抗R2は、第2入出力端子P2と電源端子VTTの間に設けられる。第1切り換えスイッチ10は、パターンデータPATの値に応じて第1入出力端子P1側と第2入出力端子P2側のいずれかを第1電流源12と結合する。第3抵抗R3は、第2入出力端子P2に接続される。第4抵抗R4は、第1入出力端子P1に接続される。第2切り換えスイッチ20は、パターンデータPATの値に応じて第1入出力端子P1側と第2入出力端子P2側のいずれかを第2電流源22と結合する。レベルシフト回路30は、第3抵抗R3の第2端子の電位Vlpおよび第4抵抗R4の第2端子Vhpの電位を、所定レベルだけシフトする。比較回路40は、電位VhpをVhnと比較し、電位VlpをVlnと比較する。

(もっと読む)

レベル変換回路

【課題】単一導電型のトランジスタにより構成されたレベル変換回路において、小占有面積のリセット回路を提供すると共に、パルス幅の広い入力信号にも対応可能にする。

【解決手段】レベル変換回路は、出力端子OUTとロー側電源ノードS3との間に接続し、ゲートが第1容量素子C1Aを介して入力端子INに接続した第1トランジスタQ4Aと、出力端子OUTとハイ側電源ノードS4との間に接続する第1電流駆動素子I1Aとを備える。第1トランジスタQ4Aのゲートとロー側電源ノードS3との間には、ゲートが第2容量素子C2Aを介してリセット端子RSTに接続した第2トランジスタQ6Aおよび、当該第2トランジスタQ6Aのゲートとロー側電源ノードS3との間に接続した第2電流駆動素子(I2A/B)からなるリセット回路が設けられる。

(もっと読む)

レベルシフタ回路及び半導体集積回路

【課題】レベルシフタ回路の出力端子に生ずるパルス性の不所望な電位変化を抑制する。

【解決手段】レベルシフタ回路は、レベルシフト部(201)と、その出力信号を、イネーブル信号(IEN)のアサートに呼応して外部出力するための出力部(202)とを含む。上記レベルシフト部(201)は、上記イネーブル信号のアサートタイミングよりも遅いタイミングで論理レベルが確定される出力ノード(ITX)を含み、上記出力部(202)は、上記イネーブル信号がアサートされた状態で、上記出力ノードの論理レベルに応じて上記出力部の出力論理を確定するための能動素子(Q11,Q13)を含む。上記イネーブル信号がアサートされるタイミングよりも遅いタイミングで上記出力部の出力論理が確定されることで、パルス性の不所望な電位変化(ノイズ)を生じないようにする。

(もっと読む)

信号レベル変換回路

【課題】双方向タイプの信号レベル変換回路の信号方向を切り替える制御信号を不用とする。

【解決手段】双方向タイプの信号レベル変換回路70にはVCCA系回路部1、VCCB系回路部2、レベシフタ回路LS1、及びレベルシフタ回路LS2が設けられる。VCCA系回路部1には入出力端子PadA、インバータINV1、インバータINV4、ラッチ回路LATCH1、出力バッファ回路SBUFF2、遅延回路DIN3、遅延回路DIN4、2入力NAND回路NAND2、及び2入力NOR回路NOR2が設けられる。VCCB系回路部2には入出力端子PadB、インバータINV2、インバータINV3、ラッチ回路LATCH2、出力バッファ回路SBUFF1、遅延回路DIN1、遅延回路DIN2、2入力NAND回路NAND1、及び2入力NOR回路NOR1が設けられる。信号レベル変換回路70では方向切り替え制御信号を必要としない。

(もっと読む)

レベルシフタ回路

【課題】動的に電源電圧と周波数を変化させる半導体集積回路において、異電源間に必要なレベルシフタ回路を高速化する。

【解決手段】第1の電源電圧で動作する第1のインバータ120と、上記第1のインバータ120で論理反転した入力信号の振幅を第1の電源電圧の電位から第2の電源電圧の電位に変換するもので上記第2の電源電圧で動作する振幅変換回路121と、第1のインバータの出力信号と上記振幅変換回路121からの振幅が変換された入力信号とを入力すると共に上記両電源電圧が異なるときは上記振幅変換回路121からの入力信号を、また、上記両電源電圧が同電位のときは第1のインバータの出力信号を選択し、論理反転して出力信号として伝達するもので上記第2の電源電圧で動作する選択回路123と、を備えた事で、振幅変換が必要ない場合に、信号の伝達速度の高速化を実現できる。

(もっと読む)

レベルシフティング回路および方法

特定の実施例では、方法は、電圧プルアップロジックを含むレベルシフティング回路への入力で入力電圧を受け取ることを含む。その方法は、レベルシフティング回路からの出力信号を提供することを含む。その方法は、レベルシフティング回路の電圧プルアップ論理回路を選択的に動作させることをさらに含む。  (もっと読む)

(もっと読む)

レベルシフタ回路

【課題】素子数が少なくても動作が速いレベルシフタ回路を提供する。

【解決手段】入力電圧Vinが接地電圧Vssになり、PMOS31及びNMOS21のゲート電圧(レベルシフタ部の入力端子の電圧)が電源電圧Vddになると、NMOS23がオンすることにより、PMOS33及びNMOS22のドレイン電圧(レベルシフタ部の出力端子の電圧)が電源電圧Vppになりやすくなり、出力電圧Voutが接地電圧Vssになりやすくなる。つまり、レベルシフタ回路の動作が速くなる。また、従来のレベルシフタ回路と比較し、インバータの数が少なくなるので、素子数が少なくなる。

(もっと読む)

レベルシフト回路

【課題】2つの電源電圧の大きさが逆転しても適切なレベルシフトを行う。

【解決手段】 トランジスタQ1,Q21,Q2,Q22,Q6,Q26を含むアンプは、第2電源VCC2によって動作し、第2電源VCC2の電圧範囲で変化する入力信号を第2電源VCC2の電圧範囲内で増幅する。アンプの出力は、トランジスタQ6,Q7,Q26,Q27を含む変換部により、第1電源VCC1によって動作し、アンプの出力を第1電源VCC1の電圧範囲内の出力に変換する。アンプOP1,OP2は、この変換部の出力を第1電源(1/2)VCC1基準で増幅する。前記変換部は、第2電源VCC2を電源とするトランジスタQ6,Q26と、第1電源VCCを電源とするトランジスタQ7,Q27をカレントミラーとして、変換を行う。

(もっと読む)

レベルシフト回路及びそれを用いたドライバと表示装置

【課題】低振幅の入力信号を高速に高振幅信号に変換するレベルシフト回路の提供。

【解決手段】第1及び第2の入力信号vi1、vi2に基づき、第1及び第2の出力端子の一方を第1のレベルシフト回路10と、第2のレベルシフト回路20と、第1の制御信号S0に基づき、前記第1及び第2の出力端子のうち、前記第1及び第2の入力信号が前記第1及び第2の入力端子に入力される時点で前記第2電圧レベルとされている一つの出力端子について、前記一つの出力端子と前記第2の給電端子間の電流経路を、前記第1及び第2の入力信号が前記第1及び第2の入力端子に入力される時点を含む所定期間、切断し、前記所定期間の後、前記一つの出力端子と前記第2の給電端子間の電流経路の切断を解除する制御を行う手段を備え、前記第1及び第2の出力端子の出力振幅は、前記第1及び第2の入力信号の振幅よりも大とされる。

(もっと読む)

半導体装置

【課題】レベル変換の振幅差が大きい場合にも高速に信号レベルを変換する回路を提供することを目的とする。

【解決手段】第1信号を受けて、それよりも大きな振幅の第2信号を出力する差動型レベル変換回路を含む半導体装置であって、前記差動型レベル変換回路は、前記第1信号を受けるための第1MISFET対(MN1-2)と、前記第1MISFET対に対する耐圧緩和のための第2MISFET対(MN3-4)と、出力すべき前記第2信号をラッチするためのものであって、交差結合されたゲートを持つ第3MISFET対(MP1-2)とを有し、前記第2及び第3MISFET対のゲート絶縁膜の膜厚を前記第1MISFET対よりも厚くし、前記第2及び第1MISFET対のしきい値電圧を前記第3MISFET対よりも小さくする。レベル変換の振幅差が4倍以上にも大きいような場合でも、高速なレベル変換が行える。

(もっと読む)

半導体集積回路及び電圧制御発振器

【課題】待機状態から任意の容量安定状態への過渡時間の短いMOSバラクタを提供する。

【解決手段】Nウェルを有するMOSバラクタ素子の動作待機時に電極の電位からウェル領域の電位を引いた電位差を0以上にする制御回路を備えることにより、動作待機時から任意の容量安定状態への過渡時間を短くすることが可能となる。また、Pウェルを有するMOSバラクタ素子の動作待機時に電極の電位からウェル領域の電位を引いた電位差を0以下にする制御回路を備えることにより、動作待機時から任意の容量安定状態への過渡時間を短くすることが可能となる。

(もっと読む)

アンチヒューズリペア電圧制御回路

【課題】 アンチヒューズリペア時、高い電源電圧または低いバックバイアス電圧がセルや周辺回路またはコア領域のような回路部に影響を与えるのを防止する。

【解決手段】 アンチヒューズリペア電圧制御回路は、アンチヒューズのリペアに対応して、アンチヒューズリペアイネーブル信号を提供するアンチヒューズリペアイネーブル部と、前記アンチヒューズリペアイネーブル信号によって、電源電圧が第1回路部に伝達されることを制御する電源電圧制御部と、前記アンチヒューズリペアイネーブル信号によって、バックバイアス電圧が第2回路部に伝達されることを制御するバックバイアス電圧制御部とを具備する。

(もっと読む)

レベルシフト回路

【課題】高電圧電源VHに接続された出力回路における貫通電流を防止することで消費電力の削減とノイズを防止すると共に、高速動作を可能とする。

【解決手段】第1トランジスタであるPMOSトランジスタM1と、第2トランジスタであるNMOSトランジスタM2のゲートバイアス電圧を与える第1,2バイアス生成回路を、ダイオード接続したPMOSトランジスタM5とNMOSトランジスタM6、およびPMOSトランジスタM7とNMOSトランジスタM8を直列に接続して構成することで、コンデンサC1の電荷が高電圧電源VHへ放電されることをなくし、出力信号がハイレベルからローレベルに、逆にローレベルからハイレベルに移行するときの両方において貫通電流を防止でき、それに伴い省電力とノイズの低減を可能とした。

(もっと読む)

レベルシフタ、表示画面駆動回路及び映像表示系統

【課題】 制御信号を駆動電圧を発生させるレベルシフタを提供することを目的とする。

【解決手段】 該レベルシフタは、一端が前記制御信号及び参考電圧とカップリングし、他端が前記駆動電圧及び補助電圧とカップリングする貯蔵用キャパシターと、前記制御信号及び前記参考電圧の一つを選択し前記貯蔵用キャパシターの一端に提供し、前記駆動信号及び前記補助電圧の一つを選択し前記貯蔵用キャパシターの他端に提供する選択スイッチ組と、を備えて成る。前記選択スイッチ組が前記参考電圧及び前記補助電圧を選択し前記貯蔵用キャパシターに提供することにより、前記貯蔵用キャパシターが前記制御信号及び前記駆動電圧とカップリングする際に、前記貯蔵用キャパシターは前記制御信号の電圧レベルが上昇するようにすることを特徴とする。本発明は表示画面駆動回路と映像表示系統も提供する。

(もっと読む)

レベルシフト回路

【課題】出力信号の電圧レベルをシフトすることのできない期間をより短縮することのできるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、所定電位VCC1が「1200[V]」から「15[V]」へ変化するレベルシフト時に、最もVCC1側に位置するトランジスタTr1n1及びTr2n1の各ゲート並びに最もLGND電位側に位置するトランジスタTr112及びTr212の各ゲートに蓄積されている電荷を、当該レベルシフト回路1外へ放出するための引き抜き用の抵抗素子RH及び引き抜き用の抵抗素子Rlを備える。そして、引き抜き用の抵抗素子RHは、出力信号作成回路部70の基準電位であるHGND電位に接続されており、引き抜き用の抵抗素子Rlは、NOTゲート20の駆動電位である所定電位VCC3に接続されている。

(もっと読む)

レベルシフト回路およびこれを用いたDC−DCコンバータ

【課題】低電位系のMOSFETのドレイン−基板間に存在する寄生容量の影響により高電位系のラッチ回路が誤動作してしまうことを防止するレベルシフト回路を提供する。

【解決手段】本実施形態では、容量(C)51,52を配することにより、ノイズを吸収してラッチ回路100の誤動作を防止している。即ち、ラッチ回路100のインバータ(U1)41,インバータ(U2)42の入力端子と、高電位系であるラッチ回路100の基準電圧となる端子(V2L)6との間に、容量(C) 51,52を接続しているので、ノイズを容量(C)51,52に吸収させることが可能となり、ラッチ回路100の誤動作を防止することができる。

(もっと読む)

レベルシフト回路

【課題】VDD2>VSS2>VSS1、且つVDD1>VSS1の関係にある入力電圧VDD1,VSS1を入力してVDD2,VSS2にレベルシフトする際に、VSS1>VSS2になったときであってもラッチアップ現象の発生を回避する。

【解決手段】信号出力端子OUTとなるノードN1とノードN2の間に逆並列接続された2個のインバータからなり且つ電圧VDD2とVSS2で動作するラッチ回路3と、信号入力端子INとノードN3の間に接続され且つ電圧VDD1とVSS1で動作する第1のインバータ1と、ノードN3とノードN4の間に接続され且つ電圧VDD1とVSS1で動作する第2のインバータ2と、ノードN1,N2,N3に接続された第1の反転駆動回路4と、ノードN1,N2,N4に接続された第2の反転駆動回路5と、電圧VSS1の端子側をアノード、電圧VSS2の端子側をカソードとするダイオードD1とを設ける。

(もっと読む)

バッファ、レベルシフト回路及び表示装置

【課題】同一導電型のトランジスタで構成されブートストラップ効果を利用したバッファに備わるトランジスタの劣化や誤動作を抑え、バッファの信頼性を向上する。

【解決手段】入力端子inには、レベルシフタからの出力信号/02が供給される。この出力信号/02にはLowレベルの浮きが生じており、Lowレベルの電位はVEEより若干高いVEE’になっている。このようなLowレベル浮きが生じている出力信号/02がゲートに供給され、かつ、ブートストラップ効果によって高電位電源VDDの2倍程度にまで高められた電位がドレインに供給されるトランジスタTr312を、ボディ構造を有するTFTとし、そのボディBをソースSに接続する。

(もっと読む)

半導体素子駆動装置、電力変換装置、及びモータ駆動装置、並びに半導体素子駆動方法、電力変換方法、及びモータ駆動方法

【課題】直列接続IGBT3,4の接続点7のdV/dtによる誤動作発生時に、上下アーム短絡などの事故を回避できる高信頼性IGBT駆動装置を提供する。

【解決手段】高低圧側IGBT3,4は、デッドタイムを挟み相補的にオン/オフ制御される。これらデッドタイム期間中に、高圧側IGBT3をオフさせるリセットパルスRSを、例えば、次のような要領で発生させる。(1)低圧側IGBT4のオン指令LDの直前に、(2)低圧側IGBT4のオン指令LDの直前から、このオン指令LDと重なる期間tdをもつように、(3)デッドタイムDT期間中、継続して、(4)低圧側IGBT4がオンとなる直前のデッドタイム期間中、継続して、(5)高圧側IGBT3のオン状態を観測したとき、低圧側IGBTのオン指令を無効とするように、リセットパルスを生成する。

(もっと読む)

レベルシフタ及び表示装置

【課題】同一導電型のトランジスタで構成されブートストラップ効果を利用したレベルシフタを構成する場合に、Lowレベル浮きやHiレベル落ちによる振幅不足を防ぎ、十分なレベルの出力を得られるようにすること。

【解決手段】トランジスタTr312とトランジスタTr315は、バックゲートBGを備える。レベルシフタ301は、トランジスタTr312,315のバックゲートBGに印加する電位を入力信号VBG,/VBGを用いて制御し、オフの状態にあるトランジスタTr312,315の閾値電圧VthOFFを、入力信号01,/01のLowレベル−低電位電源VEEよりも大きくする。

(もっと読む)

81 - 100 / 246

[ Back to top ]