Fターム[5J056AA11]の内容

Fターム[5J056AA11]の下位に属するFターム

ECLから (6)

TTL、DTLから (1)

I2Lから (1)

MOSから (9)

MES、ショットキーFETから

その他から (3)

ECLへ (1)

TTL、DTLへ

I2Lへ

MOSへ (18)

MES、ショットキーFETへ

信号線 (3)

その他へ (1)

振幅拡大 (172)

振幅縮小 (38)

正電位の振幅→負電位の振幅 (2)

負電位の振幅→正電位の振幅

一方の電位の振幅←→正負の電位の振幅 (5)

直流レベルのシフト (74)

信号幅の変換 (3)

タイミングの調整、遅延、同期 (148)

整合 (285)

Fターム[5J056AA11]に分類される特許

21 - 40 / 246

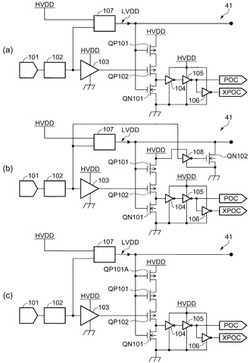

集積回路装置

【課題】高い電源電圧を元に、低い電圧を発生させることで、低い電圧を用いる内部回路と高い電圧を用いる外部回路とのインターフェイスを行う場合、外部回路を動作させた状態で内部回路の動作を休止させる場合がある。この場合、低い電圧の発生を止めたことをインターフェイスを行う回路に伝達する回路(POC回路)が必要となるが、従来の回路では、低い電圧を発生させる状態で貫通電流が流れる回路を用いる必要があり、消費電流が増加してしまうという課題がある。

【解決手段】低い電圧の発生を停止する信号により、レギュレーター107の動作を止め、VOUTが十分下がった状態でインターフェイスを行う回路へ供給停止信号をレベルシフト回路121に伝達する。そのため、レベルシフト回路121での貫通電流の発生を抑えられる。さらに、供給停止信号を提供するPOC回路41内での定常状態での貫通電流を防止できる。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】3Tr2Cで構成されるインバータ回路において、トランジスタTr2のゲートと低電圧線L1との間、さらにトランジスタTr2のソースと低電圧線L1との間に、入力電圧Vinと低電圧線L1の電圧との電位差に応じてオンオフ動作するトランジスタTr1,Tr2が設けられている。トランジスタTr2のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr2のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

半導体装置及び電子機器

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路160を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路160に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能とする。

(もっと読む)

レベルコンバータ回路を備えたMOSトランジスタ回路

【課題】動作上の欠点を除去し、また、用いるトランジスタ数が少ない静的動作のレベルコンバータ回路を備えたMOSトランジスタ回路を提供する。

【解決手段】高電源電圧回路側の第一のCMOSインバータの遷移領域TRHが、低電源電圧回路側の第二のCMOSインバータの出力論理信号の変化範囲に含まれるように前記第一のCMOSインバータと前記第二のCMOSインバータの動作を設定し、第一のCMOSインバータをレベル変換回路とし、第一のCMOSインバータを第二のCMOSインバータの出力で駆動するように構成する。

(もっと読む)

バス絶縁型PLC

【課題】フォトカプラ等の絶縁素子の必要数を大幅に削減可能として上記実装装置の規模の小型化とコストの大幅な削減化を可能とすること。

【解決手段】CPU2と、CPUとの間で信号の入力伝送および出力伝送の少なくとも一方の伝送をする複数の入/出力回路6,7と、CPUからの信号はシリアル/パラレル変換し、入/出力回路からの信号はパラレル/シリアル変換するバスI/F3a,3bと、CPUとバスI/Fとの間に配されて信号をシリアル伝送する信号伝送バス8a,8bと、バスI/Fと各入/出力回路との間に配されて信号をパラレル伝送する信号伝送バス9a,9b,10a,10bと、を備え、シリアル信号伝送バス8a,8b内に、絶縁回路部20a,20bを設けた構成。

(もっと読む)

レベルシフト回路及びそれを用いた発振器

【課題】 出力波形の割れや抜けを無くし、回路の誤動作が防止される低電圧動作のレベルシフト回路を提供する。

【解決手段】 レベルシフト回路は、電源端子VDDにソースを接続した第1のPMOSトランジスタP1と、接地端子GNDにソースを接続したNMOSトランジスタN1と、PMOSP1のドレインとNMOSN1のドレインとの接続点に接続された出力端子OUTと、NMOSN1のゲートに接続された入力端子INと、電源端子VDDにソースを接続し、PMOSP1のゲートにドレイン及びゲートを接続し、このドレインを第2の抵抗R2を介して接地端子GNDに接続した第2のPMOSトランジスタP2とを有し、PMOSP1及びP2は、カレントミラー回路を構成している。レベルシフト回路の出力波形の割れや抜けが無くなって誤動作を防止することが可能になる。

(もっと読む)

電源回路

【課題】どの条件下でも一定のパルス幅で駆動する電源回路を提供する

【解決手段】電源回路10は、外部回路20と接続可能である。電源回路10は、一定の内部電圧を外部回路20に印加するフィードバック回路12と、パルスのパルス幅に応じた電荷を外部回路20に供給する電荷供給回路14と、外部回路20のオペレーションに対応するオペレーション状態に依存しない一定のパルスを電荷供給回路14に供給する電源制御回路16と、備える。

(もっと読む)

レベルシフト回路

【課題】貫通電流を防止するレベルシフト回路

【解決手段】従来のレベルシフト回路にPMOSトランジスタMP3およびMP4ならびにレベルシフト回路の出力信号をフィードバックするスイッチ制御回路を追加することで、従来回路の問題点であった貫通電流の流れる時間を減らし、消費電力を低減させ、かつ実装面積の増加を抑えながら高速動作させる。

(もっと読む)

RFID用リーダ装置及びその制御方法

【課題】直流遮断コンデンサを用いるリーダ装置の送受信の切り替え待機時間を短縮する。

【解決手段】リーダ装置2は、RFID3に対し、高周波搬送波信号を送信する送信回路4と、送信回路5により送信された高周波搬送波信号から、RFID3の応答データを抽出する受信回路5とを備え、受信回路5は、高周波搬送波信号を検波する検波回路14と、検波回路14による検波後の高周波搬送波信号の信号処理を行い、RFID3の応答データを取得する信号処理回路18と、検波回路14と信号処理回路18とを接続する配線に間挿された直流遮断コンデンサ15と、直流遮断コンデンサ15と直列に接続され、オフのときに直流遮断コンデンサ15の少なくとも一方の端子をオープンとするスイッチ素子16とを有することを特徴とする。

(もっと読む)

レベルシフト回路

【課題】消費電流を低減することができ、信号伝達に必要な電源電圧を低減することができ、電源電圧が揺れても正確に信号を伝達することができるレベルシフト回路を得る。

【解決手段】本発明のレベルシフト回路は、インバータ回路INV2、レベルシフト素子MOS1、第1の抵抗R1及びカレントミラー回路CM1を備える。インバータ回路INV2は、入力信号を反転して出力する。レベルシフト素子MOS1は、入力信号を反転した信号をゲート信号として動作する。第1の抵抗R1の一端は、インバータ回路の出力に接続されている。カレントミラー回路CM1は、第1の抵抗R1を介してインバータ回路INV2の出力から入力した電流に対応する電流をレベルシフト素子MOS1のソースから接地点に流す。

(もっと読む)

レベルシフタおよびそれを用いた試験装置

【課題】従来と異なる形式のレベルシフタを提供する。

【解決手段】レベルシフタ200は、第1下側電圧VssLと第1上側電圧VddLのいずれかのレベルをとる入力信号Inを、第2下側電圧VssHと第2上側電圧VddHのいずれかのレベルをとる出力信号Outにレベルシフトする。SRフリップフロップ100の出力信号Outは、そのセット端子への信号のポジティブエッジに応じて第2上側電圧VddHに遷移し、そのリセット端子への信号のポジティブエッジに応じて第2下側電圧VssHに遷移する。ANDゲート202は、SRフリップフロップ100の出力信号Qに対して反転論理レベルを有するフィードバック信号FBQと入力信号Inとの論理積を、SRフリップフロップ100のセット端子へと出力する。NORゲート204はフィードバック信号FBQと入力信号Inとの否定論理和を、SRフリップフロップ100のリセット端子へと出力する。

(もっと読む)

ドライバ回路および試験装置

【課題】ドライバ回路が出力する波形の歪みを低減する。

【解決手段】出力端子に高レベル電圧を出力するか、または、低レベル電圧のいずれを出力するかを切り替える、高レベルトランジスタおよび低レベルトランジスタと、与えられる高レベル制御信号に応じて、高レベルトランジスタに高レベル電圧を出力させるか否かを制御する高レベルインバータと、与えられる低レベル制御信号に応じて、低レベルトランジスタに低レベル電圧を出力させるか否かを制御する低レベルインバータと、高レベルインバータのスレショルド電圧に応じた電圧の高レベル制御信号と、低レベルインバータのスレショルド電圧に応じた電圧の低レベル制御信号とを生成する制御信号生成部とを備え、制御信号生成部は、正論理電圧または負論理電圧の少なくとも一方の電圧が異なる高レベル制御信号および低レベル制御信号を生成するドライバ回路を提供する。

(もっと読む)

半導体回路

【課題】 高電位側スイッチング素子の導通を示す第1状態から前記高電位側スイッチングデバイスの非導通を示す第2状態への遷移、または前記第2状態から前記第1状態への遷移に伴い発生する過渡的な電圧ノイズに曝された場合であっても誤信号が発生することのない半導体回路を提供する。

【解決手段】 高電位側スイッチング素子駆動回路1は、レベルシフト回路2の第1の負荷抵抗28、28に発生するオン側、オフ側の第1のレベルシフト済み信号S4、S5のうち少なくとものいずれか一方に信号が発生したときに、第2の負荷抵抗30、29に同時に発生する第2のレベルシフト済み信号S6、S7によって制御され、他方の出力が発生しないようにレベルシフトの出力を抑制する短絡手段31、32を有する。

(もっと読む)

可変駆動電圧により動作するオシレータ

【課題】安定した発振周期の信号を出力することができるオシレータを提供すること。

【解決手段】複数の論理素子がリング状に接続され、所定の周期の発振信号を出力する可変駆動電圧により動作するオシレータであって、複数の論理素子に選択的に印加される第1及び第2の駆動電圧を発生させる内部電圧発生手段を備え、発振信号の周期が正常状態である場合には、第1の駆動電圧が複数の論理素子に印加され、発振信号の周期が正常状態より短いか又は長い場合には、第2の駆動電圧VOSCが複数の論理素子に印加され、発振信号の周期が一定に維持されるように構成されている。

(もっと読む)

CMOS入力バッファ回路

【課題】低電圧動作かつ低消費電流のCMOS入力バッファ回路を提供すること。

【解決手段】ドレインが電源端子VDDに接続され、ゲートが出力端子に接続されたディプレッション型NMOSトランジスタと、ソースがディプレッション型NMOSトランジスタのソースに接続され、ドレインが出力端子に接続され、ゲートが入力端子に接続されたPMOSトランジスタと、ソースが基準端子GNDに接続され、ゲートが入力端子に接続され、ドレインが出力端子に接続されたNMOSトランジスタとを備えた構成とした。

(もっと読む)

半導体装置および電子機器

【課題】パワー半導体素子を駆動するためのドライバを低コストで得ることが可能な半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置101は、ノーマリーオン型の第5の電界効果トランジスタ16,17を含み、入力信号処理部65から受けたスイッチング制御信号の基準電圧をシフトした信号を出力するためのレベルシフト部62と、ノーマリーオン型の第1の電界効果トランジスタ51および第3の電界効果トランジスタ53と、ノーマリーオフ型の第2の電界効果トランジスタ52および第4の電界効果トランジスタ54とを備え、レベルシフト部62、第1の電界効果トランジスタ51および第3の電界効果トランジスタ53は第1の半導体チップ71に含まれている。

(もっと読む)

ドライブ回路

【課題】低電圧の制御信号を高電圧の制御信号に変換して出力する高圧用のドライブ回路において、待機時の消費電力を削減することができるようにする。

【解決手段】低圧部1からの制御信号a1〜d1及びa2〜d2により高圧部2のトランジスタMN1〜MN8を駆動し、操作対象3に駆動信号を出力する。その際、低圧部1からの制御信号a1〜d1をそれぞれ論理積ゲートQ1〜Q4の一方の入力端子を介して高圧部2のトランジスタMN1,MN3,MN5,MN7のゲートに入力し、論理積ゲートQ1〜Q4の他方の入力端子には高圧部2のオン/オフ信号を入力する。

(もっと読む)

高電圧論理回路

相対的に大きな電圧範囲を有するデジタル入力及び出力信号を扱うことができる高電圧論理回路が説明される。例示的設計において、高電圧論理回路は、入力ステージ、第2ス

テージ、及び出力ステージを含んでいる。入力ステージは、少なくとも1つの入力信号を

受信し、(i)第1の電圧範囲を有する少なくとも1つの第1の中間信号と、(ii)第2の電圧範

囲を有する少なくとも1つの第2の中間信号とを提供する。第2ステージは、第1及び第2の

中間信号を受信し当該信号を論理機能に基づいて処理し、(i)前記第1の電圧範囲を有する第1の駆動信号と、(ii)前記第2の電圧範囲を有する第2の駆動信号とを提供する。出力ス

テージは、前記第1及び第2の駆動信号を受信し、第3の電圧範囲を有する出力信号を提供

する。ここにおいて第3の電圧範囲は、前記第1及び第2の電圧範囲の各々より大きいもの

であってもよい。

(もっと読む)

半導体集積回路装置

【課題】低コストで低電圧高速動作が可能なI/O回路を備えた半導体集積回路装置を提供する。

【解決手段】I/O回路において、I/O電圧vcc(例えば3.3V)をvcc_18(例えば1.8V)へ低電圧化した場合に、速度劣化を引き起こす部分が、レベル変換部と、メインの大型バッファを駆動するためのプリバッファ部分であることに着目し、レベルアップコンバータLUCとプリバッファPBFの回路に高電圧(電圧vcc)を印加することにより、低コストで低電圧高速動作が可能なI/O回路を実現する。

(もっと読む)

半導体表示装置

【課題】良好な動作をおこなう半導体表示装置を提供する。

【解決手段】p型トランジスタ、第1の容量素子、第1のスイッチ、n型トランジスタ、第2の容量素子、第2のスイッチを有する半導体表示装置であって、第1の容量素子の第1の電極は、第1の配線に電気的に接続されており、第1の容量素子の第2の電極は、p型トランジスタのゲートに電気的に接続されており、第1のスイッチの第1の端子は、p型トランジスタのゲートに電気的に接続されており、第1のスイッチの第2の端子は、p型トランジスタの第1の端子及び第2の端子の一方に電気的に接続され、第2の容量素子の第1の電極は、第1の配線に電気的に接続されており、第2の容量素子の第2の電極は、n型トランジスタのゲートに電気的に接続されており、第2のスイッチの第1の端子は、n型トランジスタのゲートに電気的に接続されており、第2のスイッチの第2の端子は、n型トランジスタの第1の端子及び第2の端子の一方に電気的に接続されている。

(もっと読む)

21 - 40 / 246

[ Back to top ]