Fターム[5J056AA11]の内容

Fターム[5J056AA11]の下位に属するFターム

ECLから (6)

TTL、DTLから (1)

I2Lから (1)

MOSから (9)

MES、ショットキーFETから

その他から (3)

ECLへ (1)

TTL、DTLへ

I2Lへ

MOSへ (18)

MES、ショットキーFETへ

信号線 (3)

その他へ (1)

振幅拡大 (172)

振幅縮小 (38)

正電位の振幅→負電位の振幅 (2)

負電位の振幅→正電位の振幅

一方の電位の振幅←→正負の電位の振幅 (5)

直流レベルのシフト (74)

信号幅の変換 (3)

タイミングの調整、遅延、同期 (148)

整合 (285)

Fターム[5J056AA11]に分類される特許

61 - 80 / 246

高周波半導体スイッチ装置

【課題】各FETの端子間にかかる電圧を抑えつつ、高周波特性の優れた高周波半導体スイッチ装置を提供する。

【解決手段】高周波スイッチ部1に制御信号を供給する駆動回路は、第1のレベルシフト回路11と第2のレベルシフト回路12とを有し、これらはSOI構造の半導体装置に設けられ、第1のレベルシフト回路11のクロスカップルPMOSP11、P12に、ゲートに第1のバイアス電位Vb1(>0)が与えられるカスコード接続PMOSP13、P14を接続し、これらの接続ノードを第2のレベルシフト回路12の入力とし、第2のレベルシフト回路12にPMOSP23、P24およびNMOSN21、N22のカスコード接続段を設け、PMOSP23、P24のゲートには第1のバイアス電位Vb1が、NMOSN21、N22のゲートには第2のバイアス電位Vb2(>Vb1)が与えられる。

(もっと読む)

I2Cインタフェースを有するシステム及びその方法

【課題】本発明の目的は、I2Cインタフェースを有するシステムを提供することである。

【解決手段】本発明の第1の態様によると、マスター装置と前記マスター装置により制御されるスレーブ装置との間のインタフェースをとるI2Cインタフェースを有するシステムが提供される。前記マスター装置は第1のデータ・バスと接続され第1の駆動電圧で動作し、前記スレーブ装置は第2のデータ・バスと接続され第2の駆動電圧で動作し、前記システムは、それぞれ前記第1及び第2の駆動電圧の間のレベルシフト機能を有する第1及び第2の双方向デジタル入出力回路、及び前記第1及び第2の双方向デジタル入出力回路を制御するシーケンサ回路、を有し、前記シーケンサ回路は、前記第1及び第2の双方向デジタル入出力回路の出力に基づき、データの伝達方向を前記マスター装置から前記スレーブ装置へ、又は前記スレーブ装置から前記マスター装置へ切り替える。

(もっと読む)

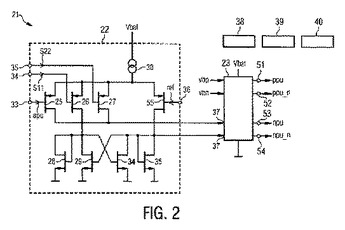

レベルシフタ

レベルシフタ(21)は、第1ステージ(22)と第2ステージ(23)とを備える。第1ステージ(22)は、第1および第2の入力(34,35)を備え、第1の状態では、回路(38,39)用に供給される少なくとも2つの第1の電源電圧(Vdig,Vdda)のうちの少なくとも1つが利用不可かどうかを示し、第2の状態では、第1の電源電圧(Vdig,Vdda)のそれぞれが、第1および第2の入力(34,35)において利用可能かどうかを示す、第1の信号(37)を生成するように構成されている。第2ステージ(23)は、出力(51〜54)を備え、第1の信号(37)がその第2の状態にあるときにのみ、第2の電源電圧(Vbat)を、通過するように切り替えて、出力(51〜54)に存在させるように構成されている。  (もっと読む)

(もっと読む)

差動増幅器、基準電圧発生回路、差動増幅方法及び基準電圧発生方法

【課題】低電圧電源で利用可能な出力精度の高い差動増幅器並びに基準電圧発生回路を提供する。

【解決手段】差動増幅器110は、差動増幅部からなるメイン差動増幅回路11と、メイン差動増幅回路11が出力する信号を増幅しオープンドレイン出力回路31で増幅された出力信号を出力する。バイアス制御差動増幅回路21は、メイン差動増幅回路11の差動増幅部の差動出力信号に含まれるオフセット電圧を検出し、検出したオフセット電圧に基づいてメイン差動増幅回路11の差動増幅部の動作点を制御して出力信号に含まれるオフセット電圧を低減する。

(もっと読む)

半導体装置

【課題】レベルシフトを行う場合に、低電圧で動作するトランジスタが使用可能であり、そのトランジスタがオンオフ動作する際の出力変化速度(動作速度)の向上を半導体チップ内の少ない占有面積で容易に実現可能な半導体装置の提供。

【解決手段】レベルシフト部5は、MOSトランジスタN2と、抵抗R2と、抵抗R1とを備え、これらが直列接続されている。抵抗R1には、ツェナーダイオードZD1が並列接続されている。ツェナーダイオードZD1は、MOSトランジスタN2がオフからオンになるときに、レベルシフト部5の出力電圧LOを所定値にクランプする。MOSトランジスタN2のドレインとソースとの間には、ツェナーダイオードZD2が並列接続されている。ツェナーダイオードZD2は、MOSトランジスタN2がオフのときに、MOSトランジスタN2のドレインとソースとの間の電圧を所定値にクランプする。

(もっと読む)

レベルシフト回路

【課題】従来のレベルシフト回路は、構成するトランジスタに低耐圧のものを利用すると、回路の高速動作に問題が生じていた。

【解決手段】本発明は、入力端子に入力される所定の振幅を有する入力論理信号に応じて、前記入力論理信号より大きい振幅を有する出力論理信号を第1の出力端子に出力するレベルシフト回路であって、前記出力論理信号の第1の論理レベルまたは第2の論理レベルを与える電源端子と、前記電源端子と前記第1の出力端子間に接続され、制御端子に前記入力論理信号に応じた信号が入力される第1のトランジスタと、前記電源端子と前記第1のトランジスタ間に接続され、前記第1のトランジスタと同期してオンまたはオフ状態になる第2のトランジスタと、を有するレベルシフト回路である。

(もっと読む)

信号伝達回路

【課題】2次側回路のGNDの電位の立上りタイミングと1次側回路から2次側回路へ信号を送るタイミングとが重なっても、トランスを介して1次側回路から2次側回路へ信号を正しく伝達することが可能な信号伝達回路を提供することを目的とする。

【解決手段】電源部54、55のnpnバイポーラトランジスタ60のON抵抗を小さくしてC点又はD点の電位と基準電圧V3とをコンパレータ2で比較しC点又はD点の電位が基準電圧V3よりも大きくなったらON抵抗が十分に小さいNチャネルのMOSFET3を立下り遅延回路4により設定される一定時間オンさせることによって、2次側回路のGNDの電位の立上りタイミングに流れるトランス53の結合静電容量を充電する電流をMOSFET3を介して1次側回路51のGNDに流す。

(もっと読む)

レベルシフト回路

【課題】パワーグランドとシグナルグランドとの差電圧がそれほど大きくない場合に、回路規模を大きくせずに信号のレベルシフトを行うことができるようにする。

【解決手段】入力部1は、一定電流が流れるバイアス部5と、一定電流に比例した比例電流を出力部2に流すための差動対回路部7とを備えている。一方、出力部2は、差動対回路部7を介して流れ込む比例電流によって信号のレベル変換を行う第1変換部17および第2変換部18を備えている。このような回路構成によると、入力部1側のシグナル電源電位SVDDと出力部2側のパワーグランド16の電位PGNDとの間に電位差を設けることができ、入力部1から出力部2に比例電流を流すことができる。こうして、信号のレベル変換が可能となる。

(もっと読む)

入力インターフェイス回路

【課題】入力信号電圧の許容範囲が広く、異なる入力信号電圧に対応可能であり、且つ簡単な構成で安価な入力インターフェイス回路を提供する。

【解決手段】電源(VCC)端子と接地(GND)端子の間でPチャネルMOSトランジスタM1とNチャネルMOSトランジスタM2が直列接続されたCMOSインバータC1を有してなる入力インターフェイス回路I1であって、NチャネルMOSトランジスタM2のゲート端子を入力端子とし、PチャネルMOSトランジスタM1のゲート端子とNチャネルMOSトランジスタM2のゲート端子の間に、閾値電圧を有する半導体素子L1が接続され、PチャネルMOSトランジスタM1のゲート端子の電位が、前記閾値電圧だけ、NチャネルMOSトランジスタM2のゲート端子の電位より高くなるように構成されてなる入力インターフェイス回路I1とする。

(もっと読む)

信号レベル変換回路

【課題】双方向タイプの信号レベル変換回路の信号方向を切り替える制御信号を不用とする。

【解決手段】信号レベル変換回路70には、方向検知回路HKC1が設けられる。方向検知回路HKC1は、ノードN2の信号S1とノードN7の信号S2が入力され、信号S1と信号S2の信号レベルを比較し、信号レベル変換回路70に入力される入力信号が第1の入出力端子PadAに入力される第1の入力信号か、或いは第2の入出力端子PadBに入力される第2の入力信号かを判断し、この判断に基づいて信号Sen1を出力する。信号Sen1に基づいて、VCCA系回路部1のスイッチSW1がオン・オフ動作して第1のラッチ回路LATCH1の接続或いは遮断が行われ、信号Sen1の反転信号である信号Sen2に基づいて、VCCB系回路部2のスイッチSW2がオン・オフ動作して第2のラッチ回路LATCH2の接続或いは遮断が行われる。

(もっと読む)

レベルシフト回路

【課題】第1p型トランジスタにおけるカット電流を低減する。

【解決手段】高レベル電源電圧HVを一端に受ける第1および第2p型トランジスタ14,20と、一端が第1および第2p型トランジスタの他端にそれぞれ接続され、他端に可変負電源電圧ZVssが供給される第1および第2n型トランジスタ18,24を含む。

第1n型トランジスタ18の制御端に通常正電源電圧Vcc、第2n型トランジスタ24の制御端に負電源電圧Vssを供給することで、第2p型トランジスタ20と第2n型トランジスタ24の接続部から高レベル正電源電圧HVのいずれかを出力する。この高レベル正電源電圧HVを出力する時に、前記可変負電源電圧ZVssを第1n型トランジスタ18の十分なオン状態が維持できる範囲内で負電源電圧Vssより高い電圧にする。

(もっと読む)

双方向バッファ回路及び信号レベル変換回路

【課題】データ転送レートを高く保ちつつ、構成が簡素な双方向バッファ回路及び信号レベル変換回路を提供する。

【解決手段】第1の端子からの信号が入力され、第2の端子へ出力する第1の出力バッファと、前記第1の端子からの信号と前記第2の端子からの信号との論理演算により、第1の制御信号を出力可能な第1の制御回路と、前記第1の制御信号により前記第2の端子を一時的に駆動可能な第1のワンショットバッファと、前記第2の端子からの信号が入力され、前記第1の端子へ出力する第2の出力バッファと、前記第1の端子からの信号と前記第2の端子からの信号との論理演算により、第2の制御信号を出力可能な第2の制御回路と、前記第2の制御信号により前記第1の端子を一時的に駆動可能な第2のワンショットバッファと、を備える。

(もっと読む)

半導体デバイス、表示パネル及び電子機器

【課題】使い勝手の良い単一チャネル型のバッファ回路を提案する。

【解決手段】絶縁基板上に単一チャネルの薄膜トランジスタで形成されるバッファ回路を、(a)第1及び第2の薄膜トランジスタが直列に接続された回路構成を有し、第1及び第2の薄膜トランジスタの接続中点を出力端とする第1の出力段と、(b)第1の制御配線に制御電極が接続される第7の薄膜トランジスタと、第2の制御配線に制御電極が接続される第8の薄膜トランジスタが直列に接続された回路構成を有し、第7及び第8の薄膜トランジスタの接続中点に現れる電位を第3の制御配線に与える第2の出力段と、(c)一方の主電極が第1の制御配線に接続され、制御電極が第3の制御配線に接続される回路構成を有し、出力端に出力パルスが現われている期間、セットパルスと同じ論理レベルの電位を第1の制御配線に印加する第9の薄膜トランジスタとで構成される。

(もっと読む)

レベルシフター

【課題】プルアップ駆動するMOSトランジスタとプルダウン駆動するMOSトランジスタのサイズを調節することによって、入力信号INのレベルが遷移する時に生じる遅延要素を除去できるレベルシフターを提供する。

【解決手段】入力信号のレベルによって第1ノードのレベルを設定するカップリング部と、前記第1ノードの信号をバッファリングし、出力信号として伝達する第1バッファーと、前記入力信号及び前記出力信号を受信して前記第1ノードを駆動する駆動部と、を備える構成とした。

(もっと読む)

レベルシフト回路

【課題】スタンバイ状態の解除時に誤動作の生じることのないレベルシフタ回路を提供する。

【解決手段】VDD1系で動作する回路の信号レベルをVDD2系の信号のレベルに変換するレベル変換回路5と、スタンバイ信号(STBY)を受けて、レベル変換回路5の入力信号(AB、ABB)をローレベルに固定するバリアゲート回路2と、入力信号(AB、ABB)がローレベルになるときに、レベル変換回路5の出力を一定電圧に保持する保持回路(MMP1、MMP2)とを備える。

(もっと読む)

レベル変換回路および画像表示装置

【課題】単一導電型のトランジスタを用いたレベル変換回路において、レベル変換する信号数が増加しても、消費電力の増大を抑制することが可能なレベル変換回路を提供する。

【解決手段】レベル変換回路は、位相の異なる入力信号INS1〜INS3をそれぞれレベル変換する単位レベル変換回路LS1〜LS3から構成される。各単位レベル変換回路LS1〜LS3の第2ブートストラップ回路120において、当該第2ブートストラップ回路120の出力ノードN6Yを充電するトランジスタQ1Yは、自己の前に活性化される他の単位レベル変換回路からの信号に応じてオン状態になり、自己の次に活性化される他の単位レベル変換回路からの信号に応じてオフ状態になる。

(もっと読む)

パワーオン検知回路およびレベル変換回路

【課題】電位が互いに異なる複数の電源電位の投入順序や立ち上がり時間に依存することなく、それら複数の電源電位の立ち上がりを安定して検出する。

【解決手段】低電源電位VDDが立ち上がり、高電源電位VCCが立ち上がっていない場合、ラッチ回路L2の入力にコンデンサC2を介してグランド電位GNDを与えることで、出力信号VOUTとして論理値‘0’を出力し、高電源電位VCCが立ち上がり、低電源電位VDDが立ち上がっていない場合、レベルシフタLSにて高電源電位VCCをグランド電位GNDに変換させることで、出力信号VOUTとして論理値‘0’を出力し、低電源電位VDDおよび高電源電位VCCの両方が立ち上がっている場合、レベルシフタLSにてグランド電位GNDを高電源電位VCCに変換させることで、出力信号VOUTとして論理値‘1’を出力する。

(もっと読む)

表示装置

【課題】レベルシフト回路を備える表示装置において、レベルシフト動作の信頼性を向上させる。

【解決手段】前記レベルシフト回路は、半導体層がポリシリコン層で構成される第1薄膜トランジスタと、前記第1薄膜トランジスタの第2電極に接続される波形整形回路と、前記第1薄膜トランジスタの第2電極と、基準電源との間に接続される定電流源とスイッチ素子とを有し、前記第1薄膜トランジスタの制御電極にはバイアス電圧が入力され、前記第1薄膜トランジスタの第1電極には入力信号が入力される。

(もっと読む)

出力バッファ回路

【課題】電源立ち上げ時における誤作動信号の発生を抑制することのできる出力バッファ回路を提供する。

【解決手段】出力バッファ回路1は、第2レベルコンバータ10bから出力される第2信号Dの電源立ち上げ時における立ち下がりタイミングを遅相させ、出力回路30に出力する第4信号Gを生成するタイミング調整回路TAを備える。タイミング調整回路TAは、第1レベルコンバータ10aの第1信号Bよりも遅く立ち下がる第3信号Eを生成する第3レベルコンバータ10cと、第3信号Eと第2信号Dとの論理和演算の結果を持つ第4信号Gを出力回路30に出力するOR回路42と、を備える。

(もっと読む)

半導体集積装置

【課題】高速で動作するレベルシフト回路を有する半導体集積装置を提供する。

【解決手段】レベルシフト回路11と、第1、第2出力ノードNout1、Nout2を充電する第1、第2カレントミラー回路12、13と、第1、第2カレントミラー回路12、13を動作させる第1、第2スイッチ回路16、19と、第1カレントミラー回路12の入力側に並列接続され、第2出力信号Vout2により駆動され、第1スイッチ回路16が第1カレントミラー回路12の動作を停止するときに、第1出力ノードNout1の充電の停止を早めるための第5スイッチ素子20と、第2カレントミラー回路13の入力側に並列接続され、第1出力信号Vout1により駆動され、第2スイッチ回路19が第2カレントミラー回路13の動作を停止するときに、第2出力ノードNout2の充電の停止を早めるための第6スイッチ素子21と、を具備する。

(もっと読む)

61 - 80 / 246

[ Back to top ]