Fターム[5J056DD28]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723)

Fターム[5J056DD28]の下位に属するFターム

相補動作するもの、CMOS (940)

Fターム[5J056DD28]に分類される特許

61 - 80 / 783

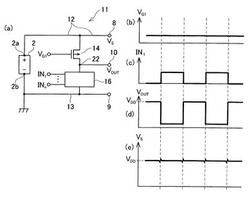

反転電圧出力回路

【課題】入力信号の変化に応じて直流電源の非接地電圧と接地電圧の間で反転する電圧を出力する回路であり、非接地端子に接続されている電源線に生じる電圧変動を抑制する。

【解決手段】電流制限素子14とスイッチング回路16が直列に接続されており、電流制限素子とスイッチング回路の中間点22の電圧を出力する。スイッチング回路の導通時にスイッチング回路を流れる電流が電流制限素子によって制限される。直流電源の非接地端子に接続されている電源線12に生じる電圧変動が抑制され、電源線12に接続されているアナログ回路等の動作が安定する。

(もっと読む)

半導体装置

【課題】ドライブ能力およびスルーレートを調節可能な出力ドライバを備え、従来よりも微細化することができる半導体装置を提供する。

【解決手段】半導体装置は、コア回路から転送されるデジタルデータを出力するために複数のサブドライバを含む出力ドライバODと、サブドライバを選択するセレクタとを備える。各サブドライバは、デジタルデータに従って出力データを立ち上げまたは立ち下げるために、第1の電源PS1と出力配線WOUTとの間に接続された出力トランジスタTP30と、出力トランジスタTP30のゲートと第2の電源VSSとの間に直列に接続されたスイッチングトランジスタTN33およびスルーレート調整トランジスタTN34とを備える。各スルーレート調整トランジスタTN34は、出力データの立ち上がりまたは立ち下がりのスルーレートを決定するために調整されたゲート電位をセレクタによって選択的に与えられる。

(もっと読む)

半導体装置

【課題】電源分離領域内の配線密度を低下させる。

【解決手段】動作モードに応じて電源電圧が供給される電源線VVDDと、常に電源電圧が供給される電源線VDDと、通常モードで電源線VVDDを電源線VDDに接続するか、またはスリープモードで電源線VVDDを接地電位とするか、を切り替える電源切替回路(104、111、110が相当)と、電源線VVDDから電源供給されスリープモードでは動作を停止する第1回路ブロック101と、電源線VDDからの電源供給によって常に動作可能とする第2回路ブロック103と、電源線VVDDの電位が接地電位近傍にあるか否かにそれぞれ応じて、第2回路ブロック103の入力端をハイレベルにするか、第1回路ブロック101の出力信号を第2回路ブロック103に伝達可能とするか、を制御する入力制御回路(114、118が相当)と、を備える。

(もっと読む)

電源スイッチ回路

【課題】チップ面積を増大させることなく突入電流の発生を抑制することができる電源スイッチ回路を提供することである。

【解決手段】本発明にかかる電源スイッチ回路は、第1の電源線21と第2の電源線22との間に接続され、第1の電源線21と第2の電源線22との接続および非接続を第1のイネーブル信号4に応じて切り替える第1のスイッチ素子1と、第1の電源線21と第2の電源線22との間に接続され、第1の電源線21と第2の電源線22との接続および非接続を切り替える第2のスイッチ素子2と、第2の電源線22から電源が供給される論理ゲートを少なくとも1つ備え、第2のスイッチ素子2を制御するスイッチ制御回路3と、を有する。スイッチ制御回路3は、スイッチ制御回路3に供給される第2のイネーブル信号5及び第2の電源線22の電圧に基づいて第2のスイッチ素子2を制御する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】多ビットの差動受信回路および差動終端抵抗を内蔵して、半導体チップ面積と消費電流の増大を軽減する。

【解決手段】複数の差動受信回路2A、B〜Nと複数の差動終端抵抗回路3A、B〜Nと複数の制御電圧供給回路6A、B〜Nに、レプリカ抵抗回路4と制御電圧生成回路5が共用される。複数の回路6A、B〜Nの各回路は、第1非反転入力と第1反転入力と出力を有する差動増幅器DA1を含む。第1供給回路6Aの第1差動増幅器の第1非反転入力と、第2供給回路6Bの第2差動増幅器の第1非反転入力と、第N供給回路6Nの第N差動増幅器の第1非反転入力とに、生成回路5から生成される差動終端抵抗制御電圧Vcont1.5が共通に供給される。第1差動増幅器の出力電圧VoutAと第2差動増幅器の力電圧VoutBと第N差動増幅器の出力電圧VoutNとは、第1と第2と第Nの差動終端抵抗回路3A、3B、3Nにそれぞれ供給される。

(もっと読む)

半導体集積回路およびその動作方法

【課題】伝送線路の特性インピーダンスと終端抵抗のインピーダンス整合を容易とする。

【解決手段】差動終端抵抗回路3は直列の第1と第2の素子Q1、Q2を含み、レプリカ抵抗回路4は直列の第3と第4の素子Q3、Q4を含み、制御電圧生成回路5は制御差動増幅器DA2と直列の制御素子Q8と第1と第2の電圧降下回路R7、8;R9とを含む。増幅器DA2の非反転入力と反転入力に、基準電圧Vrefと回路4の素子Q3、Q4のレプリカ抵抗電圧Vrcmがそれぞれ供給される。回路5の第1と第2のレプリカ抵抗制御電圧Vcont0、1は、回路4の素子Q3、Q4の制御入力にそれぞれ供給される。差動終端抵抗回路3の素子Q1、Q2は、第2のレプリカ抵抗制御電圧Vcont1と第2の電圧降下回路R9の電圧降下との合計電圧である差動終端抵抗制御電圧Vcont1.5に基づく制御出力電圧Voutによって制御される。

(もっと読む)

入出力バッファ回路

【課題】チップ面積を削減させると共に、動作周波数をより高くする。

【解決手段】外部接続端子VIOと、ソースを電源に接続し、ドレインを外部接続端子VIOに接続し、ゲートに駆動信号が供給可能とされるPMOSトランジスタMP7と、PMOSトランジスタMP7のバックゲートと電源間に接続され、開閉が制御されるバックゲート制御回路22と、PMOSトランジスタMP7のドレイン・ゲート間に接続され、開閉が制御されるゲート制御回路23と、PMOSトランジスタMP7のゲートと駆動信号が供給される駆動端との間に接続され、開閉が制御される駆動側制御回路24と、を備え、外部接続端子VIOから駆動信号に係る信号を出力しないハイインピーダンス状態において、バックゲート制御回路22および駆動側制御回路24が開放状態とされ、ゲート制御回路23が短絡状態とされる。

(もっと読む)

レベルシフト回路及び通信回路

【課題】 入力信号の電圧振幅の最大値と同電圧を供給する電源電圧の入力を必要とせず、異なる電圧振幅の入力信号が入力された場合でも動作可能であり、貫通電流による消費電力の増大を低減できるレベルシフト回路及び通信回路を提供する。

【解決手段】 出力信号の電圧振幅の最大値と同電圧を供給する第1電圧源と内部出力ノードN1の間に設けられた負荷抵抗回路R1と、入力信号の入力電圧を受け付け、制御ノードN2の電圧値を入力信号の電圧振幅の最大値に対応する制御電圧値に保持する電圧記憶回路11と、内部出力ノードN1と入力信号の入力ノードN3の間に設けられ、制御ノードN2の電圧と入力信号の電圧の電圧差に応じてON状態とOFF状態が切り替わるように構成され、入力信号の電圧値が電圧振幅の最大値の場合にOFF状態に、入力信号の電圧値が電圧振幅の最小値の場合にON状態になる第1スイッチング回路MN1と、を備える。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

内部電位発生回路

【課題】内部電位のずれを短時間で調整することができる内部電位発生回路を提供することを課題とする。

【解決手段】内部電位発生回路は、参照電位テストモードにおいてクロック信号に同期してカウントを行う参照電位カウンタ(205)と、参照電位カウンタのカウント値に応じた参照電位を生成する参照電位発生回路(203)とを有し、第1の内部電位発生回路は、参照電位テストモードにおいて参照電位カウンタのカウントに並列してクロック信号に同期してカウントを行う第1のカウンタ(225)と、参照電位テストモードにおいて第1のカウンタのカウント値に応じて外部電位を抵抗分割した第1の比較電位を生成する第1の比較電位発生回路(223)と、第1の比較電位が参照電位発生回路により生成される参照電位より低いときには第1の内部電位を昇圧する第1の電位発生回路(226)とを有する。

(もっと読む)

論理否定型電子回路

【課題】 ブートストラップ機能を有する電子回路に関し、出力電圧の降下を防止して、論理否定型電子回路の誤作動を阻止し、また、長い作動時間を確保する。

【解決手段】 負荷トランジスタ、駆動トランジスタ部、充電用トランジスタ並びにブートストラップ容量を具備し、入力電圧の位相を出力部から反転せしめて出力する論理否定型電子回路について、入力される電圧の位相を反転させて出力するインバータ回路をさらに設け、このインバータ回路の入力節点を前記出力部に、出力節点を前記充電用トランジスタのゲートにそれぞれ接続する。

(もっと読む)

半導体装置

【課題】基準電圧生成回路に電源電圧が投入されてから安定平衡状態に達するまでの時間を短縮する回路を提供することを課題とする。

【解決手段】スタートアップ回路から基準電圧生成回路に入力される初期電圧を、基準電圧生成回路の安定平衡状態における内部電圧に近い電圧とすればよい。また、このような電圧を電源が遮断された状態でも保持しておくことができ、且つ起動時に出力することのできるスタートアップ回路とすればよい。

(もっと読む)

半導体スイッチ

【課題】端子切替時の挿入損失の増加を抑制した半導体スイッチを提供する。

【解決手段】実施形態によれば、電源回路部と制御回路部とスイッチ部とを備えた半導体スイッチが提供される。前記電源回路部は、内部電位生成回路と第1のトランジスタとを有する。前記内部電位生成回路部は、電源線に接続され、入力電位よりも高い第1の電位を生成する。前記第1のトランジスタは、前記内部電位生成回路の入力と出力との間に接続され、前記第1の電位が前記入力電位よりも低下したときオンして前記第1の電位を前記入力電位以上に保持するようにしきい値電圧が設定されたことを特徴とする。前記制御回路部は、前記第1の電位を供給され、ハイレベルまたはローレベルの制御信号を出力する。前記スイッチ部は、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

スイッチングトランジスタの制御回路

【課題】イネーブル信号をHIGHにしてから急速にスイッチングトランジスタをオンし、かつ突入電流を防止することが可能なスイッチングトランジスタの制御回路を提供すること。

【解決手段】イネーブル信号によりトランジスタM2はオフする。トランジスタM8はオフし、ノードCTの電位はグラウンドと等電位になり、反転器の出力ACTはHIGHとなり、トランジスタM9はオンする。イネーブル信号の反転信号によりトランジスタM5はオフし、トランジスタM3、M4、M6のゲート電位はM4とIBIASで決まる電位VBIASと等電位となってトランジスタM3、M4、M6はオンとなり、並列接続されたトランジスタM3、M6の能力に応じたIGD(大)が流れる。トランジスタM1、M7は、電流IGD(大)によって急速にゲート容量へ電荷が蓄えられて急速にオンになり、電流IOUT、IDETが流れる。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】スタンバイ状態への設定と解除が頻繁に繰り返されることにより、消費電力が増大することを避けることのできる半導体装置を提供する。

【解決手段】内部回路50と、第1制御信号を受けて内部回路への電源供給を制御する電源制御回路40と、第2制御信号を受けて第1制御信号を出力する制御信号発生回路30と、を備え、制御信号発生回路30は、第2制御信号の非活性期間が第1の期間未満であるときに第1制御信号を非活性状態とせず、第1の期間以上であるときに第1制御信号を非活性状態とする。

(もっと読む)

回路装置及びシステム

【課題】出力モードを切り換えることにより効率的な通信ができる回路装置及びシステム等を提供すること。

【解決手段】回路装置100は、バスHBSを介してホスト装置200に信号を出力する出力回路110と、出力回路110を制御する出力制御回路120とを含む。出力回路110は、出力ノードNQと第1の電源ノードVSSとの間に設けられる第1の導電型のトランジスターTNと、出力ノードNQと第2の電源ノードVDDとの間に設けられる第2の導電型のトランジスターTPとを含む。出力制御回路120は、第1の出力モードでは、第1の導電型のトランジスターTN及び第2の導電型のトランジスターTPのいずれか一方をオフにし、他方をオン・オフする制御を行い、第2の出力モードでは、第1の導電型のトランジスターTN及び第2の導電型のトランジスターTPを排他的にオン・オフする制御を行う。

(もっと読む)

モードコントロール回路

【課題】 パワーダウンモードを含む複数の動作モードを有する半導体集積回路において、モード切り換えを行うモードコントロール回路の消費電力を少なくする。

【解決手段】 制御電圧VCに基づきパワーダウンを設定するか解除するかの判定を行う回路としてオフセット付き電圧比較器30Aを設けた。制御電圧VCがオフセット電圧V0よりも低く、オフセット付き電圧比較器30Aがパワーダウン解除信号MD0を非アクティブレベルとしている間は、基準電圧発生回路10Aを動作させず、制御電圧VCとの比較に用いる基準電圧V1〜V3を出力させない。制御電圧VCがオフセット電圧V0を越えて上昇し、パワーダウン解除信号MD0がアクティブレベルになったとき、基準電圧発生回路10Aを動作させ、基準電圧V1〜V3と制御電圧VCとの比較によるモード切り換えを行わせる。

(もっと読む)

信号駆動回路

【課題】DCオフセットを低減し、正確な出力アナログ電圧値を得る信号駆動回路を提供する。

【解決手段】信号駆動回路は、デジタルデータに基づいて第一アナログ電圧を発生するデジタル/アナログコンバータ(DAC)と、第一アナログ電圧に基づいてアナログバッファによって第二アナログ電圧をロードに選択的に出力、またはアナログバッファを通過することなしに第一アナログ電圧をロードに選択的に出力する出力回路とを含む。

(もっと読む)

クロック負昇圧回路

【課題】回路構成が簡易、小型でウェル・バイアス電圧の立ち上がり時間が短く、安定した負昇圧クロックを供給することが可能なクロック負昇圧回路を提供する。

【解決手段】クロック負昇圧回路部301、クロック負昇圧回路部302、クロック負昇圧回路部301、クロック負昇圧回路部302のウェル層上に設けられたNMOSトランジスタ107に電圧を供給するキャパシタ403、NMOSトランジスタ104を備え、クロック負昇圧回路部301が備えるNMOSトランジスタ104とキャパシタ403とを接続する電圧ライン303、クロック負昇圧回路部302が備える2つのNMOSトランジスタ104の出力を接続する電圧ライン303によってクロック負昇圧回路を提供する。

(もっと読む)

61 - 80 / 783

[ Back to top ]