Fターム[5J056DD28]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723)

Fターム[5J056DD28]の下位に属するFターム

相補動作するもの、CMOS (940)

Fターム[5J056DD28]に分類される特許

21 - 40 / 783

レベルシフト回路

【課題】伝播遅延時間を短縮する。

【解決手段】インバータINV1,INV2と、ラッチ回路1と、反転駆動回路2,3と、セレクタ4を備える。N1=VSS2、N2=VSS2、N3=VSS2、N4=VDD2のとき、入力端子INがVDD1→VSS1に変化したとき、トランジスタMP5をオンして大きな電流をVDD2からノードN1に流し高速にノードN1をVSS1→VDD2に変化させる。その後、トランジスタMP5はオフし、ノードN1はインバータINV4でVDD2に保持される。これで、N1=VDD2、N2=VDD2、N3=VDD2、N4=VSS2となる。次に入力端子INがVSS1→VDD1に変化したとき、トランジスタMN2がオンして大きな電流をノードN1からVSS2に流し高速にノードN1をVDD2→VSS2に変化させる。

(もっと読む)

バススイッチ回路

【課題】より確実に信号を伝送することが可能なバススイッチ回路を提供する。

【解決手段】バススイッチ回路は、第1、第2の入出力端子間に接続されたバススイッチ素子を備える。バススイッチ回路は、第1の入出力端子と第1の電源電圧が印加される第1の電圧線との間に接続され、第1の制御信号により制御される第1のスイッチ素子を備える。バススイッチ回路は、第2の入出力端子と第2の電源電圧が印加される第2の電圧線との間に接続され、第2の制御信号により制御される第2のスイッチ素子を備える。バススイッチ回路は、第1の信号と、第2の信号とに基づいて、遅延信号を出力する遅延信号生成回路を備える。バススイッチ回路は、第1の信号、第2の信号、および、遅延信号に基づいて、第1および第2の制御信号を出力する制御信号生成回路と、を備える。

(もっと読む)

半導体装置

【課題】信号転送ラインの充放電によって消費される電力を低減する。

【解決手段】フリップフロップ構成のアンプ回路AMPを含むレシーバ回路R0kと、データバスDBとレシーバ回路R0kの入力端T2との間に挿入され、データバスDBがVPERI−NVthに達するとオフするトランジスタM7を備える。本発明によれば、トランジスタM7によって入力端T2の振幅が制限されることから、データバスDBがローレベルからハイレベルに変化する際の転送速度が向上する。しかも、アンプ回路AMPがフリップフロップ構成を有していることから、フリップフロップが反転した後は貫通電流が生じない。これにより、消費電力がより一層低減される。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

回路装置及び電子機器

【課題】断熱的回路動作により消費電力を抑制することができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、第1の基準電圧を基準として電圧が周期的に変化する第1の電源電圧VP、及び第2の基準電圧を基準として電圧が周期的に変化する第2の電源電圧VMが供給されて断熱的回路動作を行う断熱的回路100と、第1の直流電源電圧VDD及び第2の直流電源電圧VSSが供給されて動作する非断熱的回路120と、断熱的回路100と非断熱的回路120との間に設けられるラッチ回路210とを含む。ラッチ回路210は、断熱的回路100からの出力信号D2を、第1の電源電圧VPが極大となり第2の電源電圧VMが極小となるタイミングに対して設定された第1のラッチ期間においてラッチし、出力信号D2のラッチ信号Q2を非断熱的回路120に対して出力する。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

差動入力回路および差動入力回路の電圧特性調整方法

【課題】ソースが共通接続されそれぞれのゲートが二つの入力端子に接続さた二つのトランジスタを有する差動対を備える差動入力回路において、より適正に入力オフセットをより小さくする。

【解決手段】トランジスタTin1,トランジスタTin2のドレインに高電圧印加回路60を接続し、トランジスタTin1のソースおよびトランジスタTin2のソースと接地電圧印加点GNDとの間にトランジスタTsenを設け、論理ローレベルの電圧の制御信号SENをスイッチング回路70に入力すると共に制御信号Tcとしてクロック信号を入力して入力端子IN1に電圧V1を印加すると共に入力端子IN2に電圧V2を印加し、検出した出力端子OUT,OUTBの電圧に応じてトランジスタTin1,Tin2のドレインに高電圧印加回路60により電源電圧Vddhを印加する

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

半導体装置

【課題】 本実施形態は、出力ドライバのドライブ能力のキャリブレーション精度を向上することが可能な半導体装置を提供する。

【解決手段】 第1、第2のプルアップドライバユニットPUDUa、PUDUbは、プルアップドライバを調整する。プルダウンドライバユニットPDDUbは、プルダウンドライバを調整する。キャリブレーション回路CBCは、プルアップドライバのキャリブレーション時、基準電圧VREFと、基準抵抗RZQに基づく第1のプルアップドライバの出力電圧を比較して第1、第2のプルアップドライバユニットのドライブ能力を決定し、プルダウンドライバのキャリブレーション時、基準電圧と、第2のプルアップドライバとプルダウンドライバの接続ノードの電圧を比較してプルダウンドライバのドライブ能力を決定する単一の比較器COMPを有している。

(もっと読む)

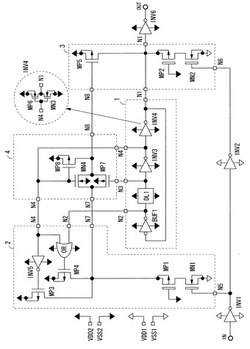

レベルシフト回路

【課題】更なる消費電力低減および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2Aは、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41および第2NMOSトランジスタ42を備える他、第3NMOSトランジスタ43および第4NMOSトランジスタ44をも備える。第1PMOSトランジスタ31および第2PMOSトランジスタ32それぞれのソース端子は、第1基準電位Vddlより高い第2基準電位Vddhに接続される。第3NMOSトランジスタ43および第4NMOSトランジスタ44それぞれのドレイン端子も第2基準電位Vddhに接続される。

(もっと読む)

半導体装置

【課題】 動作試験用の外部抵抗素子を用意することなくZQキャリブレーション回路の動作試験を行える半導体装置を提供する。

【解決手段】 半導体装置は、外部端子と、外部端子に接続され、当該外部端子に接続される外部抵抗素子を利用してキャリブレーションを行うキャリブレーション回路と、内部抵抗素子と、内部抵抗素子と外部端子との間に設けられたスイッチと、を備える。外部端子に外部抵抗素子が接続されていない状態で、スイッチを導通状態にして内部抵抗素子をZQ端子に電気的に接続する。これにより、外部抵抗素子に代えて内部抵抗素子を利用してキャリブレーションを行うことができる。

(もっと読む)

リンギング抑制回路

【課題】簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、PチャネルMOSFET4及びNチャネルMOSFET5の直列回路を接続し、制御回路11は、差動信号のレベルがハイからローに変化したことを検出すると、PチャネルMOSFET4及びNチャネルMOSFET5を同時に一定期間オンさせる。これにより、差動信号のレベルが遷移する期間に信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーをFET4及び5のオン抵抗により吸収させてリンギングの発生を抑制する。

(もっと読む)

差動入力バッファ

【課題】動作モード切り換え時におけるノイズを抑制する。

【解決手段】差動入力バッファ1は、動作モードを通常状態又は省電力状態のいずれかに切り換える電源回路MN1,MN2と、ソースフォロア回路を構成する半導体素子MP1,MP3及びMP2,MP4のそれぞれの寄生容量の合計である第1の寄生容量に対応する第2の寄生容量を有する半導体素子MP7,MP8により構成されるダミー回路とを有し、動作モードの切り換え時に第1の寄生容量に起因して発生する電流の流通方向と、動作モードの切り換え時に第2の寄生容量に起因して発生する電流の流通方向とが共通の配線において相反する構成を有する。

(もっと読む)

駆動回路、駆動信号出力回路及びインクジェットヘッド

【課題】出力する駆動信号の遅延を小さくし且つ小型化した安価な駆動回路、駆動信号出力回路及びインクジェットヘッドを実現することである。

【解決手段】駆動回路30は、負荷を駆動するプッシュ側のMOSFET32及びプル側のMOSFET33と、アノード、カソードがMOSFET32のゲート、ソースに接続されたツェナーダイオード38と、アノード、カソードがMOSFET33のソース、ゲートに接続されたツェナーダイオード39と、昇圧回路31の出力端とMOSFET32のゲートとに接続された抵抗36と、昇圧回路31の出力端とMOSFET33のゲートとに接続された抵抗37と、抵抗36、抵抗37に並列に接続されたスピードアップコンデンサ42,43と、を備える。MOSFET32,33のソースが高圧側、グランドに接続され、MOSFET32,33のドレインが互いに接続される。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

差動増幅回路

【課題】チップ面積を小さくする。

【解決手段】一端がグランド端子14に接続される定電流源13と、ソースが共通に定電流源13の他端に接続され、ゲートが入力端子A、Bにそれぞれ接続される第1および第2の差動対(Q11、Q12およびQ13、Q14に相当)と、第1の差動対のそれぞれのドレインにそれぞれのソースを接続するnMOSトランジスタQ15、Q16と、nMOSトランジスタQ15、Q16のそれぞれのドレインを出力端子C、Dとし、出力端子C、Dと電源端子11との間に接続される負荷部(図1のQ17、Q18に相当)と、を備え、第1の差動対のそれぞれのドレインを第2の差動対の逆相となるそれぞれのドレインに接続し、nMOSトランジスタQ15、Q16のそれぞれのゲートは、nMOSトランジスタQ15、Q16のドレインにそれぞれ接続する。

(もっと読む)

半導体装置

【課題】スタンバイ時のリーク電流と回路面積の増大を抑制する。

【解決手段】第1電源に接続する第1の回路11の入力対に出力が夫々接続された第2及び第3の回路12、13と、前記第1の回路の入力、又は、前記第1の回路の内部ノードに接続された第4の回路14と、を含み、前記第2の回路及び前記第3の回路は、第2電源と第3電源間に接続され、スタンバイ時にパワーゲーティングされる回路を有し、前記第2の回路は、前記第2及び第3電源電位を振幅範囲とする信号を入力し、前記第2の回路の出力は前記第3の回路の入力に接続され、前記第1の回路の出力信号の振幅範囲は、前記第1電源電位と、前記第2又は第3電源電位とされ、前記第4の回路は、パワーゲーティング時に前記第1の回路の前記入力対、又は前記内部ノードの論理値を保持し、スタンバイ時にも前記第1の回路の出力信号の論理を前記入力信号に関連した論理に維持する。

(もっと読む)

レベル変換回路

【課題】Lレベル出力も高電位側電源から決定されるようにできるレベル変換回路を提供する。

【解決手段】高電位電源VDDから論理レベル設定抵抗RLを経由して出力ノードBに至る第1経路と、高電位電源VDDから論理レベル設定抵抗RLを経由しないで出力ノードBに至る第2経路と、を設ける。切換えスイッチ部120,110は、Lレベル出力の場合には第1経路を導通させ、Hレベル出力の場合には第2経路を導通させる。さらに、Lレベル出力の場合には、カレントミラー回路130を有する定電流源がONになり、出力ノードBから一定電流を引き抜く。前記出力ノードBは、終端抵抗RLを介して終端電圧VTに接続されている。Lレベル出力の電位VOUTは、終端電圧VTの値ではなく、論理レベル設定抵抗RLの値によって調整される。

(もっと読む)

レベル生成回路

【課題】 耐圧の低いMOSFETを保護するためにゲート接地として動作する、MOSFETのゲート電圧を生成するための外部電源を不要にする。

【解決手段】 第1電源電圧から一定の大きさの第1電流を生成する定電流生成部と、第1薄膜NMOSFETと第2薄膜NMOSFETから構成され、第1電流に比例した大きさの第2電流を出力する第1カレントミラー回路部と、第2薄膜NMOSFETを保護するためにゲート接地として用いる第3薄膜NMOSFET及び第1厚膜PMOSFETと、第1電源への電流の逆流を防ぐための第1ダイオードと、第3薄膜NMOSFETのゲート−ソース間電圧がマイナスになることを防ぐための第2ダイオードとからなる保護回路部と、第2電流に比例した大きさの第3電流を出力する第2カレントミラー回路部と、第3電流により第1定電圧を生成する第1ツェナーダイオード部とを備える。

(もっと読む)

21 - 40 / 783

[ Back to top ]