Fターム[5J056DD28]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723)

Fターム[5J056DD28]の下位に属するFターム

相補動作するもの、CMOS (940)

Fターム[5J056DD28]に分類される特許

41 - 60 / 783

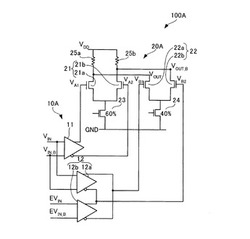

差動出力バッファ

【課題】本発明は、差動データ信号の変化を強調した強調済み差動データ信号を出力する差動出力バッファに関し、負荷容量や回路構成を大きく増やすことなく複数段にわたる高精度な強調を可能にする。

【解決手段】差動データ信号VIN,VIN_Bと、差動データ信号を所定の時間だけ遅延し、反転した、反転遅延差動データ信号EVIN_B,EVINとを、所定の比率で混合した、混合差動データ信号VB1,VB2を生成する混合回路12を有する混合段10Aと、複数の差動増幅等の組合せからなる出力段20Aとを備え、混合段10Aが、所要の強調量に応じて、混合回路12での差動データ信号と反転遅延差動データ信号との混合比を1:0、1:1、0:1のいずれかに設定する混合比設定回路を含む。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路のデータレートの変化時に発生するスキューを抑制する。

【解決手段】一つの実施形態によれば、レベルシフト回路には第1及び第2のレベルシフタが設けられる。第1のレベルシフタは、第1乃至4のトランジスタが設けられ、レベルシフトされた第1の出力信号を出力する。第2のレベルシフタは、第5乃至8のトランジスタが設けられ、レベルシフトされた第1の出力信号とは逆位相の第2の出力信号を出力する。第1の入力信号が入力される第1のトランジスタと差動対をなす第2のトランジスタに、第1の入力信号とは逆位相のハイレベルの第2の入力信号が入力されると第3及び4のトランジスタも同時にオンする。第2の入力信号が入力される第5のトランジスタと差動対をなす第6のトランジスタに、ハイレベルの第1の入力信号が入力されると第7及び8のトランジスタも同時にオンする。

(もっと読む)

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

半導体集積回路の出力バッファ回路、及び半導体集積回路

【課題】半導体集積回路の出力バッファ回路において電流の流れ込みを防止し、動作を高速化し、回路規模を削減する。

【解決手段】出力バッファ回路11は、常時オンの電源VDD、オン/オフ制御される電源VDD1、電源VDD1の電位を反転した反転信号INVOUTを出力するインバータ回路41、トランジスタP1A1,PP2,PP3、トランジスタP1A1を制御するドライブ回路51を備える。トランジスタP1A1は、入出力端子E1Aに接続されたドレイン、電源VDD1に接続されたソース、電源VDDに接続されたバックゲート、ドライブ回路51に接続されたゲートを有する。トランジスタPP2,PP3のバックゲート及びトランジスタPP2のソースは電源VDDに接続され、トランジスタPP2のゲート及びトランジスタPP3のソースは電源VDD1に接続され、トランジスタPP3のゲートには反転信号INVOUTが入力される。

(もっと読む)

判定帰還型イコライズ回路

【課題】低電圧動作及び高速動作が可能な、判定帰還型のイコライズ回路を提供すること。

【解決手段】本発明にかかる判定帰還型イコライズ回路は、ダイナミック型サンプル回路1、ラッチ回路2及びバッファ回路3を備える。ダイナミック型サンプル回路1は、入力データIN及びINB、フィードバック信号FB1〜FBn及びFBB1〜FBBnをサンプリングし、サンプリングした信号を加算したサンプル信号SS及びSSBを出力する。ラッチ回路2は、差動サンプル信号サンプル信号SS及びSSBの差電圧を増幅し、増幅した信号を保持する。なお、ラッチ回路2は、差動サンプル信号SS及びSSBが過渡状態にあるときの差電圧を増幅する。バッファ回路3は、ラッチ回路2により保持された信号を出力データOUT及びOUTBとして出力する。

(もっと読む)

出力回路

【課題】負荷容量の要求仕様に適合する出力回路を提供する。

【解決手段】出力回路1は,第1の電源VDDと出力トランジスタP1のソースとの間に設けられた電流調整用トランジスタP2と,出力信号EXが,第2の電位から第1の電位に変化する途中で,電流調整用トランジスタP2の電流を増大させるよう,出力信号EXの電位に応じて,電流調整用トランジスタP2のゲートを制御する電流調整回路11とを有する。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路の出力信号のノイズを低減する。

【解決手段】一つの実施形態によれば、レベルシフト回路は第一及び第二のレベル変換部が設けられる。第一の出力加速回路は、レベルシフトされた第一の入力信号の立ち上りエッジを制御し、信号変化部分が多段階に分割された第一の信号を生成する。第二の出力加速回路は、レベルシフトされた第一の入力信号の立ち下りエッジを制御し、信号変化部分が多段階に分割された第二の信号を生成する。第三の出力加速回路は、レベルシフトされた第二の入力信号の立ち上りエッジを制御し、信号変化部分が多段階に分割された第三の信号を生成する。第四の出力加速回路は、レベルシフトされた第二の入力信号の立ち下りエッジを制御し、信号変化部分が多段階に分割された第四の信号を生成する。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S5に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。第1のトランジスタT1のゲート端子には、伝送路27の波形を整形するためのキャパシタC1の第1端が接続され、キャパシタC1の第2端はクランプ回路46に接続されている。クランプ回路46は、プルダウン用のトランジスタT1と同様に、キャパシタC1の第2端が接続されたノードNDの電位を制御する。

(もっと読む)

差動出力バッファ

【課題】送信状態とスタンバイ状態との間の遷移時間の増大を抑制しつつ、電流の変動を低減する。

【解決手段】メインドライバ1は、差動信号PREP、PRENのレベル変換を行い、バイパス回路2は、メインドライバ1の動作状態とスタンバイ状態との間の遷移時に高電源電位VDDから低電源電位VSSに流れる電流I5の変化量が一定の範囲内に収まるようにメインドライバ1に流れる電流I5をバイパスさせる。

(もっと読む)

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

出力回路、温度スイッチIC、及び、電池パック

【課題】電源電圧が動作電圧以下でも出力が不定にならず、かつ面積の小さい出力回路を提供する。

【解決手段】インバータ回路の電源端子にスイッチ回路を設け、電源電圧が回路の動作電圧以下のとき、スイッチ回路がインバータ回路の動作を停止させる。そして、インバータ回路の出力端子に電流源を設け、インバータ回路の動作が停止したときに出力を電源電圧に固定する、ように構成した。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

レベルシフト回路および半導体集積回路装置

【課題】回路面積を大きくせずに電源投入時の貫通電流を防止するレベルシフト回路を提供する。

【解決手段】アシスト回路(200)は、第1および第2スイッチ(N21、P21)と、電圧設定回路(300)とを備える。第1および第2スイッチ(N21、P21)は、第1インバータ(101)の出力ノード(BB)と、レベルシフタ(104)の入力ノード(AA)との間に挿入され、第1電源電圧(VDD1)に応答して回路を開閉する。第2電源電圧(VDD2)に基づいて設定電圧を生成する。第1電源電圧(VDD1)が供給される前に第2電源電圧(VDD2)が供給されたときに、レベルシフタ(104)の入力ノード(AA)の電圧を設定電圧に設定する。

(もっと読む)

双方向レベルシフト回路

【課題】高速に信号の伝達が可能な双方向レベルシフト回路を提供する。

【解決手段】実施形態によれば、第1の回路と、第2の回路と、第3の回路と、第4の回路と、を備えた双方向レベルシフト回路が提供される。前記第1の回路は、双方向に信号を伝達する。前記第2の回路は、前記第1の回路の両端の電位の変化に基づいて前記第1の回路の伝達方向を検出する。前記第3の回路は、前記第1の回路の両端の電位のいずれかがローレベルからハイレベルに上昇してから、前記第1の回路の両端の電位のいずれもがハイレベルになるまでの第1の期間を検出する。前記第4の回路は、前記第1の回路の両端にそれぞれ接続され、前記第1の回路の出力側に前記第1の期間ハイレベルの電位を供給する。

(もっと読む)

レベル変換回路及び半導体装置

【課題】低面積化を図ること。

【解決手段】各信号BDT1〜BDTmをレベルシフトする回路として、クロックトレベルシフト回路(CLS回路)36(361〜36m)を用いた。CLS回路361は、ダイナミックコンパレータ回路(DC回路)411と、ラッチ回路421とを備える。DC回路411は、Lレベルのクロック信号ACKに応答してリセット状態となり、Lレベルの信号CDTm,XCDTmを出力する。また、CLS回路361は、Hレベルのクロック信号ACKに応答して比較状態となり、H1レベルの信号BDTm,XBDTmをH2レベルの信号CDTm,XCDTmにレベル変換する。ラッチ回路421は、相補な信号CDTm、XCDTmに応じた信号ADTm,XADTmを出力し、Lレベルの信号CDTm,XCDTmに応答して出力レベルを保持する。

(もっと読む)

インターフェース回路

【課題】 中間電位の出力が可能なトレラント機能を有するインターフェース回路等を提供する。

【解決手段】 第1の電位VDDと第1の電位以下である第2の電位VSSとを受け取るインターフェース回路10。内部データ信号P、XNと第1の内部信号n1とを受け取る前置駆動回路PD、PDaと、前置駆動回路からの信号n2、n3を受け取る出力駆動回路ODaと、出力駆動回路の出力部と電気的に接続された入出力パッドPADと、入出力パッドに第1の電位よりも高い電位が印加された場合に、前置駆動回路からの信号を第1の電位よりも高くして出力駆動回路をオフ状態にする第1の保護回路(P2、P5、P5a)と、第1の内部信号を第1の電位よりも高くして前置駆動回路をオフ状態にする第2の保護回路(P2、P7、P6、P6a)とを含み、出力駆動回路はトランスミッションゲートを含み、中間電位を入出力パッドに出力する。

(もっと読む)

半導体装置、回路基板装置及び情報処理装置

【課題】小規模な回路で送受信に応じた最適なインピーダンス調整を行う。

【解決手段】選択部15が、送信部11のインピーダンス調整時か、受信部12のインピーダンス調整時かに応じて異なる基準電圧を選択し、選択した基準電圧を基準電圧生成部14に生成させ、基準電圧生成部14が、選択部15により選択された基準電圧を生成して、インピーダンス調整部13に入力し、インピーダンス調整部13が、入力された基準電圧に応じて、送信部11または受信部12のインピーダンスを別々に調整する。

(もっと読む)

半導体装置

【課題】クロック生成回路からクロック信号を受けるドライブ回路の経年劣化を抑制する。

【解決手段】半導体装置1は、クロック信号INT1−SIGを生成して出力するクロック生成回路2と、クロック生成回路2からクロック信号INT1−SIGを受けるドライブ回路3とを備え、クロック生成回路2は、クロック信号INT1−SIGを生成して出力ノード2aから出力するクロック出力モードと、出力ノード2aの電位をハイレベルに固定する第1のクロック停止モードと、出力ノード2aの電位をロウレベルに固定する第2のクロック停止モードとを有する。

(もっと読む)

多入力差動増幅器

【課題】各動作モードにおいてレベルシフト回路を用いることなく所望の入力電圧範囲となる多入力差動増幅器を提供する。

【解決手段】差動部1は、バイアス部2と出力部3との間に設けられ、第一入力部10と第二入力部20とを有する。第一入力部10は、ソースがバイアス部2と接続され、ドレインが出力部3と接続された1個のn型MOSFET(M11)からなる。第二入力部20は、直列接続される2個のn型MOSFET(M21)、(M22)と、直列接続される2個のn型MOSFET(M23)、(M24)とが2列に並列接続される。また、入力端INaはM11のゲートに接続され、入力端INxはM22とM23のゲートに接続され、入力端INyはM21とM24のゲートに接続される。バイアス部2は1つの定電流源21を有し、出力部3は2つのp型MOSFET(Q1、Q2)で構成のカレントミラー回路を有する。

(もっと読む)

41 - 60 / 783

[ Back to top ]