Fターム[5J056FF07]の内容

Fターム[5J056FF07]に分類される特許

21 - 40 / 879

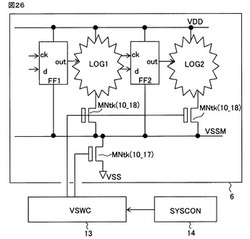

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体装置

【課題】作製コストが低減され、かつ歩留まりが向上された半導体装置、および消費電力が低減された半導体装置を提供することである。

【解決手段】第1のトランジスタおよび第2のトランジスタと、第1のトランジスタ群および第2のトランジスタ群を具備し、第1のトランジスタ群は、第3のトランジスタ、第4のトランジスタおよび4の端子を有しており、第2のトランジスタ群は、第5乃至第8のトランジスタおよび4の端子を有しており、第1のトランジスタ、第3のトランジスタ、第6のトランジスタ、第8のトランジスタはnチャネル型トランジスタが用いられ、第2のトランジスタ、第4のトランジスタ、第5のトランジスタ、第7のトランジスタはpチャネル型トランジスタが用いられる半導体装置である。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

半導体装置

【課題】新たな構成の半導体装置を提供する。

【解決手段】半導体装置は、p型の第1のトランジスタ、n型の第2のトランジスタ、第3のトランジスタ及び第4のトランジスタを有する。第3のトランジスタのソース又はドレインの一方は、第1の電位を供給することができる機能を有する配線に接続され、他方は、第1のトランジスタのソース又はドレインの一方に接続される。第2のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの他方と接続され、他方は、第4のトランジスタのソース又はドレインの一方に接続される。第4のトランジスタのソース又はドレインの他方は、第1の電位よりも低い第2の電位を供給することができる機能を有する配線に接続される。第3のトランジスタ及び第4のトランジスタのチャネル形成領域には酸化物半導体材料が用いられる。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

半導体装置

【課題】出力インピーダンスを切り替えた場合の出力トランジスタに対する電源配線抵抗等の見かけ上の変動を抑制し、出力インピーダンスを切り替えた際の出力インピーダンスの誤差を低減する。

【解決手段】本発明による半導体装置は、電源端子に接続された電源配線(10)と、出力端子に接続された信号配線(20)と、前記電源配線と前記信号配線との間に並列接続された複数のトランジスタ(TP1〜TP7,TN1〜TN7)と、前記複数のトランジスタのうち、特定のトランジスタ(TP4,TN4)を基準として前記電源配線および前記信号配線の長手方向において相互に対照をなす位置関係にあるトランジスタを単位として前記複数のトランジスタを選択的に活性化させる制御回路とを備える。

(もっと読む)

信号出力回路

【課題】トランジスタ製造工程をnpn型の製造工程のみとして、使用可能な化合物半導体の自由度を高め、単相のデジタル信号により外部から出力透過/遮断を切替制御する。

【解決手段】トランジスタとしてnpn型を用いて構成し、入力バッファ11で、外部入力された単相切替指示信号10Sを、互いの位相が反転している差動切替指示信号11Sに変換し、発生制御回路13で、差動切替指示信号11Sに基づいて、制御電圧発生回路14における制御電圧VCSの発生を制御するための発生制御信号13Sを出力し、制御電圧発生回路14で、発生制御信号13Sに基づいて、単相切替指示信号10Sの論理に応じて電圧値が変化する制御電圧VCSを発生させて出力し、出力回路15で、入力された差動入力信号INをインピーダンス変換し差動出力信号OUTとして出力し、制御電圧VCSに基づいて当該差動入力信号INの出力透過/遮断を切り替える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

半導体装置

【課題】貫通電流を少なくできる半導体装置を提供する。

【解決手段】データを出力する出力部を各々備えた複数の半導体チップと、出力部の各々と接続された配線と、配線を介して複数の半導体チップの各々からデータを受け付ける受付部と、を含み、出力部が順番に駆動する半導体装置にて、出力部の各々は、オン状態時の抵抗値を変更可能であり、自己の駆動開始時から自己の次に駆動を開始する出力部の駆動開始時の前のタイミングまでの第1期間の間は、オン状態時の抵抗値を第1抵抗値にしてデータを配線に出力し、第1期間が経過した時点から自己の駆動終了時までの第2期間の間は、オン状態時の抵抗値を第1抵抗値よりも大きい第2抵抗値にしてデータを配線に出力する。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

半導体装置

【課題】 本実施形態は、出力ドライバのドライブ能力のキャリブレーション精度を向上することが可能な半導体装置を提供する。

【解決手段】 第1、第2のプルアップドライバユニットPUDUa、PUDUbは、プルアップドライバを調整する。プルダウンドライバユニットPDDUbは、プルダウンドライバを調整する。キャリブレーション回路CBCは、プルアップドライバのキャリブレーション時、基準電圧VREFと、基準抵抗RZQに基づく第1のプルアップドライバの出力電圧を比較して第1、第2のプルアップドライバユニットのドライブ能力を決定し、プルダウンドライバのキャリブレーション時、基準電圧と、第2のプルアップドライバとプルダウンドライバの接続ノードの電圧を比較してプルダウンドライバのドライブ能力を決定する単一の比較器COMPを有している。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

出力回路及びそのドライブ能力テスト方法。

【課題】容量性負荷が外部端子に接続されている場合でも、出力バッファのドライブ能力の診断が可能な出力回路とテスト方法を提供する。

【解決手段】外部負荷が接続される第1、第2の外部端子と、前記第1、第2の外部端子に接続される前記外部負荷を駆動する出力バッファ部と、第1の制御信号に応じてオン状態となることで、前記第1、第2の外部端子を導通させるスイッチ部と、テスト時において、前記出力バッファ部により、前記第1、第2の外部端子に対して互いに逆相の信号を出力させ、且つ、前記第1の制御信号により前記スイッチ回路をオン状態とするテスト制御部と、を有する出力回路。

(もっと読む)

半導体装置

【課題】 動作試験用の外部抵抗素子を用意することなくZQキャリブレーション回路の動作試験を行える半導体装置を提供する。

【解決手段】 半導体装置は、外部端子と、外部端子に接続され、当該外部端子に接続される外部抵抗素子を利用してキャリブレーションを行うキャリブレーション回路と、内部抵抗素子と、内部抵抗素子と外部端子との間に設けられたスイッチと、を備える。外部端子に外部抵抗素子が接続されていない状態で、スイッチを導通状態にして内部抵抗素子をZQ端子に電気的に接続する。これにより、外部抵抗素子に代えて内部抵抗素子を利用してキャリブレーションを行うことができる。

(もっと読む)

リンギング抑制回路

【課題】簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、PチャネルMOSFET4及びNチャネルMOSFET5の直列回路を接続し、制御回路11は、差動信号のレベルがハイからローに変化したことを検出すると、PチャネルMOSFET4及びNチャネルMOSFET5を同時に一定期間オンさせる。これにより、差動信号のレベルが遷移する期間に信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーをFET4及び5のオン抵抗により吸収させてリンギングの発生を抑制する。

(もっと読む)

差動入力バッファ

【課題】動作モード切り換え時におけるノイズを抑制する。

【解決手段】差動入力バッファ1は、動作モードを通常状態又は省電力状態のいずれかに切り換える電源回路MN1,MN2と、ソースフォロア回路を構成する半導体素子MP1,MP3及びMP2,MP4のそれぞれの寄生容量の合計である第1の寄生容量に対応する第2の寄生容量を有する半導体素子MP7,MP8により構成されるダミー回路とを有し、動作モードの切り換え時に第1の寄生容量に起因して発生する電流の流通方向と、動作モードの切り換え時に第2の寄生容量に起因して発生する電流の流通方向とが共通の配線において相反する構成を有する。

(もっと読む)

半導体装置

【課題】 待機動作時のオフリーク電流を削減した論理回路を含む半導体装置を提供することを目的とする。

【解決手段】 半導体装置100は、第1の動作電圧または第1の動作電圧よりも小さい第2の動作電圧を供給する電源供給部110と、電源供給部110から第1または第2の動作電圧を受け取る低しきい値のP型トランジスタTpと、トランジスタTpと基準電位との間に接続されたN型トランジスタTnとを有し、トランジスタTp、Tnは、ゲートに入力された信号Dinに応じて出力信号Doutを生成する論理回路を構成する。電源供給部110は、通常動作時、第1の動作電圧をトランジスタTpのソースに供給し、待機動作時、第2の動作電圧をトランジスタTpのソースに供給する。第2の動作電圧は、トランジスタTp、Tnそれぞれのゲート・ソース間電圧の振幅がトランジスタTp、Tnのしきい値よりも大きくなるように設定される。

(もっと読む)

21 - 40 / 879

[ Back to top ]