Fターム[5J056FF07]の内容

Fターム[5J056FF07]に分類される特許

41 - 60 / 879

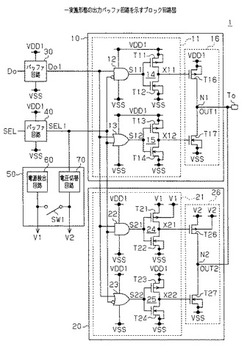

出力バッファ回路及び入出力バッファ回路

【課題】流入電流の発生を抑制することができる出力バッファ回路を提供する。

【解決手段】出力バッファ回路1は、第1の高電位電源VDD1レベル又は低電位電源VSSレベルの出力信号OUT1を出力する第1出力回路10と、第1出力回路10とワイヤードオア接続され、第1の高電位電源VDD1よりも低電位である第2の高電位電源VDD2レベル又は低電位電源VSSレベルの出力信号OUT2を出力する第2出力回路20とを有している。また、出力バッファ回路1は、第1の高電位電源VDD1及び第2の高電位電源VDD2のうち第2の高電位電源VDD2のみが投入される場合に、第1出力回路10の高電位側の第1出力トランジスタT16及び第2出力回路20の高電位側の第2出力トランジスタT26の少なくとも一方のトランジスタのゲート電圧及びバックゲート電圧を第2の高電位電源VDD2レベルに設定する制御回路50を有している。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

回路装置及び回路装置の制御方法

【課題】プルアップ電流を増加することなく、オープンドレイン接続の信号ラインのスルーレートを向上させる。

【解決手段】オープンドレイン若しくはオープンコレクターの出力端子を駆動する出力回路と、前記出力回路を制御する制御回路と、を含み、前記制御回路は、前記出力回路が前記出力端子にローレベルを出力しない期間において、前記出力端子がローレベルからハイレベルに遷移する場合に前記出力回路が前記出力端子にハイレベルを出力する制御を行うことを特徴とする。

(もっと読む)

集積回路及び集積回路の制御方法

【課題】回路若しくは装置が、仕様或いは規格に適用しない部分があったとしても、使用することに問題がない場合の対応方法のひとつを提供する。

【解決手段】集積回路が入出力回路とタイミング測定回路とを含み、前記入出力回路の第1の入力端子に入力される第1の信号と、前記入出力回路の第1の出力端子から出力される第2の信号とが前記タイミング測定回路に入力され、前記第2の信号は、前記入出力回路の第1の入出力端子における信号が前記第1の出力端子から出力されたものであり、前記タイミング測定回路において、前記第1の信号における第1の変化を検出し、前記第2の信号における前記第1の変化に対応する第2の変化を検出し、前記第1の変化を検出したときと前記第2の変化を検出したときとの間の時間間隔の計測を行うことを特徴とする。

(もっと読む)

半導体装置

【課題】スタンバイ時のリーク電流と回路面積の増大を抑制する。

【解決手段】第1電源に接続する第1の回路11の入力対に出力が夫々接続された第2及び第3の回路12、13と、前記第1の回路の入力、又は、前記第1の回路の内部ノードに接続された第4の回路14と、を含み、前記第2の回路及び前記第3の回路は、第2電源と第3電源間に接続され、スタンバイ時にパワーゲーティングされる回路を有し、前記第2の回路は、前記第2及び第3電源電位を振幅範囲とする信号を入力し、前記第2の回路の出力は前記第3の回路の入力に接続され、前記第1の回路の出力信号の振幅範囲は、前記第1電源電位と、前記第2又は第3電源電位とされ、前記第4の回路は、パワーゲーティング時に前記第1の回路の前記入力対、又は前記内部ノードの論理値を保持し、スタンバイ時にも前記第1の回路の出力信号の論理を前記入力信号に関連した論理に維持する。

(もっと読む)

半導体集積回路装置

【課題】 集積回路における時間的に変動するばらつきを検出する回路を提供する。

【解決手段】 集積回路内に検出回路100、演算回路101、ばらつき/電圧変換回路113とを設ける。検出回路100において集積回路の特性ばらつきを検出回路100の出力信号の発振周波数として検出する。演算回路101では、タイマ106にて規定した時間間隔毎に検出したばらつき情報をレジスタ111に格納し、統計演算回路112にて統計処理を施し、集積回路の時間的に変動する特性ばらつきを検出する。更に、ばらつき/電圧変換回路113は、検出された特性ばらつきに対応した電圧情報に変換する。

(もっと読む)

入出力回路

【課題】回路規模の増大を抑制しながら、コネクタに接続されたチャージャーの種類を的確に認識する。

【解決手段】電源検出回路12は、VBUS端子への外部からの給電を検出する。チャージャー検出回路14は、DP端子およびDM端子の電圧を検出することにより、チャージャーの種類を特定する。チャージャー検出回路14は、DP端子およびDM端子の少なくとも一方のオープン、プルアップ、プルダウンまたは両端子間のショートを検出する。

(もっと読む)

差動出力バッファ

【課題】本発明は、差動データ信号の変化を強調した強調済み差動データ信号を出力する差動出力バッファに関し、負荷容量や回路構成を大きく増やすことなく複数段にわたる高精度な強調を可能にする。

【解決手段】差動データ信号VIN,VIN_Bと、差動データ信号を所定の時間だけ遅延し、反転した、反転遅延差動データ信号EVIN_B,EVINとを、所定の比率で混合した、混合差動データ信号VB1,VB2を生成する混合回路12を有する混合段10Aと、複数の差動増幅等の組合せからなる出力段20Aとを備え、混合段10Aが、所要の強調量に応じて、混合回路12での差動データ信号と反転遅延差動データ信号との混合比を1:0、1:1、0:1のいずれかに設定する混合比設定回路を含む。

(もっと読む)

レベル変換バススイッチ

【課題】レベル変換時の信号の立ち上がりを速くすることのできるレベル変換バススイッチを提供する。

【解決手段】実施形態のレベル変換バススイッチは、低電圧レベル信号が伝送される低電圧レベル信号線と高電圧レベル信号が伝送される高電圧レベル信号線との間に、低電圧レベルの制御信号により導通が制御されるMOSトランジスタ型のスイッチ1が接続され、高電圧レベル信号線と高電圧電源線VccBとの間に、プルアップ抵抗2が接続される。このレベル変換バススイッチでは、加速回路3が、高電圧レベル信号の立ち上がりをプルアップ抵抗2による立ち上がりよりも速くし、加速期間制御回路4が、加速回路3の作動期間を制御する。

(もっと読む)

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

演算およびスリープ・モード中のデータ格納回路並びに方法

【課題】スリープ・モード中に信号を格納するための回路を提供する。

【解決手段】スリープ信号を受け取るスリープ信号入力と、クロック信号を受け取るクロック信号入力と、クロック信号でクロックされる複数のラッチと、クロック信号でクロックされるトライステート素子であって、トライステート素子は1つの入力に、少なくとも1つの格納ラッチが接続され、格納ラッチは複数のラッチの1つであり、トライステート素子は格納ラッチの入力を、予め定められたクロック信号値に応答して選択的に分離するトライステート素子とを含み、回路への電源供給が、スリープ信号に応答して、回路の少なくとも1部の電圧差が低減されて回路の部分の電源が遮断され、格納ラッチに掛かる電圧差が維持され、トライステート素子で受け取られるクロック信号が予め定められた値に保持されて、格納ラッチの入力が分離される。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

不揮発性メモリ用の高速ファンアウトシステムアーキテクチャおよび入出力回路

【課題】 不揮発性メモリ用の高速ファンアウトシステムアーキテクチャおよび入出力回路を提供する。

【解決手段】 さまざまな実施形態において、複数の不揮発性メモリデバイス、例えばNANDフラッシュメモリデバイスが、ファンアウト構造でホストコントローラデバイスに接続され得る。ファンアウト構造によると、各メモリデバイスは読み出し動作および/または書き込み動作を同時に実行できる。各不揮発性メモリデバイスは、高速入力回路および高速出力回路を有し得るので、メモリとの間のデータ転送は、フラッシュメモリ読み書きインターフェースの速度に制限されない。

(もっと読む)

半導体装置

【課題】リーク電流を従来よりも抑えること。

【解決手段】本発明の半導体装置1は、外部から信号を供給可能な入力端子10と、内部回路30と、制御部40と、バッファ回路20とを具備している。制御部40は、起動時から所定時間が経過するまでの間にマスク解除信号MASK“H”を出力する。バッファ回路20は、入力端子10に供給される電圧VDD又は電圧GNDを表す信号をマスク解除信号MASK“H”に応じて内部回路30に出力する。本発明の半導体装置1では、外部から入力端子10に信号が供給されているときにノイズが発生しても、バッファ回路20が入力端子10から内部回路30への伝送を有効にする時間以外は無効にしている。このため、マスク回路26によるバッファ回路20と内部回路30との切り離しにより、内部回路30への貫通電流を防止することができる。

(もっと読む)

双方向レベルシフト回路

【課題】高速に信号の伝達が可能な双方向レベルシフト回路を提供する。

【解決手段】実施形態によれば、第1の回路と、第2の回路と、第3の回路と、第4の回路と、を備えた双方向レベルシフト回路が提供される。前記第1の回路は、双方向に信号を伝達する。前記第2の回路は、前記第1の回路の両端の電位の変化に基づいて前記第1の回路の伝達方向を検出する。前記第3の回路は、前記第1の回路の両端の電位のいずれかがローレベルからハイレベルに上昇してから、前記第1の回路の両端の電位のいずれもがハイレベルになるまでの第1の期間を検出する。前記第4の回路は、前記第1の回路の両端にそれぞれ接続され、前記第1の回路の出力側に前記第1の期間ハイレベルの電位を供給する。

(もっと読む)

41 - 60 / 879

[ Back to top ]