Fターム[5J106CC37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598)

Fターム[5J106CC37]の下位に属するFターム

Fターム[5J106CC37]に分類される特許

41 - 60 / 65

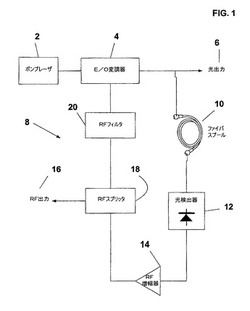

光学的分配回路網を有する光電気発振器クロック

【課題】スキューおよびジッター等が低減されたクロック信号の分配システムおよび方法を提供する。

【解決手段】クロック信号を必要とするコンポーネントを含む電子システム用のクロック回路は、光クロック出力(6)において光クロック信号を発生するための光電気発振器(4)と、光クロック出力(6)を光電気発振器(4)に結合し戻すフィードバックループ(8)とを備える。

(もっと読む)

PLL回路、デッドロック状態復旧方法、および信号処理装置

【課題】PLL回路内部で、デッドロック状態を復旧させることがができるようにする。

【解決手段】セレクタ63は、位相検出回路61からの位相誤差(PExGain)および最長反転間隔検出回路62からのTMAX固定値のどちらか一方を選択し、制御情報として、セレクタ65に出力する。セレクタ65は、デッドロック検出回路66からのデッドロック検出フラグに基づいて、セレクタ63からの制御情報およびPE微分成分計算回路64からの位相誤差の微分成分のどちらか一方を選択し、セレクタ後制御情報として、セレクタ67に出力する。本発明は、記録媒体より読み出される再生信号に対して信号処理を行う信号処理装置を含む再生システムに適用できる。

(もっと読む)

クロック位相シフト装置

【課題】PLL回路を使用してクロックの位相をずらすクロック位相シフト装置において、PLLロック外れを発生しにくくする。

【解決手段】水晶発振器100の出力クロックC100を入力する第1段のPLL回路201、およびこの第1段のPLL回路の出力クロックC201を入力する第2段のPLL回路202を備え、前記第2段のPLL回路の出力クロックC202が前記第1段のPLL回路に前記水晶発振器の出力クロックと比較する入力クロックとして入力され、前記第2段のPLL回路の出力クロックC202が外部への出力クロックとして取り出されるクロック位相シフト装置。

(もっと読む)

移相発振器およびアンテナ

本発明は、新しい改善された移相注入発振器、移相注入同期プッシュ・プッシュ発振器、およびフェーズド・アレイ・アンテナ(PAA)について説明する。本発明の例示的な実施形態によるPAAは低コストであるため、種々の商業用途、例えば、無線通信または衛星モバイル・テレビにおいて用いることができる。 (もっと読む)

主にデジタルな時間基準発生器を使用する信号完全性測定のシステム及び方法

1以上の被テスト信号のサンプリングを制御するための、独自の時間基準発生技法を利用する信号完全性測定のシステム及び方法である。本開示に従い作成した時間基準発生器は、位相フィルタ及び変調回路を備えており、これらは、シグマデルタ変調器の出力の関数として、高速に変化する位相信号を発生させるものである。この位相フィルタは、該高速に変化する位相信号から所望でない高い周波数の位相成分をフィルタする。フィルタされた該信号は、1以上のサンプラをクロックするために使用され、それによって上記の被テスト信号のサンプリングの事例を生成する。次に、これらサンプリングの事例を、被テスト信号の種類に適した何らかの1以上の様々な技法を使用して分析する。 (もっと読む)

電圧制御発振器

【課題】部品点数を削減し、回路規模を低減させることが可能な電圧制御発振器を提供すること。

【解決手段】本発明にかかる電圧制御発振器は、発振回路(2)と、複数の共振回路(5,6)と、前記複数の共振回路のいずれか1つを選択的に前記発振回路と接続させる切り替え手段(4)と、を備える。ここで、各共振回路は、例えば、所定の共振周波数に対応するLC共振回路と当該共振周波数を制御する可変容量ダイオードと、を含んで構成される。

(もっと読む)

周波数推定方法、広帯域周波数弁別器及び無線位置測定用受信機

【課題】 サンプリング周波数の2倍の周波数における回転因子の集合に対応する、DFT演算子と1/2DFT演算子の組み合わせにもとづく周波数弁別器である。

【解決手段】 周波数弁別器は、ゼロ又は不連続点を持たないように選定される。そのため、この発明の弁別器は、拡張された動作範囲において、より安定的かつ良好に動作する。この発明の弁別器は、GPS受信機に適用された場合、初めに大きな誤差が有っても、より確実にキャリヤ周波数にロックすることが可能であるとともに、誤ってロックする問題を防止するものである。

(もっと読む)

発振回路とこれを用いたPLL発振回路とこのPLL発振回路を用いた高周波受信装置

【課題】所定の周波数変化範囲を確保しながら、位相雑音特性を改善する。

【解決手段】差動タイプの増幅器54,55で構成された発振部52と、この発振部52の出力端子52b,52cに入力端子53a,53bがそれぞれ接続された同調部53からなる発振回路51において、同調部53は、可変容量素子74,75とインダクタンス72,73からなる並列接続回路とを備え、可変容量素子74に制御電圧を供給する制御端子53cと可変容量素子75に制御電圧を供給する制御端子53dとをそれぞれ独立に設け、制御端子53dに供給する制御電圧による発振周波数の変化量の方が、制御端子53cに供給する制御電圧による発振周波数の変化量より小さく設定した。

これにより、所期の目的を達成することができる。

(もっと読む)

位相同期ループ回路及びこの位相同期ループ回路の制御方法

【課題】電圧制御水晶発振器の経年変化による異常が発生しても、この異常を確実に検出できるようにした位相同期ループ回路を提供する。

【解決手段】カウンタ111にて外部クロック信号から内部クロック信号に同期した矩形波信号を生成するとともに、カウンタ112−2にて内部クロック信号から外部クロック信号の異常を検出するために必要なウインドウ信号W1を生成し、カウンタ115にて内部クロック信号から電圧制御水晶発振器12の異常を検出するために必要なウインドウ信号W2を生成し、異常判定制御部114−2にて矩形波信号の立ち上がりがウインドウ信号W1,W2のハイレベル期間内に入っているか否かを判定し、ウインドウ信号W1のハイレベル期間に入っていて、ウインドウ信号W2のハイレベル期間内に入っていない場合に、電圧制御水晶発振器12の異常と判定するようにしている。

(もっと読む)

PLL回路

【課題】複数の位相誤差出力をもつ特殊なVCOを備えること無しに、間欠的に記録され、データの先頭部に同期引き込みパターン領域を有するデータに対し、高速での引き込みを可能とするPLL回路を提供する。

【解決手段】PLL回路において、ADコンバータ4と、ADコンバータ4の出力信号から位相誤差を算出する位相比較器5と、周波数系フィルタ6と、位相系フィルタ7と、所定のタイミングで位相比較器5で算出された位相誤差の読み取りを行い、その読み取り値に応じた出力を発生する位相誤差読み取り手段8および位相誤差変換手段9と、周波数系フィルタ6の出力、位相系フィルタ7の出力、および位相誤差変換手段9の出力を加算する加算器10と、DAコンバータ11と、DAコンバータ11の出力電圧に基づいてADコンバータ4のサンプリングクロックとして使用される発振出力を出力するVCO12とを備えた。

(もっと読む)

周波数変調器およびこれを用いたFM送信回路

【課題】PLLのループフィルタが変調信号におよぼす影響を抑える。

【解決手段】演算増幅器10は、反転入力端子に第1抵抗R1を介して入力信号が入力される。第2抵抗R2は、演算増幅器10の出力端子と反転入力端子間の帰還経路に設けられる。VCO12は、演算増幅器10から出力される制御電圧Vcntが入力される。分周器14は、VCO12の出力信号Soutを分周する。位相比較器16は、分周器14の出力信号を、基準クロック信号と比較し、位相差に応じた電圧を出力する。ループフィルタ18は、位相比較器16の出力電圧Vcpの高周波成分を除去し、演算増幅器10の非反転入力端子へと出力する。

(もっと読む)

シンセサイザモジュール

【課題】PLL回路用接地パターン領域7と広域接地パターン11間に基準信号除去用フィルタ4を接続し、電圧制御発振器1への基準信号の回り込みをなくしたシンセサイザモジュールを提供する。

【解決手段】絶縁基板5上面に、電圧制御発振器1及びPLL回路2を装着すると共に電圧制御発振器用接地パターン領域6及びPLL回路用接地パターン領域7を形成し、絶縁基板5下面に広域接地パターン11を形成したもので、絶縁基板5上面にさらにPLL回路の基準信号除去用フィルタ4を装着し、フィルタ用接地パターン領域10を形成し、フィルタ4をPLL回路用接地パターン領域7とフィルタ用接地パターン領域10間に接続し、フィルタ用接地パターン領域10を広域接地パターン11に導電接続した。

(もっと読む)

電力を節約するためのトライステート型位相同期ループ

その周波数が位相同期ループ(PLL)によって制御されかつ間欠的に動作している無線部を備えるシステムにおいて、PLLが設計周波数において安定した後に、PLL内の制御コンデンサをトライステートにすることによって、PLLによって消費される電力を低減する方法及びシステムを提供する。前記コンデンサが安定した後に、PLL内の構成要素のうちのいくつかへの電力が低減される。 (もっと読む)

送受信機の周波数合成の方法および装置

【課題】受信機参照周波数信号から受信機周波数信号を合成するように構成されるプライマリ周波数シンセサイザを提供し、フラクショナル−N分周を使用することにより受信機周波数信号から送信機周波数信号を合成するように構成されるオフセット周波数シンセサイザを提供することに基づく、送受信機の周波数合成に関する方法および装置である。かかる構成が、要求される受信および送信周波数間の非整数のデュプレックス距離を可能とする。プライマリ周波数シンセサイザは、フラクショナル−N周波数シンセサイザとして作動されることもできる。これは受信機周波数信号が受信機参照周波数信号との非整数の関係を有することもできることを意味する。フラクショナル−N周波数合成と共に作動するようにプライマリおよびオフセット周波数シンセサイザを構成することが、プライマリおよびセカンダリ周波数シンセサイザの独立した周波数の調整/最適化を許容する。 (もっと読む)

信号処理装置、信号処理方法

【課題】デジタルPLLのループ遅延の短縮化と、そのデジタルPLLによって位相同期が取られた再生データの高精度化とを両立させる。

【解決手段】ビタビ検出用の位相補間フィルタ9と、PLL8にある位相誤差検出用の位相補間フィルタ81とを設ける。位相オフセット演算器84において位相誤差の積算値である位相オフセット量φに応じて、位相補間フィルタ9および位相補間フィルタ81では、タップ係数が逐次更新されるが、位相補間フィルタ81は、位相補間フィルタ9と比較して、タップ数/ビット幅が小さく設定され、PLL8内のループ遅延時間を短縮する。

(もっと読む)

回路、制御システム、IC、送受信装置、制御方法およびプログラム

【課題】 位相誤差を小さくでき、かつ高周波ジッタ成分および低周波ワンダ成分を同時に抑圧することができる回路、制御システム、IC、送受信装置、制御方法およびプログラムを提供する。

【解決手段】 高周波ジッタ抑圧部であるPLL1部100と、低周波ワンダ抑圧部であるPLL2部200と、再生クロック部であるPLL3部300をマルチループ・シンセサイザ構成とする。

(もっと読む)

クロック・データリカバリ回路

【課題】 外部から高速な参照クロックを入力することなく、回路の安定性が高められたクロック・データリカバリ回路を提供する。

【解決手段】 入力データDataInの立ち下がりエッジと、遅延部10に配列された各1ビット遅延素子11の出力データD1,D2,D3,D4,D5の立ち上がりエッジとの位相を位相比較部20で比較し、その位相比較結果に基づいて遅延部10に配列された各半ビット遅延素子の遅延量をチャージポンプ・ループフィルタ30で調整し、調整された複数の半ビット遅延素子の出力データD0h,D1h,D2h,D3h,D4hに基づいて、入力データDataInの入力周期と同期した周期のクロックRCKをクロック生成部40で生成し、フリップフロップ50でクロックRCKを用いて入力データDataInを取り込む。

(もっと読む)

クロック生成回路

【課題】 工数の削減を図りつつ、PLL回路のジッタ精度を安定化させるために用いられるフィルタ回路のフィルタ係数を調整できるようにする。

【解決手段】 PLL回路2を半導体チップ1に形成するとともに、フィルタ係数を切り替え可能なフィルタ回路3、フィルタ回路3のフィルタ係数を切り替えるスイッチング素子4およびスイッチング素子4をオン/オフするための信号を保持するレジスタ5を形成し、フィルタ回路3のフィルタ係数が最適化されるようにスイッチング素子4をオン/オフさせるための信号をレジスタ5に設定し、レジスタ5に設定された信号に基づいてスイッチング素子4をオン/オフさせることにより、フィルタ回路3のフィルタ係数を調整する。

(もっと読む)

PLL変調器、通信機器、及び移動無線機

【課題】 アナログフィルタを除去してもノイズを除去できるような構成にすることにより、広帯域変調が可能なPLL変調器を小型かつ低コストで提供する。

【解決手段】 PLL変調器は、分周器4に分周比変調をかける第1の変調ルートと、VCOに直接変調をかける第2の変調ルートとの2点変調を行う。第2の変調ルートにおいて、D/A変換器6の前段にループフィルタ2の逆周波数特性を有するプリエンファシスフィルタ7を設ける。これにより変調信号の帯域幅が制限されないようにする。さらに、D/A変換器6からの変調信号S10をPLL部10におけるループフィルタ2の前段の加算器9へ印加する。これにより、D/A変換器6で発生するノイズをループフィルタ2で抑圧した変調信号S3をVCO3へ供給する。この構成により、D/A変換器6の後段のアナログフィルタを除去し、ディジタルのプリエンファシスフィルタを設置できる。

(もっと読む)

デュアルループPLLおよび逓倍クロック発生装置

【課題】 初期起動においてロックアップ時間を短縮できるデュアルループPLL(Phase Looked Loop)を提供すること、および消費電力低減に寄与する逓倍クロック発生装置を提供すること。

【解決手段】 デュアルループPLLは、位相を比較する位相比較器1を有する位相比較ループと、周波数を比較する周波数比較器7を有する周波数比較ループとを有するデュアルループPLLを備え、周波数比較器7は、位相比較器1に用いる、外部基準クロックラインCLex11から入力される基準クロック信号と異なる、キャリブレーションクロックラインCLcal18から入力される入力信号を用いて周波数比較を行う。また、上記デュアルループPLLを用いて、逓倍クロック発生装置を構成する。

(もっと読む)

41 - 60 / 65

[ Back to top ]