Fターム[5J106CC47]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | デジタル型 (163) | D/A変換器出力型 (31)

Fターム[5J106CC47]に分類される特許

1 - 20 / 31

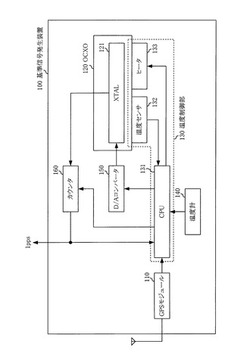

基準信号発生装置および基準信号発生方法

【課題】基準信号発生装置全体の消費電力を削減する。

【解決手段】OCXO120が、GPSモジュール110が同期信号を受信している間、当該同期信号を用いて基準信号を発生し、GPSモジュール110が同期信号を受信していない間は、あらかじめ設定された値を用いて基準信号を発生し、温度制御部130が、GPSモジュール110が同期信号を受信している間、OCXO120の温度を所定の温度よりもあらかじめ設定された温度だけ高い温度で変化させ、GPSモジュール110が同期信号を受信していない間は、OCXO120の温度をGPSモジュール110が同期信号を受信しなくなった際の温度に固定させる。

(もっと読む)

送受信装置

【課題】構造簡単な距離を測定可能とした送受信装置の実現

【解決手段】第1信号の受信と第2信号の送信とを共通化した送受信アンテナ20と、第1信号を復調して第1パルス信号を得る復調器30と、制御信号を入力して目標周波数を設定する目標周波数設定レジスタ61と目標位相を設定する目標位相設定レジスタ66とを有し、目標周波数設定レジスタに設定されている目標周波数と目標位相設定レジスタに設定されている目標位相とに一致した周波数と位相の第2パルス信号を出力するパルス発振器60を有する。第2パルス信号により搬送波を変調する変調器70と、第1パルス信号と、第2パルス信号との位相差を検出する位相比較器32を有する。また、位相差信号の時間変動からその時の第1パルス信号と第2パルス信号との周波数差をもとめ、その周波数差に基づいて目標周波数を制御する周波数制御装置と、位相差信号の示す位相差に基づいて目標位相を制御する位相制御装置とを有する。

(もっと読む)

ダイレクト・デジタル・シンセサイザ回路

【課題】 正弦波ROMテーブルのメモリ規模を増大させることなく、位相誤差を低減できるダイレクト・デジタル・シンセサイザ回路を提供する。

【解決手段】 周波数設定データをデータ分離部1で上位ビットと下位ビットに分離し、位相内挿補正値出力部10が下位ビットの累積によるオーバーフローで補正パラメータ1を出力し、下位ビットの積分値から得られた補正値を補正パラメータ2として出力し、上位ビットのデータに補正パラメータ1を正弦波ROMアドレス生成部2で加算して積分して正弦波ROMテーブル5で対応する正弦波の同相成分と直交成分を出力し、位相内挿補正部6で直交成分に補正パラメータ2を乗算し、同相成分との差分を演算することで、位相補正を行うDDS回路である。

(もっと読む)

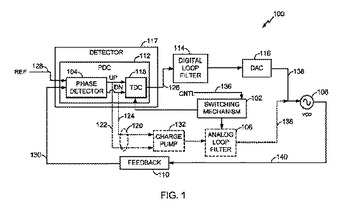

設定可能なデジタル−アナログ位相ロックループ

位相ロックループ(PLL)デバイスは、アナログ位相ロックループおよびハイブリッドアナログ−デジタル位相ロックループ内で構成可能である。アナログモードでは、少なくとも位相検出器、アナログループフィルタおよび電圧制御発振器(VCO)はアナログループを形成するために接続される。デジタルモードでは、少なくとも前記位相検出器、前記電圧制御発振器(VCO)、時間−デジタルコンバータ(TDC)、デジタルループフィルタおよびデジタル−アナログコンバータ(DAC)は前記ハイブリッドデジタル−アナログループを形成するために接続される。  (もっと読む)

(もっと読む)

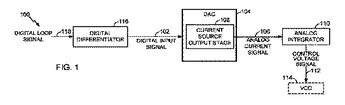

アナログ積分のためのデジタル補償を有するフェイズロックループ

フェイズロックループ(PLL)デバイスは、アナログ積分器によるアナログ電流信号の積分を少なくとも部分的に補償するために、デジタルループ信号を微分するように構成されたデジタル微分器を含む。デジタルアナログコンバータ(DAC)は、デジタル入力信号に基づいてアナログ電流信号を発生する電流源出力ステージを含む。アナログ積分器は、アナログ電流信号を積分して、電圧制御発振器(VCO)を制御するための電圧制御信号を発生する。  (もっと読む)

(もっと読む)

デジタルPLL回路とその制御方法

【課題】比較的簡易な回路構成で、制御時定数を短くしても超高安定な位相同期を実現する。

【解決手段】基準クロックを1/m分周器12で1/m倍し、VCXO11で発生される発振クロックを1/n分周器13で1/n倍し、両クロックを量子化位相比較器14に送り、両クロックのずれ量に相当する量子化位相差δを取得して予測制御器15に送る。予測制御器15では、入力された量子化位相差を、その極性が負から正に反転してから再び負に反転するまで、または正から負に反転してから再び正に反転するまで積分し、この積分値に-0.5倍〜-0.05倍の予測係数を掛けた値を予測重み値として求め、この予測重み値を積分値に加算して制御電圧値を予測する。この予測制御器15で予測された制御電圧値を、D/A変換器16でアナログ電圧に変換し、LPF17によって決まるループ時定数でフィルタリングして、周波数制御電圧としてVCXO11に送る。

(もっと読む)

冗長PLL回路

【課題】本線系と冗長系との間に生じる出力位相の偏差を抑圧し、出力切替時に出力位相の変化を抑える。

【解決手段】基準クロックによるリファレンス信号から1/n(nは任意の自然数)倍の第1の周波数信号を生成する1/n分周器11と、それぞれVCXO121,131の出力信号から1/m(mは任意の自然数)倍の第2の周波数信号を生成して1/n分周器11で生成される第1の周波数信号と位相比較し、その位相比較結果に基づいてVCXO121,131の出力周波数を制御するPLL回路部11,12と、PLL回路部11,12の出力を選択的に導出する出力選択スイッチ14とを具備する。

(もっと読む)

周波数シンセサイザ

【課題】位相雑音を改善することのできる周波数シンセサイザを提供すること。

【解決手段】周波数設定部により設定された周波数の正弦波信号を設定信号出力部からディジタル信号として出力し、これをD/A変換する。ここから出力された正弦波信号と電圧制御発振部の出力周波数に対応する周波数の正弦波信号と、前記D/A変換部からの正弦波信号と、の差分を差動増幅器で増幅し、増幅された信号をA/D変換部を介して、既述の両正弦波信号の位相差を取り出す手段に入力する。この位相差を積分した信号に相当する電圧を電圧制御発振器に制御電圧として入力する。そして差動増幅器の利得をA/D変換部の位相雑音劣化の最大値よりも大きく設定し、これによりA/D変換部の位相雑音劣化をキャンセルする。

(もっと読む)

クロック供給システム

【課題】基準クロックが異常であるのか、電圧制御発振器が異常であるのか故障原因を特定することが可能なクロック供給システムを提供する。

【解決手段】現用系のシステム200のVCXO203の制御値Xがα<X<βにあるかを監視し、その範囲から外れた時に異常を検出する。この異常検出時にVCXO203の制御値を予め決められた制御値γに設定し、現用系のシステムで運用する。また、この運用状態で予備系のシステム210のVCXO213の制御値X’がα’<X’<β’にあるかを判定し、その範囲内にある場合には基準クロック2aの異常と判定し、現用系のまま運用する。一方、その範囲内から外れている場合には現用系のVCXO203が異常と判定し、予備系のシステムに切り替えを行う。

(もっと読む)

クロック供給装置

【課題】運用系および待機系システムクロックの位相を、バックボード間の配線遅延量、温度変化および電圧変動に起因するバッファ遅延の変化量を含め一致させたシステムクロック供給装置を提供する。

【解決手段】システムクロック1に位相同期した運用系および待機系システムクロック6を出力する冗長構成とされた運用系および待機系システムクロック供給部200と運用系および待機系システムクロックを装置内各部へ分配するためのバックボード8を有する。システムクロック1に位相同期したクロック22を生成するPLL210は、運用系システムクロックを基準とし、待機系システムクロックの位相を制御する位相差調整部211を含んだ構成とする。

(もっと読む)

高性能信号発生

【課題】高性能位相検出器は、プログラムで制御できる周波数および位相を有するデジタル基準信号を生成する局部デジタルオシレータを含む。

【解決手段】位相検出器は、デジタル基準信号とサンプリングされた入力信号の間の位相差を蓄積し、位相誤差の指標を作る。位相検出器は、周波数合成器において用いられ、低位相ノイズおよび正確な位相制御で信号を発生することができる利点がある。さらに、この種類のシンセサイザは、低ジッタのクロックおよび波形を生成するATEシステムおよび他の電子システムにおいて、ビルディングブロックのように用いられる。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広く、かつ消費電力の少ない周波数シンセサイザを提供する

【解決手段】電圧制御発振部1の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルの位相差を取り出して出力周波数の調節に利用するPLLは、出力周波数調節用の第1の位相差検出部71と、周波数引き込み用の第2の位相差検出部74とを備え、前記第1の位相差検出部71の出力に係る信号をディジタル/アナログ変換した結果が予め定めたしきい値を越えたときに、前記第2の位相差検出部74の出力に係る信号をディジタル/アナログ変換する手段105から切り離すと共に、当該第2の位相差検出部74における消費電力を小さくする。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。抵抗回路や容量回路をスイッチングすることなく、自然角周波数ωnとダンピングファクタζをそれぞれ自由に変えることが可能な、新しい位相同期回路が実現される。使用用途に合わせた位相同期回路の選択の幅を広げることができる。

(もっと読む)

位相差補正回路及び位相差補正方法

【課題】現用系と予備系の基準クロックの位相同期の精度を向上させる。

【解決手段】基準クロック供給システムは、現用系のクロック供給回路及び予備系のクロック供給回路の冗長構成で形成され、現用系から第1の基準クロックを供給すると共に予備系から第1の基準クロックに位相同期させた第2の基準クロックを供給する。位相差補正回路は、基準クロック供給システムから第1及び第2の基準クロックを受信する側で第1及び第2の基準クロック間の位相差を測定し、その位相差情報を基準クロック供給システムにフォードバックさせる位相差測定部を有し、位相差情報に応じて、基準クロック供給システムによる第1及び第2の基準クロックの位相同期動作に補正をかける。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】広帯域で量子化雑音及び発振器の位相雑音を除去し、小面積で構成可能な位相同期回路を提供する。

【解決手段】第1の制御信号及び第2の制御信号の組み合わせによって制御される共通の周波数及び互いに異なる位相を夫々持つ第1及び第2の発振信号を生成する制御発振器と;基準信号と第1の発振信号との間の周波数差及び位相差に応じた第1の検出信号を生成するデジタル位相周波数検出器と;第1の検出信号の高周波成分を除去して第1の制御信号を生成するデジタルフィルタと;第2の発振信号と基準信号との間の位相差に応じた第2の検出信号を生成するアナログ位相検出器と;第2の検出信号の高周波成分を除去して、第2の制御信号を出力するアナログフィルタと;アナログ位相検出器及びアナログフィルタを能動状態とするために、基準信号と第1の発振信号の同期を検出する同期検出部と;を具備する。

(もっと読む)

クロック信号生成回路とクロック信号生成方法

【課題】複数系統の基準信号のいずれか、又は全てが断となってしまった場合でも、安定してクロック信号を生成することができるようにする。

【解決手段】断検出部2−A,2−Bで現用系の基準信号Aと予備系の基準信号Bの断を検出するようにし、断検出時には断検出信号を制御部8へ出力する。制御部8は、断検出部2−Aからの断検出信号を受け取ると、入力切替部1の導出を基準信号Bに切り替え、その後、断検出部2−Bからの断検出信号を通知されると、制御電圧保持部6の保持電圧の更新を停止させ、切替部7の導出を制御電圧生成部5で生成される制御電圧から制御電圧保持部6に保持される保持電圧に切り替える。

(もっと読む)

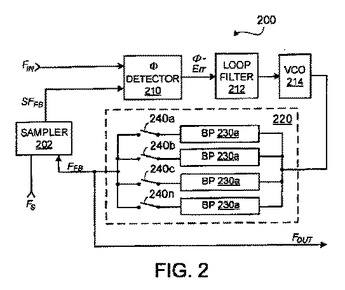

偽信号化された周波数上の位相ロック

位相ロックループ(200)は、サンプラー(202)、位相検出器(210)、ループフィルタ(212)、VCO(214)を含む。ループは、ループのフィードバックパス中に分割器を必要とすることなく周波数逓倍を達成する。VCO(214)は、サンプラーのナイキストレートより上で動作され、ループが偽信号化された信号上にロックすることを引き起こす。VCO出力周波数中のあらゆる変動(即ち、ジッターまたは位相ノイズ)は、周波数分割器に通常関連付けられる減衰無しで、1対1で位相検出器(210)にフィードバックされる。ループゲインは従って、高い閉ループ周波数逓倍を提供するループにおいてでも、高く保つことができる。一変形によると、高調波発生器(540)がVCOとサンプラーの間に置かれ、よってループがVCO周波数の高調波上にロックすることを引き起こす。開ループゲインと精度はよって更に向上される。  (もっと読む)

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

PLL回路及びディスク装置

【課題】温度特性や経時変化がなく、線速度変化に合わせてループ特性をシームレスに補正できるPLL回路を提供する。

【解決手段】デジタルループフィルタ103は、位相比較器102が出力する位相誤差を入力し、デジタル周波数値を生成する。このデジタル周波数値は、D/A変換器104でアナログ電圧に変換され、VCO105は、D/A変換器104が出力する電圧に応じた周波数の同期クロックを出力する。位相比較器102が出力する位相誤差は、デジタルループフィルタ103の出力に所定の係数Aを乗じたものでゲイン補正され、デジタルループフィルタ103に入力される。デジタルループフィルタ103に入力する位相誤差を、出力クロック周波数に比例して変化させることで、PLLループ全体として、出力クロック周波数に依存して線形にループ特性が制御できる。

(もっと読む)

光ディスク装置、クロック生成装置、およびクロック生成方法

【課題】設定発振周波数範囲を自律して切り換える。

【解決手段】光ディスク装置1は、動作クロックの制御値に応じて動作クロックの発振周波数を調節可能であり、制御値の変更により調節可能な発振周波数の範囲を、段階的に異なる複数の設定発振周波数範囲のいずれか1つに切り換え可能である発振器20と、設定発振周波数範囲について、制御値の上限値、当該上限値に対応する制御値の初期値、制御値の下限値、および当該下限値に対応する制御値の初期値が設定されており、制御値が上限値に達した時に一段階上の設定発振周波数範囲に切り換えると共に制御値を当該上限値に対応する初期値に設定し、制御値が下限値に達した時に一段階下の設定発振周波数範囲に切り換えると共に制御値を当該下限値に対応する初期値に設定する発振周波数範囲切り換え回路30と、を有するクロック生成機能を備える。

(もっと読む)

1 - 20 / 31

[ Back to top ]