Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

281 - 300 / 713

PLL回路、並びに通信装置及びその折り返し試験方法

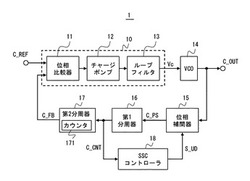

【課題】SSCのジッタを抑制し、SSCの変調度を滑らかに遷移させることが可能なSSC生成機能を有するPLL回路を提供する。

【解決手段】SSCコントローラ18は、SSCの変調プロファイルに応じて予め定められたタイミングで位相シフト量を変更するよう位相補間器15を制御し、出力クロック信号C_OUTの変調度を周期的に変更させる。さらに、SSCコントローラ18は、帰還クロック信号C_FBの一周期内において位相補間器15より出力される位相シフト信号C_PSに与える総位相シフト量を、当該総位相シフト量と直前の一周期における総位相シフト量との差分が常に基本遅延量Δ以下となるよう制御する。ここで、基本遅延量Δは、出力クロック信号C_OUTの周期T_OUTを位相補間器15の位相分解能Nrで除算した値(つまり、T_OUT/Nr)である。

(もっと読む)

PLL回路およびそれを用いた角速度センサ

【課題】本発明は、正確に位相を調整することが可能なPLL回路およびそれを用いた角速度センサを提供することを目的とするものである。

【解決手段】本発明のPLL回路およびそれを用いた角速度センサは、AD変換器21が電圧制御発振器26の出力するタイミング信号により動作し、かつDA変換器24が分周器27の出力するタイミング信号でのAD変換器21の出力する値に応じたアナログ信号を出力する構成としたものである。

(もっと読む)

PLL回路

【課題】消費電力と出力雑音の双方を抑えることができるPLL回路を得ることを目的とする。

【解決手段】PLL回路が、位相比較器1、チャージポンプ2、ループフィルタ3、電圧制御発振器4及び分周器5を備えており、CMOSロジック回路を用いて、分周器5を構成し、バイポーラトランジスタを搭載しているECL回路を用いて、位相比較器1及びチャージポンプ2を構成している。このようにPLL回路を構成することで、消費電力と出力雑音の双方を抑えることができる。

(もっと読む)

位相同期ループの出力VCOにおいて50%デューティサイクルを達成するための方法および装置

【課題】PLLの出力において所望のデューティサイクルを達成するための方法および装置を提供する。

【解決手段】本方法は、制限差動増幅器214を使用して、差動コモンモードクロック信号からデューティサイクルを有するシングルエンドクロック信号を発生させるステップと、シングルエンドクロック信号213のデューティサイクルに応じて差動バイアス電流信号229、230を発生させるステップと、差動バイアス電流信号を制限差動増幅器に与えることによって、シングルエンドクロック信号のデューティサイクルを所望のデューティサイクルに修正するステップとを含む。CML−CMOS変換器回路は、制限差動増幅器214と、シングルエンドクロック信号のデューティサイクルの測定値を発生するための低域フィルタと、(i)測定値を基準電圧と比較し、(ii)比較に応じて差動バイアス電流信号を発生するための第2の差動増幅器とを含む。

(もっと読む)

TDC回路、PLL回路、並びに無線通信装置

【課題】入力信号とトリガ信号の間に遅延時間が存在するというフリップフロップ自身の特性に起因した検出誤差を改善するTDC回路を提供する。

【解決手段】各フリップフロップ105−1、…は、CLKREF、B2からDelay1だけ遅延したタイミングをトリガにして入力信号A0、A1、A2をそれぞれ保持し、データ系列[C0:C3]として“1110”を得る。例えば、[C0:C1]が“11”の場合は遅延量の符号をマイナスとし、[C2:C3]を左から1から0に変化する点をカウントすることでデコードされる。よって、この例では、“−1”とデコードされ、Delay=−Dを検出する。

(もっと読む)

基準信号発生装置

【課題】外部環境による精度低下への影響を低下させ、且つ、ユーザに必要以上の手間を掛けることなく、安定して高精度な基準周波数信号を継続的に出力し続ける。

【解決手段】制御部10は、位相差の平均が、監視閾値未満であるかどうかによって、較正の有無を判定する。ここで、監視閾値は、当該基準周波数信号発生装置1が搭載される通信機器に求められる精度の仕様を満たすとともに、この仕様の限界に対して所定の余裕を持てるような値に設定されている。監視閾値未満の場合、制御部10は、自身で生成した維持用制御電圧信号を電圧制御発振器14へ与え、監視閾値に達する場合、ループフィルタ12からの制御電圧信号を電圧制御発振器14に与え、電圧制御発振器14はこの制御電圧信号に基づいて較正を行う。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

PLL回路

【課題】定常状態で、電圧制御発振器から出力されるクロック信号の周波数の変動を抑えることができるPLL回路を得ることを目的とする。

【解決手段】位相比較器3から出力される矩形波信号の電圧を基準クロック信号fpの周期時間で平均して、その矩形波信号の平均電圧値を出力する平均化器4と、その基準クロック信号frの周期毎に、平均化器4から出力される平均電圧値を読み込んで、その平均電圧値を保持する電圧ラッチ5とを設け、VCO6が電圧ラッチ5により保持されている平均電圧値に応じた周波数f0のクロック信号を出力する。

(もっと読む)

周波数補正システム及び受信機

【課題】製品コストの増大を抑え、水晶発振器の動作のばらつきを防止することが可能な周波数補正システム及び受信機を提供することを目的とする。

【解決手段】誤差読出しタイミング制御部31で設定される読出しタイミングに基づいて、復調部設定レジスタ26から周波数誤差ΔIFをΔIF抽出部34に読み込み、記憶部32に記憶される現在受信中の受信信号の周波数RF及び周波数誤差ΔIFなどに基づいて、水晶発振器6の経年変化による水晶発振器6の発振信号の周波数誤差Δfを算出し、周波数誤差Δfが閾値以上であると判断した場合、現在受信している受信信号のチャンネルに対応する周波数誤差ΔIFを記憶部33から読み出し、その周波数誤差ΔIFに基づいて、チューナ設定レジスタ16及び復調部設定レジスタ26に現在書き込まれている設定値R、Nを更新する。

(もっと読む)

半導体集積回路装置

【課題】PLL回路におけるジッタを低減しながら、ワイドレンジで安定した動作を行う。

【解決手段】PLL回路のオシレータを構成する遅延バッファ7のインバータ13,14は、電流制限用トランジスタであるトランジスタ8を介して電源電流が供給されている。トランジスタ8は、バイアス電流である入力信号in1に応じてインバータ13,14に供給する電流制限する。このトランジスタ8を設けたことにより、発振周波数の低い帯域における該インバータ13,14に流れるリーク電流を防止することができる。

(もっと読む)

分周器

【課題】専用の発振器を用いないボーレート発生器のように分周する周波数の誤差を許容する分周器を簡素な構成かつ高精度で実現する。

【解決手段】分周器としてのボーレート発生器1は、所定の基準クロックRCLKを分周することにより、データをサンプリングするボーレートクロックBCLKを生成する。このボーレート発生器1は、m進/m−1進ダウンカウンタ2と、カウンタ切替制御部3とを備える。m進/m−1進ダウンカウンタ2は、異なる分周比を切り替えて基準クロックRCLKを分周する。カウンタ切替制御部3は、記ボーレートクロックBCLKの正規のボーレートクロックに対する1周期毎の誤差の累積値が所定範囲を超えると、前記累積値が減少するように、m進/m−1進ダウンカウンタ2の分周比を切り替える。

(もっと読む)

電圧制御発振器

【課題】VCO利得の変動を抑圧した簡易な構成のVCOの提供。

【解決手段】二つの周波数可変手段を具備することでマルチバンド動作を行なう電圧制御発振器(VCO)において、可変容量素子11iaと12ia及び11ibと12ib(i=1、2、3)をそれぞれ互いに極性が逆になる向きに並列接続可能とし、可変容量素子対を形成する。一般に、可変容量素子11iaと12ia、11ibと12ib(i=1、2、3)の容量値は異なる値に設定される。これらの可変容量素子対は、ループコントロール端子3に印加されるコントロール電圧VCNTにより制御されると同時に、帯域設定信号VSW1、VSW2、VSW3によってオンオフされるスイッチ素子であるトランジスタ101a、102a、103a、101b、102b、103bの切替により、VCO本体に電気的に分離・接続される。

(もっと読む)

半導体集積回路装置

【課題】ユーザシステムに搭載された状態でクロック信号の異常検出機能の故障診断を可能とする。

【解決手段】第1クロック信号が正常の場合には第1クロック信号に基づいてシステムクロック信号を生成し、上記第1クロック信号が異常の場合には第2クロック信号に基づいてシステムクロック信号を生成するクロック発生部(10)を設ける。そして、演算処理を実行可能なCPU(2)と、上記外部発振器の状態を示す発振状態フラグに基づいて上記CPUに対する割り込み要求信号を形成可能なフラグ設定レジスタ部(9)とを設ける。上記フラグ設定レジスタ部は、疑似発振停止状態イネーブルビット保持部と、上記疑似発振停止状態イネーブルビットがイネーブル状態にされた場合に、上記割り込み要求信号をアサートする制御論理とを含む。上記割り込み要求信号がアサートされることで疑似的な発振停止状態を形成する。

(もっと読む)

クロック及びデータ復元回路

【課題】入力データ論理判定用クロックとして、周波数の安定したクロックを得ることができ、しかも、消費電力を低減することができるCDR回路を提供する。

【解決手段】入力データの論理判定に使用する内部クロックRCKの発生源として電圧制御発振器15を設ける。電圧制御発振器15は、CMOSインバータをリング接続して構成し、常に電流を消費することがないものとする。両エッジ検出部13は、PLL12内の電圧制御発振器21の出力クロックVCO_CKの遷移タイミングを検出し、電圧制御発振器15の発振周波数がPLL12内の電圧制御発振器21の発振周波数と同一となるように電圧制御発振器15を制御する。

(もっと読む)

クロック生成回路

【課題】ロングタームジッタを正確に評価し、回路の誤動作を未然に防ぐ。

【解決手段】第1オシレータ10は、基準クロックCKrefを生成する。PLL回路14は、第1オシレータ10からの基準クロックCKrefにもとづいて出力クロックCKoutを生成する。異常発振監視部20は、基準クロックCKrefを分岐して受け、基準クロックCKrefの周期の整数倍の所定時間経過後にアサートされる基準タイミング信号S1を生成する。異常発振監視部20は、出力クロックCKoutのエッジのタイミングが基準タイミング信号S1のエッジに応じて規定される所定の範囲から逸脱するとき、異常検出信号S2をアサートする。

(もっと読む)

シンボル同期回路

【課題】

シンボル同期回路に於いて、デジタル通信の復調に於ける同期を迅速に精度よく行える様にする。

【解決手段】

電圧制御発振器1と、該電圧制御発振器からの出力を分周する分周器2と、受信信号中の信号変換点を検出し、検出点での前記分周器からの信号をラッチして位相差信号として出力する位相差検出部15,18と、前記位相差信号をフィードバック信号10に変換して前記電圧制御発振器に入力する位相信号変換部4,16,17とを具備する。

(もっと読む)

周波数シンセサイザおよびその制御方法

【課題】周波数シンセサイザがロック状態にあり、かつ、電圧制御発振器の電圧制御信号が一定の電圧範囲からはずれたときに、ロック状態を保ったまま、電圧制御信号を一定の電圧範囲に戻す。

【解決手段】ローパスフィルタ3が生成する制御電圧信号11によって直流バイアス電圧が制御された可変容量ダイオード52の他に補償用可変容量ダイオード53、54を電圧制御発振器5に設け、制御電圧信号11をモニタし、制御電圧信号11の電圧が可変容量ダイオード52の容量を容易に変えられる範囲外の電圧となったときに制御信号16、17のレベルを変化させるモニタ回路8と、その制御信号16、17のレベルの変化をロック状態が解除されないゆっくりとした電圧変化に鈍らせて補償用可変容量ダイオードに直流バイアス電圧を与える時定数回路72とを備える。

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

位相同期ループ回路の制御方法及び位相同期ループ回路

【課題】ロックアップ時間を短縮すること。

【解決手段】PLL回路20の位相比較器23は、基準信号frと比較信号fpの位相を比較し、両信号fr,fpの位相差に応じた信号を出力する。ループフィルタ25は強誘電体容量C1を含み、位相比較器23の出力信号に応じたチャージポンプ24から出力される位相差電流IPにより直流電圧を生成するとともに、その直流電圧を平滑化して制御電圧VCを生成する。VCO26は、制御電圧VCに応じた周波数の出力信号foを生成する。カウンタ31は、入力信号fiをカウントし、カウント値と第1の設定値,第2の設定値とを比較し、第1の期間、強誘電体容量C1を高電位電源VDDの電源線に接続し、第2の期間、強誘電体容量C1と低電位電源VSSの電源線を接続する。

(もっと読む)

発振回路、発振回路を備えた電子機器及び発振回路の制御方法

【課題】高精度発振器間の位相同期を間欠動作にすることにより低消費電力化する。

【解決手段】基準となる周波数の基準信号Frefを出力する周波数確度が高い高精度発振器100と、出力信号Foutの周波数を制御電圧Vcで制御する電圧制御発振器110と、基準信号Frefの位相と出力信号Foutの位相との位相差を検出し位相差信号Poを出力する位相比較部120と、位相差信号Poに基づき制御電圧Vcを生成する制御電圧生成部130と、位相比較部120への電源VDDの接続を接続状態または非接続状態に切り替えるスイッチ回路140と、位相差信号Poに基づき位相差が無くなった時点から所定の時間が経過するまでの期間はスイッチ回路140を接続状態にし、期間以外はスイッチ回路140を非接続状態にする制御信号Swを出力するタイマ回路150と、を含む発振回路1。

(もっと読む)

281 - 300 / 713

[ Back to top ]