Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

241 - 260 / 713

半導体集積回路

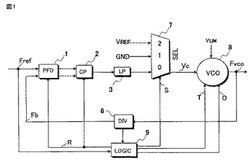

【課題】半導体集積回路の製造プロセスがばらつきを持っても所望の周波数特性を有するPLLを提供する。

【解決手段】PLLと制御ユニット9を具備し、PLLは位相周波数比較器1、ループフィルタ3、電圧制御発振器(VCO)8、分周器6を含み、VCO(8)は電圧電流変換器(VIC)とリング発振器を含む。制御電圧Vcに応答してVICは、リング発振器の動作電流を設定する制御電流を生成する。制御ユニット9は、PLLをオープンループのキャリブレーション動作期間とクローズドループの通常動作期間に切り換える。通常動作期間でVCOに所定の制御電圧Vcが供給され、VCOの周波数は所定の周波数とされる。キャリブレーション動作期間で制御電圧Vcと略等しいレベルの基準電圧VREFが供給された状態のVCOの周波数計測の間にVCOの周波数が所定の周波数と略等しくなるように、制御ユニット9はVIC81の動作パラメータTの値を設定する。

(もっと読む)

基準信号発生装置

【課題】起動特性に基づく安定的な遷移曲線に対して変動が生じても、高精度に自走DAC値を推定できる基準信号発生装置を実現する。

【解決手段】制御部10は、自走DAC値の推定タイミングtNになると、当該タイミングtNから特定時間に亘って遡る区間MNを基準区間として、推定曲線201を算出する。制御部10は、基準区間MNと異なる補正区間LMの同期DAC値を取得し、推定曲線201から得られる推定同期DAC値との差分値ΔDを算出する。制御部10は、差分値ΔDに基づいて補正値Cdを算出し、各同期DAC値を補正値Cdで補正することで補正同期DAC値を取得する。制御部10は、この補正同期DAC値を含む同期DAC値から新たな推定曲線を算出し、自走DAC値を推定する。

(もっと読む)

ディスプレイ駆動装置

【課題】本発明は、ディスプレイ駆動装置に関する。

【解決手段】本発明はディスプレイ装置、特にディスプレイ装置に使用されるバックライトユニット駆動装置において、映像信号が正常である場合には映像信号の周波数に同期された周波数を有する駆動信号を提供し、映像信号が異常状態である場合には予め設定された周波数を有する駆動信号を提供して、安定的な動作を行うため、入力された映像信号の周波数と分周された駆動信号の周波数の差を検出する周波数検出部と、上記周波数検出部からの検出結果により、上記映像信号の周波数と同期された周波数を有する上記駆動信号を生成する駆動信号生成部と、上記周波数検出部からの上記検出結果が異常動作である場合、上記周波数検出部の周波数検出動作を停止させる制御部とを含むディスプレイ駆動装置を提供する。

(もっと読む)

PLL回路

【課題】電圧制御発振器が発振信号出力動作を停止した場合、自動的に最適消費電流で電圧制御発振器の発振信号出力動作を復帰させることができるPLL回路を提供する。

【解決手段】リセット制御回路7は、電圧制御発振器5の発振信号出力動作の停止を検出し、電圧制御発振器5の発振信号出力動作の停止を検出している間、基準信号Ref_CKを分周してなるリセット信号RESETを生成する。カウンタ8は、リセット信号RESETの立ち上がり変化の回数をカウントする。ローパスフィルタ4は、前記リセット信号RESETがLレベルの間に周波数制御電圧Vcntを初期化する。電圧制御発振器5が有する出力アンプは、前記カウンタ8が出力するカウント値Cnt[1:0]が増加する毎に駆動電流を段階的に増加させることにより出力駆動能力を段階的に増加させ、周波数帯域を段階的に上げる。

(もっと読む)

基準信号発生装置

【課題】自走DAC値と実測の同期DAC値との誤差を取得して、当該誤差に応じた動作及び処理の検証を行える基準信号発生装置を実現する。

【解決手段】制御部10は、推定誤差検出タイミングTv(n)の時点で、直前の推定タイミングTe(m)から推定誤差検出タイミングTv(n)までの期間の実測した同期DAC値を読み出すととともに、推定タイミングTe(m)に算出された推定曲線201に対応する演算用関数および演算用係数を用いて各実測の同期DAC値に対応する自走DAC値を算出する。制御部10は、実測の同期DAC値と自走DAC値とを差分することで、誤差を検出するとともに、誤差の積算値である位相差を算出する。これら誤差や位相差は、推定曲線の精度の指標となるので、当該誤差や位相差を用いることで、自走DAC値に対する各種の検証が可能となる。

(もっと読む)

基準信号発生装置

【課題】常に高精度な制御電圧信号のレベル(DAC値)の推定を行うことができる基準信号発生装置を実現する。

【解決手段】制御部10は、起動とともに計時を開始し(S102)、計時を行いながら(S103)、自走DAC値の算出タイミングを検出して自走DAC値の算出タイミングになると(S104:Yes)、予め設定したタイミング(起動からの経過時間)と重み付け係数との関連テーブルから、重み付け係数Wを設定する(S105)。この際、重み付け係数は、起動からの経過時間が長いほど大きな値に設定される。これにより、DAC値の変動が激しい起動からの経過時間が短い期間では、過去のDAC値が今回の推定値に与える影響が少なくなる重み付けがなされる。一方、経過時間が十分に長いDAC値が安定する期間では、過去のDAC値が今回の推定値に与える影響が大きくなる重み付けがなされる。

(もっと読む)

デッドロック検出回路およびデッドロック復帰回路

【課題】誤検出することなく、デッドロック状態を正確に検出することができるデッドロック検出回路を提供する。

【解決手段】デッドロック検出回路は、PLL回路のデッドロック状態を検出するものであり、PLL回路の電圧制御発振器の出力信号を分周して、第1の分周クロックを出力するPLL内蔵分周器と、電圧制御発振器の出力信号を分周して、PLL回路の位相比較器へのフィードバッククロックとなる第2の分周クロックを出力するフィードバック分周器と、第1の分周クロックの周期によって決定される所定の期間に含まれる、第2の分周クロックのクロック数に基づいて、デッドロック状態であるか否かを表す判定信号を出力する誤ロック検出回路とを備えている。

(もっと読む)

位相同期回路

【課題】 簡単な構成で、暴走状態に陥る前により確実に異常を検知し、半導体装置の誤動作をより効果的に防止できる位相同期回路を提供する。

【解決手段】 発振制御回路11、電圧制御発振回路12、帰還回路13を備え、発振制御回路11の出力電圧、発振制御に係る発振制御回路11及び電圧制御発振回路12のアナログ内部電圧の内、少なくとも何れか1つの電圧を異常検出用電圧Vdi(i=1〜n)とし、異常検出用電圧Vdiがロック可能範囲の上限値より高く設定された第1判定電圧Vri1より高い場合または下限値より低く設定された第2判定電圧Vri2より低い場合に異常状態であると判定する異常判定回路15iが、異常検出用電圧Vdi夫々について各別に設けられ、異常判定回路15i夫々における異常状態の検出結果を用いて暴走前状態であるか否かを判定し、暴走前状態であると判定した場合に、初期化動作を行う異常復帰回路16を備える。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】エイリアシングによるエイリアシングによる誤動作の発生が防止されたDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を設定するカウンタ回路130と、外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相検出回路140と、外部クロック信号CLKに含まれるジッタ成分が所定の周波数以上であることに応答して、位相判定信号PDに基づいたカウンタ回路130のカウント値の更新を禁止するアンチエイリアス回路200とを備える。これにより、エイリアシングによる誤動作によって内部クロック信号LCLKが誤った方向に連続制御されるという問題がなくなる。

(もっと読む)

制御装置、クロック同期方法

【課題】DPLL回路において、入力クロックの瞬間的な位相跳びによる出力クロックの位相跳びの発生を抑制する。

【解決手段】出力クロックを入力クロックに同期させる制御を行う制御装置は、前記入力クロックと前記出力クロックとの位相差をカウントするカウント部と、前記カウント部がカウントした位相差のうち、所定範囲内の位相差を示すカウント値を抽出する抽出部と、抽出された前記所定範囲内の位相差を示すカウント値に基づいて位相差情報を生成する位相差情報生成部と、前記位相差情報生成部により生成された前記位相差情報に基づいて、生成する前記出力クロックの周波数を制御可能なクロック生成部と、を備える。

(もっと読む)

PLL(PHASELOCKEDLOOP)回路内のチャージポンプリークに起因した制御電圧リプルを最小化する技術

【解決手段】位相ロックループ回路を含む装置においてチャージポンプリーク電流の影響を和らげるようループフィルタのサンプリング間隔を適切に制御する技術を提供する。一態様において、装置は電圧制御発振器(VCO)、位相周波数検知部(PFD)、VCOを固定するための制御電圧を提供するループフィルタ、及びUPパルスDOWNパルスの少なくともいずれか1つに応じてループフィルタに出力信号を供給するよう構成されたチャージポンプを含む。ループフィルタの入力とチャージポンプの出力との間で結合されサンプリング間隔によって特徴付けられたスイッチを含む。サンプリングスイッチ制御部は位相比較動作の前にスイッチを閉じ位相比較動作が完了するとスイッチを開くことでチャージポンプからのリーク電流の影響を和らげるようサンプリング間隔幅を適切に制御するよう構成される。 (もっと読む)

半導体集積回路

【課題】リアルタイムクロック用の半導体集積回路の消費電力をさらに低減すると共に、生成されたクロック信号を周辺回路においても利用できるようにする。

【解決手段】この半導体集積回路は、外部から供給される電源電圧に基づいて、第1の電源電圧及び第2の電源電圧を生成する定電圧回路と、第2の電源電圧が供給され、発振動作を行うことにより原振クロック信号を生成する発振回路と、第2の電源電圧が供給され、原振クロック信号を分周することにより複数種類の分周クロック信号を生成する分周回路と、第1の電源電圧が供給され、分周回路によって生成される少なくとも1種類の分周クロック信号に基づいて計時情報を管理するロジック回路と、原振クロック信号と所定数の分周クロック信号との内の1つを選択するセレクタ回路と、選択されたクロック信号を出力端子に供給する出力回路とを具備する。

(もっと読む)

ループ設定調整回路

【課題】ループ回路において、フィードバック遅延やPVT変動を自動的に検出して、ループ設定を調整し最適化することができるループ設定調整回路を提供する。

【解決手段】ループ設定調整回路は、クロックツリーシンセシスがフィードバック経路に挿入されたループ回路のループ特性を決定するループ設定を調整する。ループ設定調整回路は、クロックツリーシンセシスによる遅延時間を検出する検出回路と、検出回路によって検出される遅延時間に相当する時間、遅延時間よりも短い周期の発振クロックを出力する発振回路と、発振回路から出力される発振クロックのクロック数をカウントし、カウント値に対応する制御信号を出力する制御回路とを有し、制御回路から出力される制御信号により、クロックツリーシンセシスによる遅延時間に応じて、ループ設定を調整する。

(もっと読む)

チャージポンプ回路、及びクロック生成器

【課題】チャージポンプ容量の充電電流と放電電流とが等しくなるように補正する。

【解決手段】外部から充電制御信号を受けて制御電圧を増加させ、外部から放電制御信号を受けて制御電圧を減少させる第1のモードと、補正動作を行う第2のモードとを有したチャージポンプ回路であって、第1のモードにおいて、充電制御信号に応じて第1のノードを通して充電電流を流し出す充電部と、放電制御信号に応じて第2のノードを通して放電電流を吸い込む放電部と、第2のモードにおいて、第1のノードと第2のノードとに一端が接続される検出抵抗と、検出抵抗の他端に参照電圧を供給する電圧源と、充電部が検出抵抗の一端へ充電電流を流し出し放電部が検出抵抗の一端から放電電流を吸い込んだ状態における検出抵抗の一端の電圧と参照電圧との差に基づいて、充電部が流し出す充電電流と放電部が吸い込む放電電流とが等しくなるように補正する補正部とを備える。

(もっと読む)

クロック再生装置

【課題】高速で安定したクロックを再生できるクロック再生装置を提供すること。

【解決手段】受信データからデータ受信用の再生クロックを得るクロック再生装置において、前記受信データから不連続を含む再生クロックを生成する再生クロック生成部と、この再生クロック生成部から出力される再生クロックを所定時間逓倍する再生クロック逓倍部とを有し、前記再生クロック生成部から出力された不連続を含む再生クロック信号を前記再生クロック逓倍部で演算し、連続した再生クロックを得ることを特徴とするクロック再生装置。

(もっと読む)

電圧制御発振回路

【課題】発振周波数を制御するPLL回路で生成可能な制御電圧の最大値を低電圧化しても、可変容量ダイオードに印加される電圧の可変範囲を広げることができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ること。

【解決手段】この電圧制御発振回路1は、発振用トランジスタ2と、可変容量ダイオード16を有し発振用トランジスタ2に接続された共振回路13と、電源電圧が印加される電源端子T2とグラウンドとの間に介挿されると共に可変容量ダイオード16に対して並列に接続されたコレクタ抵抗RCと、コレクタ抵抗RCのグラウンド側の端部とグラウンドとの間に介挿され発振周波数を制御する制御電圧が印加される制御用トランジスタ21とを具備する。

(もっと読む)

PLL回路

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部とを有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記分周信号の周波数と前記基準信号の周波数とを比較し、前記分周信号の周波数が前記基準信号の周波数に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

PLL回路

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部と、を有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記生成部から出力された前記制御電圧と前記参照電圧とを比較し、前記生成部から出力される制御電圧が前記参照電圧に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

クロッククリーンアップ位相ロックループ(PLL)

【解決手段】スプリアスを低減し受信機性能を向上し得るクロッククリーンアップ位相ロックループ(PLL)が述べられる。典型的な一設計では、集積回路はPLL及びアナログ/デジタルコンバータ(ADC)を含む。PLLは、フラクショナル分周比で生成され、突発的周波数ジャンプによるスプリアスを有する第1クロック信号を受信する。第1クロック信号は、集積回路外部のフラクショナルNの周波数シンセサイザによって生成され得る。PLLは、整数の分周比で、低減されたスプリアスを有する第2クロック信号を生成する。ADCは、第2クロック信号に基づいてアナログベースバンド信号をデジタル化してデジタルサンプルを供給する。集積回路は更に、低ノイズ増幅器(LNA)を有し、これは第1クロック信号をクリーンアップするPLLの使用により、集積回路の基板を介して結合するより小さいスプリアスを観測し得る。 (もっと読む)

基準信号発生装置

【課題】、目的周波数の基準信号の異常を、確実且つ正確に検出することができる基準信号発生装置を実現する。

【解決手段】基準信号発生装置1は、位相比較器11、ループフィルタ12、電圧制御発振器13、分周器14からなるPLL回路を備える。基準信号発生装置1の波数計測部15は、PLL回路の調整用タイミング信号に基づく期間での復調用基準周波数信号の波数をカウントし、期間毎のカウント値を異常発振検出部16へ出力する。異常発振検出部16は、調整用タイミング信号の元となる基準信号と復調用基準周波数信号との仕様周波数範囲の関係に基づいて設定される正常発振カウント値範囲を予め記憶している。異常発振検出部16は、波数計測部15から取得したカウント値が正常発振カウント値範囲内に無ければ異常発振として検出し、外部へ通知する。

(もっと読む)

241 - 260 / 713

[ Back to top ]