Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

181 - 200 / 713

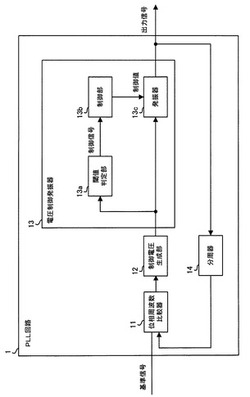

PLL回路および電圧制御発振器

【課題】PLL回路のデッドロック状態になることを防止する

【解決手段】閾値判定部13aは、制御電圧の高低を示す制御信号を生成する。制御部13bは、制御信号に応じた制御値を出力し、制御値が発振周波数の上限および下限について最も高い対応関係を示す場合において制御信号が高を示すとき、および制御値が発振周波数の上限および下限について最も低い対応関係を示す場合において制御信号が低を示すときのいずれか一方を満たす際、所定の制御値を出力する。発振器13cは、制御電圧と発振周波数との対応関係が発振周波数の上限および下限が異なるように複数定められていると共に対応関係が複数の制御値と対応付けられており、制御値が示す対応関係における制御電圧に応じた発振周波数を有する出力信号を出力する。

(もっと読む)

クロック供給装置

【課題】入力クロックの周波数がジッタやワンダ等により時間的に変動する場合においても、入力クロックの不具合の状態を的確に判定することができようにし、適切な保守が可能となる、クロック供給装置を提供する。

【解決手段】本発明のクロック供給装置においては、N系クロック受信部22とN系MTIE計測部31との間に設置されるワンダ・ジッタ除去フィルタ41と、E系クロック受信部23とE系MTIE計測部32との間に設置されるワンダ除去フィルタ42と、を有して構成される。そして、発振器部26が有するローパスフィルタ特性のカットオフ周波数と、ワンダ除去フィルタ41,42の有するローパスフィルタ特性のカットオフ周波数とが一致あるいは略等しいように構成される。

(もっと読む)

通信装置及びその折り返し試験方法

【課題】SSCのジッタを抑制し、SSCの変調度を滑らかに遷移させることが可能なSSC生成機能を有するPLL回路及び通信装置を提供する。

【解決手段】SSCコントローラ18は、SSCの変調プロファイルに応じて予め定められたタイミングで位相シフト量を変更するよう位相補間器15を制御し、出力クロック信号C_OUTの変調度を周期的に変更させる。さらに、SSCコントローラ18は、帰還クロック信号C_FBの一周期内において位相補間器15より出力される位相シフト信号C_PSに与える総位相シフト量を、当該総位相シフト量と直前の一周期における総位相シフト量との差分が常に基本遅延量Δ以下となるよう制御する。ここで、基本遅延量Δは、出力クロック信号C_OUTの周期T_OUTを位相補間器15の位相分解能Nrで除算した値(つまり、T_OUT/Nr)である。

(もっと読む)

ローカル信号生成回路

【課題】

周波数ホッピングを用いた通信を行うためのローカル信号生成回路が従来技術に開示されているが、実際に周波数ホッピングを用いたワイヤレスUSBの通信システムにおいては、ローカル信号の出力を開始してから出力が安定するまでに時間がかかり通信における規格を満たすことができないという課題が存在していた。

【解決手段】

第1の周波数で所定のバイアス電圧を中心に振動する第1のローカル信号を出力する第1の発振部と、前記第1の周波数より高い周波数である第2の周波数で前記バイアス電圧を中心に振動する第2のローカル信号を出力する第2の発振部と、前記第1および第2のローカル信号を入力すると共に前記第1のローカル信号および前記第2のローカル信号のそれぞれを選択的に出力し、前記第1のローカル信号および前記第2のローカル信号のそれぞれを出力しない期間においては前記バイアス電圧を出力する選択回路と、を有する。

(もっと読む)

クロックを並列データに整列させるための回路

【課題】クロック信号を並列データに整列させるための方法を提供する。

【解決手段】クロックシフティング回路10は、入来クロック信号8を入来データ信号16に対してシフトし、データクロッキング回路20は、シフト済みクロック信号を使用して、入来データ信号16を再クロックする。クロックシフティング回路10は、位相ロックループ回路2に直列に接続されている複数のDフリップフロップ回路4,6を連結して備える。データクロッキング回路20は、それぞれの入来データビット16を受信し、ミキサ22に対するローカルオシレータとして働く真−補数ブロック50,58を備える。複数のシフト済みクロック信号62,54,64,56は、入来クロック信号16に対して90度、180度、及び270度シフトされたものなど、が生み出される。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】安定した位相同期ループを構成できない。

【解決手段】本発明は、第1、第2のクロック信号をカウントする第1、第2のカウンタと、第1のクロック信号を遅延させた第1、第2の遅延クロック信号を生成する遅延クロック生成回路と、第1のクロック信号及び第1、第2の遅延クロック信号のそれぞれで第2のカウンタのカウント値をサンプリングするサンプル回路と、第1、第2のクロック信号を所定の数で分周した第3のクロック信号との位相差と、サンプリングしたカウント値に応じ、そのサンプリングしたカウント値のうち1つを選択する選択回路と、第1のカウンタ及び選択回路が選択したカウント値に応じて第1、第3のクロックとの位相差を演算する位相誤差演算回路と、位相誤差演算回路の演算結果に応じて第2のクロックを出力するデジタル制御発振器とを有するデジタルフェーズロックドループ回路である。

(もっと読む)

電圧制御発振器

【課題】発振周波数のばらつきを抑えることができる電圧制御発振器を提供する。

【解決手段】本発明による電圧制御発振器は、直列に接続されたN(Nは2以上の整数)個の反転差動増幅器(9)を備えている。N個の反転差動増幅器(9)の各々は、所定の電圧値の定電圧(Vcn1)と制御電圧(Vcnt)とに応じて動作する。N個の反転差動増幅器(9)の各々の動作電流は、定電圧(Vcn1)に応じた電流と、制御電圧(Vcnt)に応じた電流とを加算した電流の値で直接定まる。

(もっと読む)

基準周波数発生装置

【課題】リファレンス信号が取得できなくなっても長時間にわたって高精度な基準周波数信号を出力可能で、使用温度範囲が広く、安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置11は、GPS受信機21と、PLL回路31と、検出器28と、記憶部29と、制御部22と、を備える。PLL回路31は、GPS受信機21からのリファレンス信号に基づいて得られた同期制御信号に基づき、デジタル制御発振器26を制御する。記憶部29には、同期制御信号の制御値と、そのときの電圧値及び温度と、の対応関係が記憶されている。リファレンス信号が得られない場合、制御部22は、前記対応関係と、検出器28が検出した電圧及び温度と、に基づいて自走制御信号を決定し、デジタル制御発振器26を制御する。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

PLL周波数シンセサイザ

【課題】ループフィルタの容量素子の面積の増大を抑制しつつループフィルタの自然周波数ωnを小さくすることができるPLL周波数シンセサイザを提供する。

【解決手段】PLL周波数シンセサイザ1Aでは、位相比較部12,ゲート部13,チャージポンプ14,容量素子15,電位調整部16,電圧制御発振器18および帰還分周部19によりループが構成されている。このループにおいて、ゲート部13およびチャージポンプ14と電位調整部16とは並列的に設けられている。位相比較部12に入力される基準発振信号RCLKと帰還発振信号PCLKとの位相差が小さくなるように、チャージポンプ14から容量素子15へ充放電電流Icpが入力され、また、電位調整部16により容量素子15の第1端の電位が調整される。

(もっと読む)

PLL回路

【課題】ループフィルタの回路面積を削減すると共に、電圧制御発振器の動作の安定化やノイズ感度の低減が可能なPLL回路を提供することである。

【解決手段】本発明のPLL回路は、位相比較器3の出力信号に応じて出力電圧を制御する第1及び第2のチャージポンプ回路4、5と、第1のチャージポンプ回路4の出力に基づく信号から所定の周波数成分が除去された第1の電圧信号を出力する第1のフィルタ6と、第2のチャージポンプ回路5からの電流を入力し、所定の一定電圧を第2の電圧信号として出力する第2のフィルタ7と、第1のフィルタ6からの第1の電圧信号と基準電圧との比較結果に基づき第3の電圧信号を出力する電圧制御部30と、第1及び第2の電圧信号を低ゲイン入力、第3の電圧信号を高ゲイン入力とし、当該第1乃至第3の電圧信号に基づき発振周波数を生成する電圧制御発振器10を備える。

(もっと読む)

PLL回路

【課題】高周波動作において、互いに容量が異なる複数のコンデンサの組み合わせを切り替えて電圧制御発振器の発振周波数帯域を切り替える際に、全ての発振周波数帯域同士を重なり合わせることが可能なPLL回路を提供することを目的とする。

【解決手段】互いに容量が異なる複数のコンデンサ51−1〜51−nの組み合わせを切り替えることにより発振周波数帯域を切り替える電圧制御発振器2を備えるPLL回路1において、電圧制御発振器2が高周波動作しているとき、容量が比較的大きなコンデンサ52−4又はコンデンサ52−5が選択されなくなる場合、補正用のコンデンサ5−1又はコンデンサ5−2を選択して電圧制御発振器2の全体の容量を大きくする。

(もっと読む)

クロック・データ再生回路及び再生方法並びに局側装置

【課題】バースト信号間の無信号区間に入ったとき、一時的に参照クロック信号と周波数が大きくずれるという現象の発生を防止することができるクロック・データ再生回路及び再生方法並びに当該再生回路を用いた局側装置を提供する。

【解決手段】周波数逓倍部110により、参照クロック信号の周波数をデータ信号相当の周波数に逓倍して逓倍クロック信号とする他、入力選択部111を用いて入力を選択する。すなわち、データ信号としてのバースト信号が入力されているときは、入力されたバースト信号と位相が同期するように再生クロック信号を生成し、バースト信号が入力されていないときは逓倍クロック信号と位相が同期するように再生クロック信号を生成する。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

サプライレギュレートされたフェイズロックループ(PLL)及び用いる方法

サプライレギュレートされたフェイズロックループ(PLL)が提供される。PLLは、サプライレギュレーティングループ、電圧制御発振器(VCO)、及びVCOのためのプログラマブルデカップリングキャパシタアレイを備える。VCOデカップリングキャパシタアレイのキャパシタンスは、NかけるCUNITに等しくなるように調整可能であり、NはN分周回路の乗算ファクタの現在の値であり、CUNITはデカップリングキャパシタアレイを製造するために選ばれたプロセス技術に対して特徴付けられたユニットキャパシタンスである。PLLが1つの周波数帯から他にスイッチするとき、VCOデカップリングキャパシタによって導入される高次ポールがPLL参照周波数をトラックし、PLLの動作安定性を改善する。  (もっと読む)

(もっと読む)

半導体装置

【課題】フラクショナルN−PLL回路における出力クロック信号でのスプリアスの発生を抑制する。

【解決手段】出力クロック信号を出力する電圧制御発振器と、出力クロック信号を分周して分周クロック信号を生成し、基準クロック信号と分周クロック信号とを比較し、比較結果に基づき出力信号を出力するN個の制御ユニットと、各制御ユニットからの出力信号を加算する加算器と、加算器の出力をフィルタ処理し電圧制御発振器に出力するローパスフィルタとを備え、分周クロック信号に同期して所定の順序で巡回させ供給するN個のデータからなる分周比に係る設定情報を、各制御ユニットに対して初期値を互いに異ならせて供給し分周動作及び比較動作を行わせるようにして、N個の制御ユニットにより移動平均フィルタを形成し量子化ノイズを低減し、出力クロック信号でのスプリアスの発生を抑制できるようにする。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

アキュムレータおよび位相デジタル変換器を使用する2ポイント変調のデジタル位相同期ループ

2ポイント変調をサポートするデジタル位相同期ループ(DPLL)が説明される。1つの設計において、DPLLは、位相デジタル変換器、ループ内で動作するループフィルタ、ローパス変調パスのための第1の処理ユニットおよびハイパス変調パスのための第2の処理ユニットを含む。第1の処理ユニットは、入力変調信号を受信し、位相デジタル変換器の後でループフィルタより前のループの内部の第1のポイントに対して第1の変調信号を供給する。第2の処理ユニットは、入力変調信号を受信し、ループフィルタより後のループの内部の第2のポイントに対して第2の変調信号を供給する。第1の処理ユニットは、周波数を位相に変換するために入力変調信号を累算するアキュムレータを含み得る。第2の処理ユニットは、可変利得で入力変調信号をスケールするスケーリングユニットを含み得る。 (もっと読む)

クロックデータリカバリ回路および逓倍クロック生成回路

【課題】データ入力の位相変化に対する受信マージンの減少を抑止でき、誤受信の確率の増大を抑止できるクロックデータリカバリ回路および逓倍クロック生成回路を提供する。

【解決手段】入力データと抽出クロックの位相差を検出して位相差に応じたアナログ量を出力する第1の位相検出器110と、ループフィルタ150と、第1の位相検出器の出力に応じてループフィルタから電流を充電または放電するチャージポンプ130,140と、VCO160と、入力データと抽出クロックの位相差の極性を検出する第2の位相検出器120と、第2の位相検出器の検出結果に応じて第1の位相検出器がもつ位相オフセットを相殺する補正位相情報を発生する補正位相情報発生部210と、補正位相をループ200に加算する補正位相加算部220と、を有し、補正位相加算部220は、チャージポンプの充電電流と放電電流を相対的に変化させる。

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

181 - 200 / 713

[ Back to top ]