Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

221 - 240 / 713

発振回路、発振回路を持つ装置、および発振方法

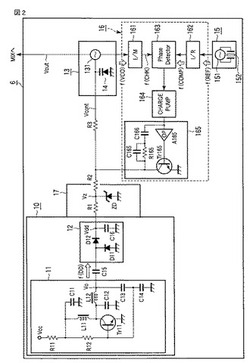

【課題】局部発振周波数を制御する制御電圧を得る際に用いられる電源回路(DC/DCコンバータ)の内部発振周波数に起因する障害を回避する。

【解決手段】電源回路10と電圧制御発振器13と基準発振器15と電圧制御発振器の発振周波数f(VCO)を電圧制御する制御回路16を備える。電源回路10は内部発振器11の発振信号Voから所定電圧Vzを提供する。電圧制御発振器13は可変容量ダイオード14に印加される制御電圧Vcontによって発振周波数が変化する。制御回路16は、基準発振器15の発振周波数f(REF)に基づく比較周波数f(COMP)とf(VCO)に基づく検査周波数f(CHK)との比較結果によりVcontを制御する。Vcontは所定電圧Vzを用いて生成される。ここで、Nを自然数としたときに、内部発振器11の発振周波数f(DD)が比較周波数f(COMP)のN倍より高くN+1倍より低くなるようにする。

(もっと読む)

基準周波数発生器

【課題】リファレンス信号を取得できている状態において動作環境が通常のものから一時的に外れた場合でも、自走用制御信号を精度良く得ることができる基準周波数発生器を提供する。

【解決手段】基準周波数発生器は、電圧制御発振器と、位相比較器と、温度センサと、制御部と、を備える。制御部は、GPS受信機からの1PPS信号が供給されなくなると、ループフィルタから出力される制御電圧信号に代えて、自走用制御電圧信号を生成して電圧制御発振器を制御する。制御部は、電圧制御発振器が動作している経過時間に応じて、前記自走用制御電圧信号を決定する。また、この制御部は、1PPS信号を取得できているときに時系列で記憶された制御電圧信号から、温度センサの検出値が設定温度範囲から外れたときの制御電圧信号を除外した上で、残りの制御電圧信号の変化に基づいて前記自走用制御電圧信号を決定することができる。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

位相補償用クロック同期回路

【課題】短時間で精度よく位相調整を行うことが可能な位相補償用クロック同期回路を提供する。

【解決手段】DLLは、入力レシーバ1と、遅延チェーン回路2と、遅延複製器4と、位相比較器5と、リセットパルス発生器6と、粗調整期間発生器7と、分周器8と、単位可変カウンタ9と、を備えている。まず単位可変カウンタ9の増減単位を17または1(平均で16)として粗調整を行って粗くロックさせた後に、単位可変カウンタ9の増減単位を1として微調整を行って細かくロックさせるため、短い期間で確実にクロックINTCKXとクロックEXTCKXの位相を合わせることができる。

(もっと読む)

基準周波数発生装置

【課題】ユーザ側装置で立上りタイミングが一致した2つの信号を容易に得られる基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、ユーザ側装置へ10MHz及び1Hzの信号をそれぞれ出力する2つの出力端子と、ユーザ側装置から戻された上記信号をそれぞれ入力する2つの入力端子と、を備える。基準周波数発生装置を初めてユーザ側装置に接続したときは、2つの出力端子から出力される波形は何れも、その立上りタイミングがUTCの1秒に正確に同期している。この基準状態で、出力する1Hzの波形と、ユーザ側装置から戻された1Hzの波形との間で、立上りタイミングの差が測定される。また、ユーザ側装置から戻された1Hzの波形と、同様に戻された10MHzの波形との間で、立上りタイミングの差が測定される。CPUは、得られた時間差に基づき、10MHz及び1Hzの出力信号波形の位相を所定の関係に従って調整する。

(もっと読む)

基準信号発生装置

【課題】演算処理能力の低い安価なCPUを用いても、ホールドオーバー時における位相差を抑制して、保守作業の時間的制限等の自走発振に係わる課題を解決することができる基準信号発生装置を実現する。

【解決手段】制御部10は、1PPSが入力されている間に同期型制御電圧信号のレベルを経時的に観測し、記憶する。制御部10は、リファレンス信号の入力断を検出すると、自走用第1制御電圧信号を生成し、電圧制御発振器14へ与える。また該自走用第1制御電圧信号を用いて前記電圧制御発振器を制御している期間において、自走用第2制御電圧信号の算出を開始する。そして前自走用第2制御電圧信号の記算出が完了し次第、自走用制御電圧補正値を算出し、位相差を相殺しながら制御を続ける。以後、H.O.が終了するまで、自走用第N制御電圧信号の算出を繰り返し、高精度な基準周波数信号を発生させる。

(もっと読む)

分周器

【課題】 動作周波数が高められた分周器を提供する。

【解決手段】 動作制御信号ENBが‘H’レベルに遷移し、クロック信号VCO,分周信号VCO_div2が‘L’レベル,‘H’レベルで停止した場合、3入力ナンドゲート14から出力された制御信号Aが‘L’レベルとなり、イクスクルーシブノアゲート10から出力されるトリガ信号VCO_delayが‘H’レベルとなる。トリガ信号VCO_delayはフリップフロップ11_1のトリガ端子Tに入力されており、フリップフロップ11_1から出力されている分周信号VCO_div2を‘H’レベルから‘L’レベルに遷移して、フリップフロップ11_1をリセット状態にする。

(もっと読む)

原子発振器

【課題】光源の輝度劣化の影響を回避する。

【解決手段】第1の励起光52を出力する励起光出力部12と、第1の励起光52を分光し第2の励起光152を出力する分光器24と、第1の励起光52により励起される第1のガスセル13を含み第1の周波数信号O1を出力する第1の原子発振部100と、第2の励起光152により励起される第2のガスセル113を含み第2の周波数信号O2を出力する第2の原子発振部200と、第1の周波数信号O1と第2の周波数信号O2とを混合した混合信号301を出力する周波数混合器310と、混合信号301の周波数を変換した出力信号OUTを出力する周波数変換部300と、を含む原子発振器1。

(もっと読む)

対称性負荷遅延セル発振器(symmetricloaddelaycelloscillator)

【解決手段】発振器は、制御回路と、対称性負荷遅延セルのリングとを含む。各遅延セルは、2つの新規な対称性負荷を含む。各負荷は、レベルシフト回路と、電流ソース接続されたトランジスタと並列に結合されたダイオード接続されたトランジスタとを含む。制御回路は、発振器入力信号をバイアス制御信号に変換し、バイアス制御信号は、対称性負荷の実効的な抵抗を、遅延セルの遅延が入力信号の関数であるように制御する。制御回路は、発振遅延セル出力信号が一定の振幅を有するように遅延セルのレベルシフト回路を制御するため、制御ループの対称性負荷レプリカを用いる。第1の有利な側面では、この一定の振幅により、発振器は広い周波数レンジで動作可能である。第2の有利な側面では、発振器入力信号は出力信号発振周波数に対して、実質的に線形の関係を有する。 (もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】ノイズの影響でディレイラインが逆方向に調整されたり、ジッタ成分の影響でループに入ることのないDLL回路を提供する。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD1に基づいて、サンプリング周期ごとにカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が所定の論理レベルを示したことに応答して、同じサンプリング周期内におけるその後の位相判定信号PD0の変化を無効化した位相判定信号PD1を生成する無効化回路200とを備える。これにより、短い周期で位相判定信号に影響を与える成分を排除することが可能となる。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラを提供する。

【解決手段】PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL300)とを備えている。このPLL300は、誤り訂正信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器312と、前記発振器312に結合され、前記基準信号341を受信し、且つ前記基準信号341と、フィードバック信号342との間の位相差に基づいて誤り訂正信号を生成させる位相周波数検出器(PFD302)と、前記PFD302に結合され、周期的にPFD302が誤り訂正信号を生成することができるようにする抑制回路321とを備えている。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】従来のADPLL回路では、出力クロックにデューティ劣化がある場合、最終的に導き出される位相差に大きな誤差が生じてしまう。

【解決手段】第1クロックをカウントする第1カウンタと、第2クロックを分周した第3クロックをカウントする第2カウンタと、第3クロックの遅延クロックと第1クロックを比較した第1比較結果と、第1クロックの遅延クロックと第3クロックを比較した第2比較結果とに応じ第1、第3クロックの相対的位相差を検出する第1位相検出器と、第2クロックの周期を測定する第2位相検出器と、第2位相検出器の検出結果により第1位相検出器の検出結果を正規化した値と、第1、第2カウンタの値とに応じて第1、第3クロックとの位相差を演算する位相誤差演算部と、位相誤差演算部の演算結果に応じ第2クロックを出力するDCOとを有するデジタルPLL回路。

(もっと読む)

デジタル位相ロック・ループ(DPLL)、デジタル位相ロック・ループ(DPLL)内のジッタを制御するための方法、デジタル制御発振器(DCO)内のディザを最適化するための方法、および自己ディザリング・デジタル制御発振器(DCO)回路

【課題】 デジタル位相ロック・ループ(DPLL)および方法を提供する。

【解決手段】 デジタル位相ロック・ループ(DPLL)および方法は、入力として基準クロックを受け取り、ディザリングした基準クロック信号を出力するように構成された調整可能遅延線を含む。位相周波数検出器(PFD)は、ディザリングした基準クロック信号をフィードバック・クロック信号と比較して、ディザリングした基準クロック信号とフィードバック・クロック信号との位相および周波数の差を決定するように構成される。デジタル制御発振器(DCO)は、PFDから早遅判断を受け取り、それに応じて出力を調整するように構成され、ディザリングした基準クロック信号はDPLLの全体的な動作を強化するためにジッタ応答を分散する。

(もっと読む)

デジタルPLL回路及びデジタルPLL動作方法

【課題】CLVスピンドル制御のランダムシーク時でもスループット低下を抑え、かつ安価で消費電力を抑えたワイドキャプチャ対応のデジタルPLL回路を提供する。

【解決手段】本発明のデジタルPLL回路10Aは、周波数値fq’に応じてマスタクロックsclkの周波数を切り替えるマスタクロック切り替え手段10Bと、周波数値fq’に一定の倍率を乗じて数値制御発振器6へ出力するとともに、マスタクロックsclkの周波数が切り替わる前後で同期クロックgclkの周波数が一定になるように前記倍率を切り替える倍率切り替え手段10Cと、を備えたことを特徴とする。

(もっと読む)

PLL回路、及び無線機

【課題】 位相誤差の小さい、発振信号の精度が高いPLL回路及び無線機を提供する。

【解決手段】 第一差動信号を生成する第一発振部と、前記第一差動信号を90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とするPLL回路。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

高性能信号発生

【課題】高性能位相検出器は、プログラムで制御できる周波数および位相を有するデジタル基準信号を生成する局部デジタルオシレータを含む。

【解決手段】位相検出器は、デジタル基準信号とサンプリングされた入力信号の間の位相差を蓄積し、位相誤差の指標を作る。位相検出器は、周波数合成器において用いられ、低位相ノイズおよび正確な位相制御で信号を発生することができる利点がある。さらに、この種類のシンセサイザは、低ジッタのクロックおよび波形を生成するATEシステムおよび他の電子システムにおいて、ビルディングブロックのように用いられる。

(もっと読む)

基準信号生成装置及びこれを用いた機器

【課題】広く普及しているADSL方式等を採用した通信回線を利用して、利用者側において、通信品質の低下や発着信の制約等を生じることなく、高精度な基準信号を容易且つ安価に得ることが可能な基準信号生成装置及びこれを用いた機器を提供する。

【解決手段】局側の通信装置と、利用者側の端末装置との間で、通信回線を介して通信を行う通信システムを用いて基準信号を生成する基準信号生成装置において、前記局側の通信装置から前記通信回線を介して伝送される一定の周波数を有する基準信号が含まれる信号を入力し、前記入力信号から基準信号を抽出する基準信号抽出回路を備えるように構成した。

(もっと読む)

PLL回路およびその制御方法

【課題】従来のPLL回路は発振周波数を精度良くかつ安定して制御することができないという問題があった。

【解決手段】本発明にかかるPLL回路は、2つのクロック信号の位相差を検出するPFD401と、PFD401の検出結果に基づいて電圧404を出力するLPF403と、電圧404に基づいて出力するVCO出力クロック406の周波数を制御するVCO405と、VCO出力クロック406を分周して出力クロック408を出力する分周器407と、電圧404に基づいて分周器407の分周比を調整する自動調整回路411と、を備える。さらに自動調整回路411は、分周器407を制御する制御信号419と基準電圧を制御する制御信号420とを出力する比較回路434と、基準電圧選択器413と、を備える。このような回路構成により、PLL回路の発振周波数を精度良くかつ安定して制御することができる。

(もっと読む)

221 - 240 / 713

[ Back to top ]