Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

321 - 340 / 713

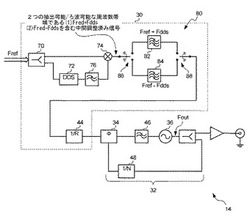

試験測定装置並びに位相拘束ループ及び方法

【課題】消費電力が大きくなく、位相ノイズが小さく、広い同調範囲のPLLを提供する。

【解決手段】位相検出器34は、基準信号路30及び帰還信号路32から入力の位相差を検出し、位相検出器出力を発生する。発振器32は、位相検出器出力に応答し且つこの位相検出器出力に基づいた発振出力Foutを発生する。この発振出力Foutが帰還信号路32に供給される。基準信号路30内のミキサ74は、基準信号Frefをダイレクト・デジタル・シンセサイザ72からの出力と混合する。基準信号路内のスイッチング機構80は、複数の異なるフィルタの1つを選択的にミキサ及び位相検出器の間に直列に配置する。

(もっと読む)

PLL回路

【課題】複数のVCOを切り替えて使用するPLL回路において、VCOの位相雑音を最適化することである。

【解決手段】PLL回路11の複数のVCO12−1〜12−nの内の1つの選択は、VCO選択データにより行われ、キャパシタの選択はVSBデータにより行われる。バイアス電流設定回路25は、VCO選択データとVSBデータと制御電圧のデジタル変換値VTDをデコードして、予め定めたバイアス設定値を可変電流源I1に出力する。

(もっと読む)

低域ろ波回路

【課題】容量素子の小型化を図る低域ろ波回路(ループフィルタ)において、容量素子としてMOS容量を使用した場合の電圧依存によるPLL応答特性のばらつきと、MOS容量として薄膜ゲートトランジスタを使用した場合のゲートリーク電流によるジッタ特性の劣化を抑制する。

【解決手段】ループフィルタは、第1の容量素子31と、この容量素子31に直列に接続された抵抗素子32及び第2の容量素子33とを備える。前記第1の容量素子31の一端に接続された第1の入力端IN1に第1の電流(Ip/10)を与え、前記第1の容量素子31の他端に接続された第2の入力端IN2に第2の電流(Ip/10)を与えることにより、第1の容量素子31の小型化が図られる。前記抵抗素子32に直列に接続された可変電圧電源35は、電圧制御端子36から、第1の容量素子31の両端の印加電圧が一定になるように制御される。

(もっと読む)

位相同期装置

【課題】本発明は、短いロッキングタイムを有しながらも、安定的に動作できる位相同期装置を提供する。

【解決手段】本発明の位相同期装置は、入力クロックを所定の分周比で分周した後、順次遅延させる動作により周波数を判別し、前記判別された周波数情報を用いて発振器ゲイン設定信号を生成する発振器ゲイン設定手段と、前記入力クロックに応じて、前記発振器ゲイン設定信号に対応する周波数を有する出力クロックを発振させるPLL回路を含むことを特徴とする。

(もっと読む)

電圧制御発振回路

【課題】発振信号の周波数帯域を広くさせつつ、位相雑音を低減することが可能な電圧制御発振回路を提供することを目的とする。

【解決手段】電圧制御発振器7〜10と、選択信号Vout_SELに対応する発振信号を選択するセレクタ11と、セレクタ11により選択された発振信号の振幅値Vout_Levを検出する検出回路12と、スイッチ13、14と、スイッチ13を介して入力される電圧Vtuneに対応するデジタル値Daを出力するとともに、スイッチ14を介して入力される振幅値Vout_Levに対応するデジタル値Dbを出力するADC回路15と、選択信号Vout_SEL及び選択信号Vout_CAPをデジタル値Daに基づいて出力するとともに、電圧制御発振器に流れる電流値をデジタル値Dbに基づいて制御する制御回路16とを備えて電圧制御発振回路2を構成する。

(もっと読む)

同期確立装置および通信装置

【課題】それぞれの発振器を備えた複数の受信部の同期を容易に確立すること。

【解決手段】現用系A受信部140の同期確立部200は、複数の受信部(140、150、160)それぞれに備えられた第一の発振器230によって生成された互いに周波数が異なる複数の波形信号を入力する入力部(210、220、240)と、入力部によって入力された複数の波形信号に対する論理演算により複数の受信部に共通する波形の共通波形信号を算出する算出部250と、算出部250によって算出された共通波形信号から各受信部内部における処理周波数を規定するローカル信号を生成するPLL部260、第二の発振器270および分周器265と、を備える。

(もっと読む)

PLL回路

【課題】 高い線形性をもった電圧―電流特性を備え、ゲイン変動を抑えた電圧電流変換回路を有するPLL回路を提供する。

【解決手段】 電圧電流変換回路11は、制御電圧VCを受けるNチャネルMOSトランジスタN1と、NMOSトランジスタN1と直列に接続されたPチャネルMOSトランジスタP1と、PMOSトランジスタP1とミラー回路を構成するPMOSトランジスタP2と、PMOSトランジスタP1と並列に接続された電流源13を備える。PMOSトランジスタP2から出力される制御電流Ioutは、NMOSトランジスタN1に流れる電流から電流源13によって供給される電流の分だけ差し引かれる。

(もっと読む)

位相ロックループ回路及び遅延ロックループ回路

【課題】ジッタの増加を防止し、カットオフ周波数の変動を防止することができる位相ロックループ回路及び遅延ロックループ回路を提供することを課題とする。

【解決手段】リファレンス信号とフィードバック信号との位相を比較し、その位相差を示す位相差信号を出力する位相比較器(101)と、前記位相差信号に応じたチャージポンプ電流を出力するチャージポンプ(102)と、抵抗及び容量を含み、前記チャージポンプ電流を平滑化して制御電圧に変換するローパスフィルタ(103)と、前記制御電圧に応じた周波数の発振信号を生成する電圧制御発振器(104)と、前記発振信号を分周した分周信号を生成し、前記分周信号を前記フィードバック信号として前記位相比較器に出力する分周器(105)とを有し、前記ローパスフィルタ内の抵抗は、前記制御電圧に応じて変化する可変抵抗であることを特徴とする位相ロックループ回路が提供される。

(もっと読む)

位相同期発振器

【課題】PLLの位相雑音を低減すること。

【解決手段】電圧制御発振器と、該電圧制御発振器の出力信号と基準信号との位相比較を行い、該位相差に基づいて前記電圧制御発振器に与える電圧を制御する位相比較器とを備える位相同期発振器に、電圧制御発振器の出力信号に対して可変の遅延時間を与える遅延制御手段と、位相比較器で検出した位相差に応じて遅延制御部が出力信号に与える遅延時間を制御する遅延時間制御手段とを有する。

(もっと読む)

通信装置、発振器、並びに周波数シンセサイザ

【課題】CDMAやOFDMといった大きな包絡線変動を伴う変調方式を使用することができ、送信機に線形性と高効率を両立するLINC送信機を提供する。

【解決手段】変調データの周波数変換を行なうPLLにおいて2ポイント変調方式を採用することで、発振器に入力される変調データはPLLにとって外乱とは見えなくなり、PLLのループ帯域幅に制限されない広帯域変調を実現することが可能となる。また、発振器の積分効果により、サンプリング周波数付近におけるレプリカを、アナログ・スムージング・フィルタを追加することなく大幅に抑制することができ、回路のリコンフィギャラビリティを高めることができる。

(もっと読む)

発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置

【課題】デジタルオーディオ回路で使用する第1クロック信号CLKAとDC−DCコンバータで使用する第2クロック信号CLKBとの周波数差によって生ずる可聴周波数帯域のノイズ信号を除去することができる発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置を得る。

【解決手段】発振周波数制御回路23は、第1クロック信号CLKAの第1周波数FAと第2クロック信号CLKBの第2周波数FBとの差が可聴周波数帯域に入ると、第2発振回路21に対して、該帯域に留まらないように第2周波数FBを変化させるようにし、第2周波数FBが可聴周波数帯域に入った場合は、第2発振回路21に対して、第2周波数FBを上昇させて最大可聴周波数以下にならないようにした。

(もっと読む)

遅延ロックループ回路及びその制御方法

【課題】本発明は、動作環境が変化しても、遅延ロックの所要時間の増加を防止できる遅延ロックループ回路及びその制御方法を提供する。

【解決手段】本発明は、基準クロック信号を遅延させて出力する遅延ラインと、基準クロック信号と前記遅延ラインの出力信号との位相差を検出して、位相検出信号及び第1の遅延モード判断信号を出力する位相検出部と、位相検出信号及び第2の遅延モード判断信号により、遅延ラインを制御するための遅延制御信号を出力する制御部と、遅延制御信号及び遅延ラインの出力信号により、第1の遅延モード判断信号のエラーを検出し、エラー検出結果により、第2の遅延モード判断信号を出力するエラー判断部を備える。

(もっと読む)

PLL回路

【課題】安定かつ最適な位相雑音レベルで動作するPLL回路を提供する。

【解決手段】上記課題を解決するために、PLL回路100は、2つの入力信号の位相差に応じた電圧を出力する位相比較器101と、電流変換利得を調整して入力信号を任意の昇圧率で上昇させる可変チャージポンプ102と、所定の周波数特性を有するループフィルタ103と、VCO104と、ループフィルタ103の出力信号をデジタル値に変換するA/Dコンバータ105と、VCO104を選択するともにA/Dコンバータ105の出力値に応じて可変チャージポンプ102を制御するVCO選択回路106と、VCO104からの出力信号を1/N倍に分周する分周回路107と、を備える。

(もっと読む)

位相ロックループ(PLL)のループ帯域幅を較正するシステムおよび方法

位相ロックループ(PLL)のループ帯域幅を較正する方法が記述される。PLLフィルタの中の少なくとも一つの抵抗器は、入力基準信号の周波数に応じて調整される。前記PLLフィルタ中の一つ又は複数の蓄電器は、入力基準信号の周波数に応じて調整される。一つ又は複数の電圧制御発振器(VCO)の出力パルス群が数えられる。対象のループ帯域幅に関連付けられている第1の電荷ポンプ電流は、前記数えられた出力パルス群に従って数えられる。プログラマブル電荷ポンプ電流は、前記計算された第1の電荷ポンプ電流に合わせられる。  (もっと読む)

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、自走した時にも発振周波数を安定に保ち、更に外部からの固定電圧を可変にした制御電圧で発振できる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、PWM回路22と、メモリ21と、制御電圧可変回路26と、位相比較器12とループフィルタ14との接続をオン/オフすると共に制御電圧可変回路26からの制御電圧を選択出力する選択スイッチ13と、当該制御電圧選択の指示で当該制御電圧を優先的に選択出力し、当該指示がない場合に検波回路17で検出された外部基準信号のレベルが適正範囲内であれば選択スイッチ13をオンとし、レベルが適正範囲外であれば選択スイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する。

(もっと読む)

クロック発生回路

【課題】クロック発生回路において、コストの増大を回避すること。

【解決手段】ディジタル位相比較器1、ディジタルループフィルタ2、DDS3、バンドパスフィルタ4、増幅器5、OCXO6および第1分周器7は、ディジタルPLLを構成する。OCXO6から与えられるDDS3の動作周波数をfSとし、DDS3の出力設定周波数をfOとし、nを自然数とすると、DDS3からは、ディジタル/アナログ変換のイメージ成分として、[n×fS±fO]の周波数の信号が出力される。バンドパスフィルタ4は、このイメージ成分の周波数を通過帯域とする特性を有する。

(もっと読む)

PLL回路

【課題】 VCOを構成する電流制御発振回路を制御する電流を生成する電圧−電流変換の動作を高速化して、従来に比較して周波数制御の応答特性を向上させるPLL回路を提供する。

【解決手段】 本発明のPLL回路は、電圧−電流変換回路と電流加算器と電流制御発振回路とから構成され、制御電圧及び制御電流に対応した周波数のパルスを出力する電圧制御発振回路と、パルスと、電圧制御発振回路が生成すべき周波数の基準パルスとの位相差により、第1の制御信号及び第2の制御信号を出力する位相検出器と、第1の制御信号により、第1の充電電流または第1の放電電流を出力する第1のチャージポンプ回路と、第1の充電電流または第1の放電電流により制御電圧を生成し、電圧制御発振回路に出力するループフィルタと、第2の制御信号により、第2の充電電流または第2の放電電流である制御電流を生成し、制御電圧発振回路に出力する第2のチャージポンプ回路とを有する。

(もっと読む)

DLL回路およびその制御方法

【課題】より向上したデューティ比特性を有するクロックを生成する。

【解決手段】本発明は、デュアルループタイプ(Dual Loop Type)のDLL回路であって、第1位相検知信号に応答し、第1遅延制御信号を生成して第1遅延ラインの遅延量を制御し、第1遅延量情報信号を出力する第1遅延制御手段と、第2位相検知信号に応答し、第2遅延制御信号を生成して第2遅延ラインの遅延量を制御し、第2遅延量情報信号を出力し、前記第1遅延制御信号と半周期情報信号に応答して前記第2遅延ラインの遅延量を再び制御する第2遅延制御手段と、前記第1遅延量情報信号と前記第2遅延量情報信号の入力を受け、基準クロックの半周期情報を抽出して前記半周期情報信号を生成する半周期検知手段と、前記第1遅延ラインの出力クロックと前記第2遅延ラインの出力クロックを組み合わせてデューティ比補正クロックを出力するデューティーサイクル補正手段とを含む。

(もっと読む)

半導体集積回路

【課題】マルチバンド無線通信のための複数のミキサーに複数のローカル信号を供給するための複数の分周器の入力を電圧制御発振器の発振出力信号により効率的に駆動すること。

【解決手段】半導体集積回路は、第1と第2と第3のミキサー(25、26、28)と、電圧制御発振器(VCO)16と、第1と第2と第3の分周器(11、12、14)と、信号配線とを具備する。第1分周器11と第3分周器14の第1分周数は、第2分周器12の第2分周数よりも小さな値に設定されている。第1と第2と第3の分周器(11、12、14)の分周出力信号は、第1と第2と第3のミキサー(25、26、28)に供給される。信号配線の略中央にVCO16と第2分周器12とが接続され、信号配線の一端と他端とには第1分周器11と第3分周器14とがそれぞれ接続される。第1分周器と第3分周器の入力に、第1と第2のバッファ電圧増幅器BUFがそれぞれ接続される。

(もっと読む)

321 - 340 / 713

[ Back to top ]