Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

361 - 380 / 713

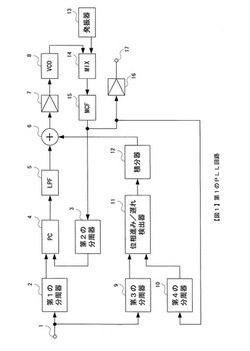

PLL回路

【課題】 ループゲインを大きくすることができ、ループ利得が上がらない場合でも、ロック時の位相ノイズを良化できるPLL回路を提供する。

【解決手段】 入力端子1からの基準周波数を第1,3の分周器2,9で分周し、VCO8からの出力と発振器13からの出力をミキサ14で合成し、MCF15aで周波数を選択して、第2,4の分周器3,10で分周し、第1,第2の分周器2,3からの出力を位相比較器4で位相比較し、LPF5で平滑化し、第3,第4の分周器9,10からの出力を位相進み/遅れ検出器11で位相の進み又は遅れを検出し、積分器12で積分して電圧を出力し、加算器6でLPF5からの出力と積分器12からの出力を加算してVCO8に出力し、MCF15aからの出力を増幅器16で増幅して出力端子17に出力し、基準周波数に対して発振器13での周波数を調整するPLL回路である。

(もっと読む)

信号再生装置

【課題】受信したDVB−ASI信号からジッタなどによる位相変動を抑制したクロックを再生可能とする。

【解決手段】パラレル変換されたDVB−ASI信号の各TSパケットの47hコードが、47コード検出器4により、検出された47hコードパルスEが得られ、適応型位相代替回路5を介してPLL回路の位相比較器13に供給され、分周器8からの位相基準クロックF1と位相比較される。ジッタなどによって47hコードパルスEの位相が大きく急変し、位相基準クロックF1との位相差が異常に大きい場合には、適応型位相代替回路5は、かかる47hコードパルスEに代わる代替パルスを位相比較器13に供給する。これにより、VCO15の制御電圧の急変を抑えることができ、安定した基準クロックFが得られる。

(もっと読む)

位相同期ループ周波数合成に於ける低雑音化の方法

【課題】位相ジッタの少ない位相同期ループ回路を実現する。

【解決手段】第一および第二レジスタへ接続された第一および第二計数手段10,14を含む位相同期ループ回路が開示される。第一レジスタ18は数Mを第二レジスタ20は数Nを記憶する。第一計数手段は基準信号FrefのMサイクルに応答してF1出力信号を出力し、第二計数手段は出力信号FoutのNサイクルに応答してF2出力信号を出力する。F1,F2,Fref,Fout 信号は、位相検出器30へ接続され、FrefとFoutの位相が比較される。位相検出回路の出力信号は位相検出回路出力信号に比例したFout信号を発生する電圧制御発振器12に接続される。Fout信号は位相同期ループ回路が整定するまで第二レジスタへフィードバックされる。

(もっと読む)

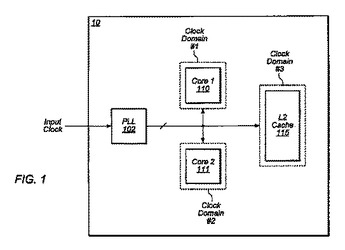

クロックサイクルスチールのための方法および装置

複数のクロック信号を生成するための方法。前記方法は、位相ロックループ(PLL)を使用して基準クロック信号を生成するステップを有する。前記基準クロックが、複数のクロック分周器ユニットのそれぞれに供給され、前記複数のクロック分周器ユニットのそれぞれが、前記受信基準クロック信号を分周して、対応する分周クロック信号を生成する。前記方法は、前記対応する受信分周クロック信号の周波数と、除去するサイクル数とに基づいて、それぞれが有効周波数を有する複数のドメインクロック信号を生成するために、(所定の数のサイクルにつき)1以上のクロックサイクルを除去する。  (もっと読む)

(もっと読む)

発振器及びそれを用いた位相同期ループ回路

【課題】制御信号だけではなく、周波数も制御可能な変調機能を有する発振器、及びその発振器を用いた位相同期ループ回路を提供する。

【解決手段】出力信号の帰還信号と基準信号との位相を比較して、位相差を示す信号を出力する位相検出器1081と、位相検出器1081の出力信号が供給され、位相差をなくすための制御信号を出力するループフィルタ1082と、ループフィルタ1082からの制御信号に基づく周波数で発振する発振器1083とを備え、発振器1083は、制御信号に変調信号を加えることによって周波数を変調する変調手段を備える位相同期ループ回路(PLL回路)。

(もっと読む)

信号分配装置

【課題】分周器の広帯域かつ低電圧動作を保障する。

【解決手段】信号分配装置は、第2制御信号に従って動作し、参照周波数に従って発振周波数を調整する調整部を有する位相同期ループ回路101と、電流源負荷を有し、前記調整部によって調整された発振周波数を分周してI/Q信号を生成する分周器102と、第1制御信号に従って自走発振周波数を生成する自走発振周波数生成器105と、前記参照周波数と前記自走発振周波数を比較する比較部103A及び前記比較部103Aの比較結果に従って前記第1制御信号又は前記第2制御信号を生成する制御部103Bを有する自走発振周波数制御回路103と、前記分周器102によって生成された前記I/Q信号を用いて送信又は受信を行う通信回路104と、を備えている。

(もっと読む)

PLL発振回路

【課題】分数分周型のPLL発振回路における抵抗やキャパシタの定数を小さくすると共に、雑音を低減する。

【解決手段】入力信号INと帰還信号FBaの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10aと、入力信号INと帰還信号FBbの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10bと、このノードNcに出力される信号の高周波成分を除去して制御電圧VCを生成するループフィルタ20と、制御電圧VCに応じた周波数foの出力信号OUTを生成するVCO30と、出力信号OUTの周波数をそれぞれ1/Mと1/Nに分周して帰還信号FBa,FBbを出力する分周器40a,40bを設ける。

(もっと読む)

PLLシンセサイザー回路

【課題】 電源変動等が生じると、外部からの割込信号により不定期間を待って再度分周データをPLLシンセサイザーICに書き込むことで、安定的にロック状態に復帰させることができるPLLシンセサイザー回路を提供する。

【解決手段】 PLLシンセサイザーIC106の電源投入時又は電源変動時にマイクロプロセッサ(CPU)104への割込を監視手段が発生させ、CPU104はPLLシンセサイザーIC106の電源投入後又は電源変動後の不定期間に相当する期間を待って、分周データをPLLシンセサイザーIC106に出力して書き込みを行い、更に分周データ出力後にロック状態となるまでの期間ウエイトするPLLシンセサイザー回路である。

(もっと読む)

位相調整装置

【課題】設計時以降に生じる位相差の変動を内部で自動的に調整することで、予め設定された位相差を有する2つの信号を出力する。

【解決手段】2つのクロック信号の位相差を予め定められた位相差に調整する位相調整装置であって、第1クロック信号に対する第2クロック信号の遅延量を選択的に変更可能な遅延部11と、前記遅延量を制御する制御部12とを備え、前記制御部12は、準備モードにおいて、前記遅延量を第1の時間間隔で段階的に増加又は減少させ、遅れ期間、又は、進み期間を検出し、調整モードにおいて、前記遅れ期間又は前記進み期間と同じ長さの期間において第2の時間間隔で前記遅延量を段階的に変化させることで、前記第2クロック信号の位相差を予め定められた位相差に調整し、前記第2の時間間隔と前記第1の時間間隔との比は、180度と予め定められた位相差との比に等しい。

(もっと読む)

電流制御回路および電流制御装置

【課題】簡単な回路構成で、高速動作と、出力電流のグリッチの低下を実現する。

【解決手段】電流源トランジスタ212は、端子255から引き込む電流を決定する。スイッチトランジスタ222は、DN信号に応じて、電流源トランジスタ212に電流を流す。カスコードトランジスタ232は、スイッチトランジスタ222と端子255との間に接続される。容量242は、カスコードトランジスタ232と、スイッチトランジスタ222との間に接続され、xDN信号に応じて、交流的に電荷を注入または放出する。本発明は、例えば、チャージポンプに適用することができる。

(もっと読む)

発振回路

【課題】高精度な発振回路を提供する。

【解決手段】例えば、奇数段のインバータ回路IVを含んだ複数のリングオシレータ部RO1,RO2と、このRO1,RO2の出力ノードRO_O1,RO_O2の信号を加算する加算部ADDを設ける。そして、このADDの加算結果をクロック信号として出力ノードOSC_Oから出力すると共に、この出力ノードOSC_OをRO1,RO2の入力ノードRO_I1,RO_I2に帰還する。これによって、例えばRO1,RO2の遅延時間がそれぞれ標準偏差σの正規分布に基づいてばらつく場合に、OSC_Oから得られるクロック信号のばらつきをσ/√2とすることが可能となる。

(もっと読む)

分周器及び高周波発振源

【課題】容易に、効率良く複数の出力波を取得できる分周器を得る。

【解決手段】第1の入力端子2a、並びに第1及び第2の出力端子3a、3bを有し、第1及び第2の出力端子3a、3bからは逆相の出力が得られる分周数N(N:2以上の整数)の分周回路1と、第1及び第2の出力端子3a、3b間に接続される第1の伝送線路4aとを設け、第1又は第2の出力端子3a、3bの少なくともいずれか一つから入力波のN分周波を取り出すとともに、第1の伝送線路4aの中点から入力波のN/2分周波を取り出す。

(もっと読む)

PLL回路、記録装置及びクロック信号生成方法

【課題】入力信号の振幅変動によるPLL回路の位相誤差を簡便に低減することができるPLL回路、記録装置及びクロック信号生成方法を提供する。

【解決手段】所定の周波数を有する入力信号に同期したクロック信号を生成するPLL回路100を提供する。このPLL回路100は、クロック信号を発振する発振器110と、発振器110が発振したクロック信号をサンプリングクロックとして用いて、入力信号をデジタル信号に変換する変換器120と、発振器110が発振したクロック信号を分周し、比較クロック信号としてフィードバックする分周器140と、変換器120が変換したデジタル信号の振幅値を正規化する正規化器130と、正規化器130が正規化したデジタル信号と分周器140がフィードバックした比較クロック信号との位相差を減少させるように、発振器110が発振するクロック信号の位相を制御する発振制御器150と、を備える。

(もっと読む)

高周波発振源

【課題】長いディレイラインを用いることなく、信号波の位相雑音を低減することができる高周波発振源を提供する。

【解決手段】周波数変換器2と、中心周波数f0の帯域通過フィルタ3と、2分周器4とを直列接続したものを1段の基本構成として、前記基本構成を(N−1)段(N:2以上の整数)直列接続し、前記第1段目の周波数変換器における第1の入力端子及び前記第1段目から第(N−1)段目の周波数変換器における第2の入力端子に接続されてそれぞれに設けられた発振周波数f0の発振器1,1aを備えた高周波発振源。

(もっと読む)

磁場計測装置

【課題】光ポンピング磁力計の磁場検出性能を向上させるために蒸気セルの保温を行う際に、希望の温度に迅速に達し、蒸気セルのレーザー照射光部への蒸気セル内の原子の付着を防ぎ、蒸気セル周辺部を小型化にし、蒸気セルを保温するヒーターからの磁場の影響を抑える。

【解決手段】光ポンピング磁力計の磁気検出部である蒸気セル119のレーザー照射光通過部に透明フィルムヒーター118と、蒸気セル側面中央部に測温体115と、蒸気セル119を保温する希望温度との設定ならびに、希望温度と測温体115で測定した実際の蒸気セル温度との比較を行う温度調節器111と、温度調節器111からの温度制御のためのPID制御信号を受けて温度調整と希望温度到達後の透明フィルムヒーター118への通電をパルス的に切り替える操作器112と、操作器112からの操作信号を受けて透明フィルムヒーター118への通電を行うヒーター用電源113を有する。

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

半導体装置

【課題】高速応答性と動作の安定化を実現したPLL回路を備えた半導体装置を提供する。

【解決手段】低電源電圧VddLで動作する位相比較回路の低振幅信号を夫々高電源電圧で動作するNチャネルMOSFET入力構成の第1差動回路とPチャネルMOSFET入力構成の第2差動回路に入力する。上記第1及び第2差動回路の負荷としてダイオード接続MOSFETとクロスカップル接続のMOSFETを並列構成にして用いる。ゲートに所定のバイアス電圧が供給されたPチャネルMOSFET,NチャネルMOSFETを直列接続する。上記PチャネルMOSFETのソースは、上記第1差動回路の出力信号で制御し、NチャネルMOSFETのソースは、上記第2差動回路の出力信号で制御し、PチャネルMOSFET及びNチャネルMOSFETのドレインからアップ電流又はダウン電流を形成する。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

周波数同期システム及び周波数同期方法

局部発振器からの局部信号と遠隔発振器からの基準クロック信号の間で周波数を同期させるデジタル周波数ロックループに関連するシステムおよび方法。基準カウンタは、基準クロック信号内のパルスごとにその計数を増分する。基準カウンタ内の値は、設定可能な基準値と比較される。基準カウンタ値と基準値の一致が発生するたびに、ヒット信号が生成され、基準カウンタ値が再初期化される。上記と同時に、局部信号からのパルスごとにフィードバックカウンタが増分される。ヒット信号が生成されると、フィードバックカウンタ内の値が設定可能なフィードバック値と比較(減算による)されて、差の値を生成する。次いで差の値が、局部発振器の周波数を増大または減少させるのに使用するための周波数調整信号に変換される。ヒット信号はまた、フィードバックカウンタを再初期化する。 (もっと読む)

シンセサイザ装置及びこれを備える携帯通信端末

【課題】デュアルシンセサイザ装置において、基板の定在波比が劣化しても、簡単な構成でアイソレーションの低下を防止する。

【解決手段】プリント基板13上には第1及び第のPLLシンセサイザ部11及び12が配置され、第1及び第2のPLLシンセサイザ部には基板に形成された配線パターン13aを介して基準発振器14から基準信号が与えられ、選択スイッチ(SW)45によって第1及び第2のPLLシンセサイザ部からの出力信号のうちいずれか一方が選択される。配線パターンのインダクタンスとこのインダクタンスと対向するアースパターンからなる第1及び第2のコンデンサとによってローパスフィルタが構成される。

(もっと読む)

361 - 380 / 713

[ Back to top ]