Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

341 - 360 / 713

クロック信号発生回路

【課題】簡単な回路構成により、低速の基準クロックから高速のクロック信号を生成することができ、高速クロック信号の周波数選択の制限を緩和することができるクロック信号発生回路を提供すること。

【解決手段】クロック信号発生回路100は、低速の基準クロック信号S1を発生する基準クロック信号発生回路110と、基本クロック信号発生回路110からの低速の基準クロック信号S1をN1逓倍し、逓倍出力S2を出力するPLL回路130と、PLL回路130の逓倍出力S2を1/N分周し、低速の基準クロック信号S1よりも高速の第2の基準クロック信号S3を出力する分周回路140と、分周回路140の第2の基準クロック信号S3をN2逓倍し、高速のクロック信号である逓倍出力S4を出力するPLL回路150とをこの順序で備える。

(もっと読む)

PLL装置、映像同期制御装置及び表示装置

【課題】コストを抑えつつ、外部同期信号と内部同期信号との同期スピードを早くすることができるPLL装置、映像同期制御装置及び表示装置を提供する。

【解決手段】位相差比較部11が外部同期信号とフィードバックされて入力される内部同期信号との位相差を検出する。位相差判定部12は、検出された位相差が所定のしきい値以上であるか否か又は所定のしきい値未満であるか否かを判定する。VCXO18は、位相差判定部12の判定結果に応じて、フィードバックされる出力信号の周波数を可変する。

(もっと読む)

クロックリカバリ回路

【課題】 クロック信号の切り替え時における不要成分の発生を効果的に抑制できるクロックリカバリ回路を提供する。

【解決手段】 異位相の選択クロック信号を複数の選択クロック信号群に分類し、前段選択制御信号により選択クロック信号の1つを前段出力クロック信号として出力する前段選択回路を、選択クロック信号群毎に備える前段選択回路群14と、後段選択制御信号により前段出力クロック信号の1つを再生クロック信号RCLKとして出力する後段選択回路15と、受信データと再生クロック信号RCLKの位相差に基づいて位相制御信号を出力する位相制御回路11と、位相制御信号により特定される選択クロック信号を選択する前段選択制御信号を出力する前段選択制御回路12と、切り替えが必要な場合に、現在の前段出力クロック信号と新たな前段出力クロック信号の論理値が同じになる期間に後段選択制御信号を出力する後段選択制御回路13を備える。

(もっと読む)

通信装置、及びそのシステムクロック制御方法

【課題】 受信バッファ量を増減させずに、IP網の揺らぎに対処する。

【解決手段】 通信装置であるIP−PBX100は、IP網5からのパケットを一時的に溜める受信バッファ32と、受信バッファに溜まったパケットをシステムクロック信号に同期して順次処理するパケット処理部33と、受信バッファに溜まっているデータ量を検出するバッファデータ量検出部40と、バッファデータ量検出部で検出されたデータ量に応じた周波数のシステムクロック信号を発振するシステムクロック発振部50と、を備えている。

(もっと読む)

半導体装置

【課題】発振信号を出力し、かつ低消費電力化を図ることが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1の制御電圧に応じた周波数で発振することにより発振信号を出力する電圧制御発振回路5と、電圧制御発振回路5から受けた発振信号の周波数を電圧に変換する周波数/電圧変換回路2と、周波数/電圧変換回路2によって変換された電圧と前回生成した第2の制御電圧との間のレベルを有する新たな第2の制御電圧を生成する制御電圧生成回路11と、第2の制御電圧を積分することにより第1の制御電圧を生成し、第1の制御電圧を電圧制御発振回路5へ出力するアナログ積分回路3とを備える。

(もっと読む)

位相同期回路およびそれを用いた半導体集積回路装置

【課題】プロセスばらつき、環境変動によらず、所望の特性を満足する自動調整できる位相同期回路を提供すること。

【解決手段】位相同期回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ3、分周器6、セレクタ7、電圧制御発振器8を備えている。分周器6は、出力信号と基準信号を入力して出力信号を分周して帰還信号を出力するとともに出力信号から選択信号とトリミング信号とリミット信号を出力する。電圧制御発振器8は、制御電圧と基準電圧とトリミング信号とリミット信号を入力して制御電圧に応じて出力信号周波数を変え、出力信号の上限周波数を制限できるとともに、トリミング信号によって制御電圧に対して出力する出力信号の周波数感度と、リミット信号によって出力信号の上限周波数を変えることができる。

(もっと読む)

注入同期型発振器

【課題】より小型化が可能な周波数逓倍器を提供する。

【解決手段】注入同期型発振器20は、インバータ(22a、22b、22c)を3段リング状に接続してリングオシレータを備えている。そして、2段目のインバータ22bの出力と、3段目のインバータ22cの出力とをnMOSトランジスタ24で接続する構成を採用している。このnMOSトランジスタ24のゲートは、外部から基準周波数信号が供給される。このような構成によって、、リングオシレータの自励発振周波数に近い周波数であって、注入された基準周波数信号と同期した整数倍の周波数で発振が行われる。このように、インジェクションロックを用いて、位相雑音を減らすことができるので、ループフィルタを必要とせず、より小面積で周波数逓倍器を構成することが可能である。

(もっと読む)

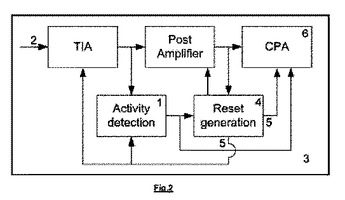

TDMAネットワークにおける信号検出のための装置及び方法

本発明は、バーストモード受信機における動作状態を検出するための回路(1)に関する。本回路は、プリアンブルを含む入力信号(2)を受けるように構成される。本回路は、入力信号(2)における信号遷移を検出する微分器(11)を備え、微分器(11)を動作させる情報をそのプリアンブルが含む。好ましい実施形態において、上記情報は時定数である。本回路は、微分器の出力が供給されるように構成された積分器(12)をさらに備える。結果として得られる信号は基準(16)に対して比較される。この基準と交差するとき、動作状態が検出される。ある実施形態ではフロントエンド回路が提供され、フロントエンド回路は、動作状態を検出する回路の後段に、フロントエンド回路をリセットするように構成されたリセット回路と、位相を復元するように構成されたクロック位相アラインメント回路を備える。  (もっと読む)

(もっと読む)

高速スイッチング低ノイズチャージポンプ

本発明のある実施形態において、チャージポンプの方法が開示されている。その方法は、複数のトランジスタをバイアスすることと、バイアストランジスタを通して出力端子で正味電荷を加えたり除去したりするためにペアのメイントランジスタスイッチを切り換えることと、メイントランジスタスイッチがオフにされる時、補助トランジスタスイッチをオンにすることとを含む。補助トランジスタスイッチは、オンの時、メイントランジスタスイッチとバイアストランジスタとの間のノードに補助等化経路を提供する。補助等化経路は、バイアストランジスタを急速にオフにするため、及び、チャージポンプの出力端子のノイズを削減するために、中間ノード同士の電圧を均等化する。 (もっと読む)

局所発振回路

【課題】消費電力を低減できる局所発振回路を提供する。

【解決手段】周波数fsの基準振動信号と周波数fout/(m×n)の分周信号の位相を比較する位相比較器1と、上記両信号の位相のずれに応じた電流IOUTを出力する電荷ポンプ10と、上記出力電流IOUTに応じた制御電圧VCを生成するループフィルタ3と、上記制御電圧VCに応じた発振周波数foutの信号を出力する電圧制御発振器4と、電圧制御発振器4の出力信号を設定周波数に応じた分周値(m×n)で分周して上記分周信号を出力する前置分周器5および可変カウンタ6とを備え、上記発振周波数foutを上記設定周波数に引き込む局所発振回路において、上記電荷ポンプ10は、出力電流IOUTの値を上記設定周波数に応じて切り換える。

(もっと読む)

PLL回路及び無線通信システム

【課題】複数の発振周波数帯域を有するVCOを備えたPLL回路において、設定されたPLL出力周波数に対応する最適な発振周波数帯域の検出動作に要する時間を短縮する。

【解決手段】TDC回路30は、固定分周器2からの所定の基準信号11の立ち上がり時に、その基準信号11と可変分周器7のPLL分周信号15との位相差を求め、更に、前記基準信号の次の立ち上がり時においても同様に、その基準信号とPLL分周信号15との位相差を求める。その求めた2つの位相差情報により、基準信号11の1周期の間にPLL分周信号15が基準信号11に対して進んだ又は遅れた位相量を検出して、基準信号11とPLL分周信号15との周波数の高低を検出する。よって、1つの発振周波数帯域に対して、基準信号11の1周期で周波数比較を完了でき、発振周波数帯域選択回路8は、設定されたPLL出力周波数に対応する最適な発振周波数帯域を短時間で検出する。

(もっと読む)

スペクトラム拡散クロック生成器

【課題】その設計の困難性を低減することができるスペクトラム拡散クロック生成器を提供する。

【解決手段】スペクトラム拡散させたクロック信号CLKOを生成するスペクトラム拡散クロック生成器1において、クロック信号CLKOを所定の分周比で分周して、分周信号を出力する分周器14と、入力される基準クロック信号CLKRと分周信号CLKFの位相差に応じてレベルが変化させた位相差信号Spを出力する位相比較器10と、位相差信号Spに応じた発振制御信号Scを生成する発振制御信号生成器11と、発振部を有し、発振制御信号Scのレベルに応じた電流を発振部に供給して、発振制御信号Scのレベルに応じた発振周波数で発振部を発振させ、クロック信号CLKOを出力する電圧制御発振器12と、発振部に供給する電流を増減させる変調電流Imを生成し、電圧制御発振器12へ供給する変調電流生成器15とを備える。

(もっと読む)

局部発振器制御装置

【課題】PLL回路のループ動作を安定化でき、処理負荷が軽減された局部発振器制御装置を提供する。

【解決手段】基準信号と分周信号との位相を比較し、位相差に応じた位相誤差信号を出力する位相比較器1と、前記位相誤差信号に応じた電流信号を出力するチャージポンプ回路2と、前記電流信号を平滑化して制御電圧を出力するローパスフィルタ3と、前記制御電圧に応じた周波数の発振信号を生成して出力する電圧制御発振器4と、前記発振信号を所定の分周比により分周して前記分周信号を生成する分周器5と、前記制御電圧を所定時間積分し、積分結果を出力する積分器6と、前記積分結果と所定の閾値とを比較し、比較結果に基づいて前記電流信号の電流値を調整する電流制御信号を生成しチャージポンプ回路2へ出力する制御部8と、を備える。

(もっと読む)

精密集積位相ロック回路用ループ・フィルタ

【課題】基準精密抵抗器と、第1のFETのゲートが第2のFETのゲートに結合されている第1のFETおよび第2のFETと、第1のFETに接続されコンデンサ電圧を発生させるフィルタ・コンデンサとを含む位相ロック・ループ回路内のループ・フィルタが提供される。

【解決手段】コンデンサ電圧は、第1のFETのソース、第2のFETのソース、および仮想グラウンドとして機能する基準精密抵抗器の底部に印加される。フィルタ・コンデンサによって生成されるコンデンサ電圧は、第2のFETが集積精密抵抗器の特性を含むように、第2のFETのバイアス点を設定する。第2のFETによって生成される所定の電圧は、第1のFETのゲートに印加されて、第1のFETが集積精密抵抗器の特性を含むように、第1のFETのバイアス点を設定する。

(もっと読む)

クロック発生回路

【課題】高精度な周波数変調が可能なスペクトラム拡散クロック発生回路を提供する。

【解決手段】このスペクトラム拡散クロック発生回路において、PLL回路31は、それぞれ位相の異なるクロック信号CLKV1〜CLKV5を出力する。セレクタ23は、クロック信号CLKV1〜CLKV5のうちのいずれか1つを選択し、制御回路24はセレクタ9の信号選択動作を制御する。入力分周回路1は選択クロック信号を分周して基準クロック信号CLKRを出力する。PLL回路21は、基準クロック信号CLKRを周波数逓倍した発振クロック信号CLKOを生成する。これにより、発振クロック信号CLKOの位相を微調整することができる。したがって、高精度な周波数変調が可能なスペクトラム拡散クロック発生回路が実現できる。

(もっと読む)

位相ロックループ回路

【課題】出力クロック信号の周波数を高精度で制御することができる位相ロックループ回路を提供する。

【解決手段】制御電圧を保持する容量(104)と、リファレンスクロック信号に対するフィードバック信号の位相差を検出する位相検出器(101)と、前記検出された位相差に応じて、前記容量を電源電圧又は基準電位に接続する第1のスイッチ回路(SW1,SW2)と、前記容量の制御電圧に応じた発振周波数の出力クロック信号を生成し、前記出力クロック信号又は前記出力クロック信号に応じた信号を前記フィードバック信号として前記位相検出器に出力する電圧制御発振器(105)と、前記リファレンスクロック信号のエッジから一定期間又は前記出力クロック信号若しくは前記出力クロック信号に応じた信号のエッジから一定期間前記容量を前記基準電位又は前記電源電圧に接続する第2のスイッチ回路(SW3)とを有する位相ロックループ回路が提供される。

(もっと読む)

光絶縁チャンネルを介した高耐性クロック再生

【課題】経済的、高性能、低電力の光学的に絶縁された装置を提供する。

【解決手段】光絶縁回路装置は第1のクロック信号によって駆動される第1のオプトアイソレータ回路を含み、第1のオプトアイソレータ回路の出力は、第1のクロック信号周波数の倍数である周波数を有する第2のクロック信号を同期させるように構成された位相ロックループ(PLL)を駆動するために使用される。第2のクロック信号は、アナログ・デジタル変換器(ADC)などの光絶縁から恩恵を受けるタイプの適当なクロック回路への入力として使用される。

(もっと読む)

位相ロックループ回路

【課題】広周波数範囲で動作可能であり、電圧制御発振器のゲインを低減させることができる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号及びフィードバッククロック信号の位相差を検出する位相差検出器(101)と、制御電圧を保持するコンデンサ(117)と、前記検出された位相差に応じて、前記コンデンサを電源電圧又は基準電位に接続するチャージポンプ回路(102)と、前記制御電圧に応じた発振周波数の出力クロック信号を生成し、前記出力クロック信号又は前記出力クロック信号に応じた信号を前記フィードバッククロック信号として前記位相差検出器に出力する電圧制御発振器(104)とを有し、前記電圧制御発振器は、4段の差動リングオシレータ(131〜134)と、前記4段の差動リングオシレータの異なる段で出力されるクロック信号の排他的論理和信号を出力する第1の排他的論理和回路(127)とを有する。

(もっと読む)

受信回路及び電子機器

【課題】PLLの低消費電力化、回路規模の低減、設計の困難性の低減。

【解決手段】所定の局部発振周波数IPA,QPAを出力する局部発振回路110を含み、受信信号RFと局部発振周波数IPA,QPAとを乗算した中間周波信号Iin,Qinを出力するアナログ直交復調回路100と、中間周波信号Iin,Qinを入力しフィルタ信号Iout,Qoutを出力する中心周波数と通過帯域とのどちらか少なくとも一方を可変にできる可変バンドパスフィルタ200と、フィルタ信号Iout,Qoutをデジタル信号Idi,Qdiに変換するアナログ−デジタル変換回路310,320と、所定の数値制御発振周波数IPB,QPBを出力する数値制御発振回路410を含み、デジタル信号Idi,Qdiと数値制御発振周波数IPB,QPBとを乗算した復調信号Idm,Qdmを出力するデジタル直交復調回路400と、を含む受信回路。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報を元に得られるAGC回路における補正値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出するようにした周波数シンセサイザである。

(もっと読む)

341 - 360 / 713

[ Back to top ]