Fターム[5J106CC53]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990) | 可変分周回路 (277)

Fターム[5J106CC53]に分類される特許

261 - 277 / 277

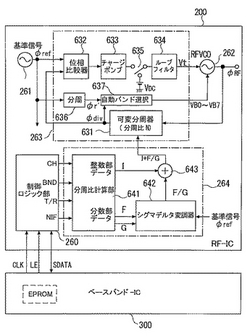

通信用半導体集積回路

【課題】 広い周波数範囲で高精度に発振動作ができ、占有面積を増大させずにVCOの使用周波数帯を短時間に選択できる通信用半導体集積回路の提供。

【解決手段】 発振器と発振信号を任意の分周比(整数I+分数F/G)で分周可能な可変分周器とを有する発振回路を備えた通信用半導体集積回路で、外部からの送信開始指示と使用周波数帯情報により、可変分周器に与える分周比を算出の分周比算出回路と、分周比算出回路により算出の分周比により可変分周器を動作させ、発振器に所定レベルの電位を制御電圧として供給した状態で可変分周回路の出力信号の位相と基準信号を分周する固定分周回路の出力信号の位相とを比較して発振器の発振周波数帯を選択のバンド選択回路とを設け、バンド選択回路により発振器の発振周波数帯を選択後、発振器の制御電圧もしくは制御電流を周波数制御回路の出力に切り替えて発振回路を動作させる。

(もっと読む)

PLL回路のノイズを抑制するシステム及び方法

位相ノイズおよび内部発生器内のミスマッチによって発生するノイズを抑制して周波数ジェネレータのSNRを向上させるシステム及び方法である。このノイズ抑制はスプリアスノイズ信号を発生器のループ帯域幅外にシフトする変調方式によって行われる。このシフトにより、例えば発生器の信号パス上のフィルタを使用して、ノイズ信号を完全に除去できるか又は所望の程度まで除去できる。一実施形態では、所望の程度のノイズ抑制を行うため、シグマデルタ変調器により、PLL回路のフィードバックパス上のパルススワロ分周器の値が制御される。別の実施形態では、PLL回路に入力されるレファレンス信号を変調することにより、ノイズが抑制される。別の実施形態では、所望の周波数シフトを行うため、前記の変調形式が組み合わされる。これら変調技術により、ロックタイムがより速くなるとともに、周波数ジェネレータのSNRが大幅に向上する。  (もっと読む)

(もっと読む)

通信用半導体集積回路

【課題】 使用周波数帯を決定するまでに要する時間が長くならないとともに回路の占有面積を小さくすることができ、また、リセット信号等の遅延により誤った周波数帯が選択されない自動バンド選択回路を備えたPLL回路を内蔵した高周波ICを提供する。

【解決手段】 VCO11の発振周波数を制御するPLLループにおいて、所定の周波数の基準信号に対する可変分周回路12の出力の位相の進みまたは遅れを判別する判別回路22と、該判別回路の出力に基づいてVCOの周波数帯を切り替える信号を生成する自動バンド選択回路20と、信号の遅延に基づく位相判別におけるずれを測定しそれを補償するような遅延を固定分周回路14で分周された信号に与える遅延補償回路25とを設け、2分探査方式でVCOの周波数帯を切り替えながら最適な周波数帯を見つけて使用周波数帯を決定するようにした。

(もっと読む)

PLL回路を内蔵する半導体集積回路

【課題】 発振回路と位相比較回路とチャージポンプ回路とループフィルタを含むPLL回路において、複数の容量素子を設けることなくつまり占有面積をそれほど増大させることなくPLLの特性を抵抗素子や容量素子の製造ばらつきに応じて調整することができ、それによってループフィルタをオンチップ化できるようにする。

【解決手段】 ループフィルタ(17)を構成する抵抗素子と容量素子を半導体チップに形成しこのうち抵抗素子は抵抗値の異なる複数の素子を設けてスイッチにより切り替えることで抵抗値を調整可能に構成し、またチャージポンプ回路(16)の電流も調整可能に構成し、抵抗素子の抵抗値の切り替えに応じてチャージポンプ回路の電流を調整するようにした。

(もっと読む)

位相同期回路

【課題】 分周値を記憶する記憶部の容量が少なくてすむ位相同期回路を提供する。

【解決手段】 整数部と分数部からなる分周値を切り換えることにより、可変分周器の分数分周を行なう位相同期回路において、

前記分数部を記憶する記憶部と、

前記可変分周器のクロックに基づいて前記記憶部から出力された前記分数部に前記整数部を加え、前記可変分周器に出力する分周値を決定するROMデータ変換部と

を備えることを特徴とする位相同期回路。

(もっと読む)

基準クロックの周波数補正方法

【課題】コストアップを抑制し、常に安定した周波数の基準クロックを生成することができる基準クロックの周波数補正方法を提供する。

【解決手段】μcom1にて、ドライバーIC2の内蔵発振回路21の原振クロック又はその分周クロックを取得し、取得された原振クロックの周波数に関する情報を計測し、計測した周波数に関する情報に基づいて基準クロックの周波数の補正値を算出し、算出した補正値をμcom1からドライバーIC2に送信する。そして、送信されてきた補正値に基づいて、ドライバーIC2にて基準クロックの周波数を補正する。よって、高価な水晶発振子を含む水晶発振回路が不要となる。また、電源投入のタイミングを待つことなく、基準クロックの周波数を補正することが可能になる。

(もっと読む)

複数のデジタルクロックの高速同期化方法およびシステム

【課題】異なる周波数でも可能な、自動テスト装置(ATE)のチャネル間の位相と周波数同期化を提供することのできる方法およびシステムを提供する。

【解決手段】本発明は、複数のデジタルクロック(PCLK)を同期信号(SYNC)に同期させる方法を提供する。方法は、基準クロック(RCLK)を中央で生成するステップと、基準クロック(RCLK)からデジタルクロック(PCLK)を、クロック乗算手段を用いて合成するステップと、クロック乗算手段を同期信号(SYNC)に応答してリセットするステップと、クロック乗算手段の出力信号(VCLK)をクロック乗算手段の整定時間中、マスキングするステップと、を含む。

(もっと読む)

モノリシックなクロック・ジェネレータおよびタイミング/周波数リファレンス

電力節約モード、クロック・モード、リファレンス・モード、およびパルス化モードなどの複数の動作モードと共に、クロック・ジェネレータおよび/またはタイミングおよび周波数のリファレンスを提供する。共振周波数を有する第1の信号を供給するようになっている共振器と、増幅器と、温度に応じてこの共振周波数を修正するようになっている温度補償器と、製造プロセス変動に応じてこの共振周波数を修正するようになっているプロセス変動補償器とを含んでいる。さらに、実質的にこの共振周波数以下の対応する複数の周波数を有する複数の第2の信号に、この共振周波数を有する第1の信号を分周するようになっている周波数分割器と、これらの複数の第2の信号から1つの出力信号を供給するようになっている周波数セレクタとを含むことができる。  (もっと読む)

(もっと読む)

周波数分割器を有する装置

セクション(21−27)を有する周波数分割器(2)は、調整信号(p,,)に依存して、かつ、後のセクションから生じる制御信号(c,,)に依存して、調整可能な数によって、周波数信号(f,,)を分割する第1種の基本セクション(21、22、23)を備えており、付加的な回路55、56、64、66、67を有する第2種の高度なセクション(22)を備えている。この付加的な回路55、56、64、66、67は、限られた数の早いセクションに対して実施されるべき何らかの変調を可能にし、後のセクションは影響を受けない。結果として、周波数分割器(2)は、例えば、いかなる変調も適応化される必要なしに、アクティブ及び非アクティブモードを有するプログラム可能なセクション(26、27)によって拡張されることができる。これに対し、回路55、56、64、66、67は、変調信号(mo、ml)及び付加的な制御信号(c3)を受け取る。前記のような周波数分割器(2)は、コストが低く、信頼でき、ロバスト性を有し、容易に実施化されることができる。  (もっと読む)

(もっと読む)

サブμ技術に適したデジタル位相同期回路

本発明は、デジタル制御発振器(4)と、位相検出器(11、12、13)と、デジタルループフィルタ(14)とを含む、デジタル位相同期回路に関するものである。上記デジタル制御発振器(4)は、出力周波数を生成するためのものである。上記の位相検出器(11、12、13)は、基準周波数と発振器(4)の出力周波数との位相差を検出するためのものであり、デルタシグマ周波数決定器(11)を含んでいる。上記デジタルループフィルタは、位相検出器の下流に接続されており、デジタル制御発振器(4)を駆動するためのものである。  (もっと読む)

(もっと読む)

電圧制御デジタルアナログ発振器およびこれを用いた周波数シンセサイザ

本発明は、発振器および周波数シンセサイザに関する。特に、電圧制御デジタルアナログ発振器およびこれを用いた周波数シンセサイザに関する。

本発明は、アナログ入力端に入力される電圧およびデジタル入力端に入力されるデジタル値によって出力信号の周波数が決定される発振器と、間欠的に前記アナログ入力端に入力される電圧を第1の閾値電圧および第2の閾値電圧と大小を比較し、その結果に応じて前記デジタル入力端に入力されるデジタル値を変化させるデジタル同調器と、を備える電圧制御デジタルアナログ発振器を提供する。また、これを用いた周波数シンセサイザを提供する。本発明に係る発振器および周波数シンセサイザは、雑音が少ないながらも、広帯域の周波数出力を得ることができる長所がある。

(もっと読む)

(もっと読む)

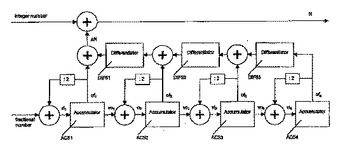

PLL回路のΣΔ変調器

PLL回路の比較分周器の分周比を変調する変調信号を生成するΣΔ変調器。複数の直列接続された積分器(9a〜9c)は、入力信号Fを積算するとともに、積算値が所定値を超えたときオーバーフロー信号OF1〜OF3を出力する。微分器(10a〜10e)は各積分器(9a〜9c)のオーバーフロー信号OF1〜OF3を転送する。加算器(11)は微分器から出力される出力信号(a〜f)に所定の係数を乗算し、その乗算値を加算する。終段の積分器(9c)と、その前段の積分器(9b)との間には、各積分器のクロック信号(fp)の分周信号に同期して積算値を転送する制御回路(12)が接続されている。制御回路(12)を設けることにより、次数を減少させることなく、変調信号の変調幅が減少される。 (もっと読む)

位相スイッチングデュアルモジュラスプリスケーラ

デュアルモジュラス分周器を有する位相スイッチングデュアルモジュラスプリスケーラがもたらされる。前記分周器は第一及び第二の2分周回路(A;B)を有しており、前記第二の2分周回路(B)は、前記第一の2分周回路(A)の出力部に結合され、少なくとも前記第二の2分周回路(B)は各々90度で分離される四つの位相出力を有している。位相選択ユニット (PSU)が、第二の2分周回路(B)の四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の一つを選択するためにもたらされる。更に、位相制御ユニットが、制御信号(C0, NC0; C1, NC1; C2, NC2)を位相選択ユニットに供給するためにもたらされ、位相選択ユニットPSUは、制御信号(C0, NC0; C1, NC1; C2, NC2)による四つの位相出力(Ip, In, Qp, Qn; INi, INni, INq, INnq)の選択を実行する。直接論理に基づく位相制御ユニット(PSU)の実現により、より高い速度が可能になり、チップ上の面積が節減される。  (もっと読む)

(もっと読む)

セル配列を用いた可変インピーダンス回路

電圧制御回路(100)において、電圧制御発振器(110)(VCO)の周波数を制御する可変コンデンサを駆動するために、回路要素の配列(500)が用いられる。配列(500)は、複数のセル(600)、少なくとも1つの出力、複数の粗設定入力(383-388)及び複数の精細設定入力(380-382)を有する。両方の種類の入力は、前記セルの選択可能な組合せを有効にするようにされる。VCO(110)は、複数の周波数帯域にわたる範囲の複数のビットアドレス処理可能な参照周波数で動作する。アドレス制御回路(130)は、前記粗設定入力(383-388)を制御することによって、前記複数の周波数帯域のうちの1つを確定するとともに、また前記精細設定入力を制御することによって、前記周波数帯域のうちの1つを確定する。1つの実施例において、前記アドレス制御回路は、VCO回路(100)のための周波数帯域を設定するのに用いられ、アナログ信号は、前記帯域内の所望な周波数に同調するのに用いられる。  (もっと読む)

(もっと読む)

シグマデルタ変調器を有する可変周波数シンセサイザ

シグマデルタ変調器を有する可変周波数シンセサイザが提供される。そのようなシンセサイザは瞬時的な周波数が変化しても正確な平均周波数を与える。シグマデルタ変調器はカスケード接続された複数のアキュムレータ段を有する。シグマデルタ変調器の一部をなすアキュムレータ(51,52,53,54)の少なくとも1つの入力値は、ある因子の乗算されたオーバーフロー信号(of1,of2,of3,of4)に等しい第2成分を有する。このフィードバックは瞬時的な周波数の最大変動を減らす。位相検出器、チャージポンプ及びVCOの非線形性に起因して生じる位相ジッタはそれ故に減少する。

(もっと読む)

(もっと読む)

タイムベース用のレイアウト

【課題】シリコン共振器におけるように必ずしも温度安定性を必要としない周波数を有し、しかも周囲の熱的条件に係わらずに正確で低コストのタイムベースを得るために使用されることのできる共振器に基づいたレイアウトを提供すること

【解決手段】二つの発振器を含むタイムベースであって、その一つは、他方よりも低い周波数を有し、後者は断続的にスタンバイモードにセットされ、二つの発振器間の周波数差により第1安定時間基準(REF)、最も低い周波数を有する発振器の周波数を分周することにより得られる第2永久的時間基準(RTC)、及び、第1安定時間基準(REF)により決定される時間間隔の間に第1発振器(OSC1)により計数されるパルスに依存する除算因子を発生する。

(もっと読む)

PLL回路

【課題】 従来よりも回路規模の小さい簡単な回路構成で、VCOのゲインを高くせずに広い出力周波数帯域を有することによって外来ノイズの影響を受けにくいPLL回路を得る。

【解決手段】 所望の出力周波数Foの信号を第1VCO14から出力する主PLL回路部2と、該主PLL回路部2の第1VCO14の発振周波数を制御する第1制御電圧VCOIN1及び第2制御電圧VCOIN2の内、第2制御電圧VCOIN2を出力周波数Foに応じて自動調整する副PLL回路部3といった2つのPLL回路を備えると共に、副PLL回路部3の発振周波数を設定する第2プログラマブルカウンタ21の分周比を、第1プログラマブルカウンタ11に設定された分周比に応じて設定するようにした。

(もっと読む)

261 - 277 / 277

[ Back to top ]