Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

281 - 300 / 351

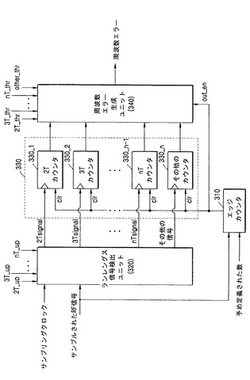

位相同期ループ回路での周波数検出器及び周波数エラーの検出方法

【課題】 位相同期ループ回路において周波数エラーを高速で検出できる周波数検出器及び周波数エラーの検出方法を提供する。

【解決手段】 予測されたランレングス信号の予測分布度に基づいて、周波数検出周期の間にサンプルされたRF信号からランレングス信号を検出するランレングス信号検出ユニットと、周波数検出周期の間に、検出されたランレングス信号をカウントする少なくとも一つのカウンタを備えたカウンタユニットと、サンプルされたRF信号のパッシングエッジをカウントして、周波数検出周期を制御するエッジカウンタと、カウンタユニットに含まれたカウンタによりカウントされた値及び所定の基準値を利用して、周波数検出周期の間の周波数エラーを生成する周波数エラー生成ユニットとを備える。

(もっと読む)

PLL(Phase−LockedLoop)リーク補償のためのシステムおよび方法

【課題】ゲートキャパシタに起因するゲートリーク電流を含み得る電流リークを補償するためのPLLシステムおよび方法。

【解決手段】電圧制御発信器(VCO)の入力ノードに補償電流を供給して電流リークを実質的に補償し、ひいてはPLLジッタを減ずる。PLL回路は、カウンタから入力を受け取り、次いでカウンタ値比例の補償電流を供給する補償チャージポンプを含む。カウンタ値は、位相周波数検出器からのアップおよびダウン入力に従ってインクリメントおよびデクリメントする。カウンタ値はPLL回路がロックされた際に固定される。PLL回路は他のチャージポンプの補助を用いてまたは用いずに補償チャージポンプによって駆動されてロックする。PLLがロックされている間、補償チャージポンプは、固定された、カウンタ値比例の補償電流を供給し得る。

(もっと読む)

周波数シンセサイザおよび無線通信システム

【課題】低消費電力の周波数シンセサイザおよび無線通信システムを提供すること。

【解決手段】制御回路を設けて、チャージポンプが作動する可能性のある時間をFref信号a、Load信号b、ロック検出信号c、基準信号dの中から所望の信号を用いて判断し、その時間のみチャージポンプに定電流もしくは定電圧を供給する電源回路を作動させ、それ以外の時間では電源回路を停止させるよう構成し、また、ロック後に外的および内的要因で電圧制御発振器の発振周波数が変動し、電源回路が停止している時間中にチャージポンプを作動させる信号が入力された場合、電源回路をある一定の時間だけ連続的に作動させるよう構成する。

(もっと読む)

クロック生成回路のテスト回路

【課題】 正確に変調周期分のサンプリングが可能で測定期間を短くすることができ、中心周波数を正確にテストすることでSSCGの変調機能の一つであるダウンスプレッドコントロールの機能テストを正確に行うことができるクロック生成回路のテスト回路を得る。

【解決手段】 コンパレータ21で変調波生成回路16からのアナログ変調波信号Smをデジタル信号Sdに変換して出力し、該デジタル信号Sdに応じて、カウンタ22でクロック生成回路2から出力されたクロック信号Soの周期のカウントを行い、該カウント値とあらかじめ規格値メモリ24に設定されたクロック信号Soの中心周波数の規格値とを比較回路25で比較するようにした。

(もっと読む)

位相同期ループ回路のロック検出のためのシステム及び方法

【課題】位相同期ループ回路のロックを検出するためのシステム及び方法。特に、PLLロック検出された出力をアサートする前のユーザー定義の期間に対するPLLの安定性を検出するために構成されたロック検出器。

【解決手段】安定性は、PLL回路に挿入され位相−周波数検出器とチャージポンプとの間に配置されたカウンタにより示されることができる。カウンタ値は位相−周波数検出器により作動されるので、PLLロックはカウンタ値の安定性により示される。デジタルカウンタ値は、デジタルチャージポンプとロック検出回路に同時に供給されることができる。ロック検出器は、いつカウンタ値間の差がユーザー定義の許容値未満になるかを判定するためにレジスタと差検出器を含む。ロック検出器は、カウンタ値がカウンタ値の変動周波数と同じ周波数でサンプリングされる場合に生じる可能性があるロックの誤表示を避けるために、可変タイマーを含むことができる。

(もっと読む)

発振器およびこれを用いたPLL回路

【課題】 インダクタを制御信号により連続的に変化可能とすることにより、発振器およびPLL回路の機能および性能を向上させる。

【解決手段】 インダクタンスが変化する可変インダクタ部と、可変インダクタ部に接続された可変容量素子と、可変インダクタ部のインダクタンスと可変容量素子の容量とで決まる発振周波数により発振する出力部と、発振周波数を変調する周波数制御信号を生成する制御信号生成手段とを含む。可変インダクタ部は、第1インダクタと、第1インダクタに流れる電流を表す電気信号を検出し、電気信号に基づいて電流信号を生成する電流信号生成手段と、電流信号を受ける第2インダクタとを含み、第1インダクタと第2インダクタを所定の磁気的結合位置に配置し、第1インダクタのインダクタンスを所望の値にする。

(もっと読む)

原子発振器

【課題】原子発振器200の出力周波数702の位相雑音を改善する際に、原子発振器自体の超小型化を維持すると共に、電源投入後又は原子発振器自身の異常で出力周波数702が不安定状態である場合においても安定した出力周波数800を出力し、位相雑音特性の優れた原子発振器を実現する。

【解決手段】原子発振器200の出力側に恒温槽タイプ電圧制御発振器及び比較器を備えた位相雑音改善回路100を接続し、比較器が、原子発振器の出力周波数702と恒温槽タイプ電圧制御発振器の出力周波数(クロック信号)800とを比較し、この比較結果に基づき、該恒温槽タイプ電圧制御発振器の出力周波数を原子発振器200の出力周波数702に追従するように該恒温槽タイプ電圧制御発振器を制御し、原子発振器200の出力周波数702が与えられないとき該恒温槽タイプ電圧制御発振器が自走周波数を出力するように制御する。

(もっと読む)

ループ周波数関数としてのディレイもしくはフェーズロックドループをコントロールするための装置および方法

ディレイ ロックド ループ(Delay Locked Loop:DLL)もしくはフェーズ ロックド ループ(Phase Locked Loop:PLL)用の方法と回路が開示されている。かかる方法と回路は、処理、電圧、または温度の変化に関係なく、高周波数におけるループの安定性を改善し、また最大のトラッキング帯域幅を実現できる。技術の中心となるものは、クロック信号(1/tCK)である高い周波数においてではなくループ自身の固有の帯域幅(1/tLoop)に近い低い周波数においてループを効率的に動作させることである。そのようにするために、一実施例において、ループ遅延、すなわちtLoop,が、ループの動作前に計測されるか、あるいは予測される。続いて、位相検出器が、ループ周波数1/tLoopに近い周波数でイネーブルされる。簡単に言えば、位相検出器は、無用な遅延時間中は実働しないようにされており、その結果、ループが過剰反応したり、不安定になることを防ぐことができる。 (もっと読む)

周波数シンセサイザ

【課題】第1の周波数の信号を生成する第1の信号生成回路と、第1の周波数と異なる周波数である第2の周波数の信号を生成する第2の信号生成回路と、の相互干渉を抑制した周波数シンセサイザを実現する。

【解決手段】第1の周波数の信号を生成する第1の信号生成回路と、第1の周波数と異なる周波数である第2の周波数の信号を生成する第2の信号生成回路と、を備え、第1の周波数の信号と第2の周波数の信号のうち、いずれかを出力する周波数シンセサイザであって、第1の信号生成回路は、第1の周波数のN倍(Nは、正の整数)の周波数でPLL発振し、これを1/N倍で分周することにより、第1の周波数の信号を生成し、第2の信号生成回路は、第2の周波数のM倍(Mは、Nよりも大きく、Nで割った値が自然数にならない整数)の周波数でPLL発振し、これを1/M倍で分周することにより、第2の周波数の信号を生成する。

(もっと読む)

位相同期ループ回路、オフセットPLL送信機、通信用高周波集積回路及び無線通信システム

【課題】ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】ループ利得検出にあたっては、まず、位相比較器101の第2の入力(IN−2)への入力信号の周波数を変化させ、その変化に対する応答を電圧制御型発信器102の出力で検出する。検出手段としては、電圧制御型発信器102の出力にカウンタ103を接続し、そのカウンタ103の出力に積分器104を接続することで行う。この検出結果をチャージポンプ105の電流値にフィードバックすることで、位相同期ループ特性を最適化する。

(もっと読む)

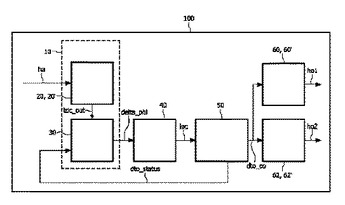

位相ロックループ回路装置及びこれを利用したクロック信号発生方法

回路装置(100)、特にサブクロックまたはサブピクセルの正確な位相測定及び位相発生用の位相ロックループ、並びにこれに対応する方法を、クロック乗算器位相ロックループを時間−ディジタル変換器の後方に設けず、アナログ遅延線も信号除算器ユニットも、ディジタルランプ発振器または離散時間発振器とディジタル−時間変換器との間に設けず、ディジタル環境におけるノイズ及び接地バウンスの影響を受け易いアナログ回路がより少ない方法でさらに発展させるために、少なくとも1つの位相測定ユニット(10);少なくとも1つの位相検出器ユニット(30)の少なくとも1つの出力信号(delta_phi)を供給される少なくとも1つのループフィルタユニット(40, 40’);ループフィルタユニット(40, 40’)少なくとも1つの出力信号、特に少なくとも1つの増分(inc)を供給される少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)を設け、ディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つのレジスタユニット(54, 54’)の状態信号(dto_status)は位相検出器ユニット(30)に入力信号として供給され、さらに、少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つの出力信号(dto_co)を供給されて少なくとも1つの出力信号(ho1, ho2)発生する少なくとも1つのディジタル−時間変換器ユニット(60, 62, 60’, 62’)を設けることを提案する。  (もっと読む)

(もっと読む)

クロック生成回路

【課題】

回路規模と消費電力とを増大させることなく、規格などに定められた変動周期および周波数の変動範囲を満足するように、出力クロック信号の周波数拡散を実現できるようにする。

【解決手段】

電圧制御発振器110の発振周波数を制御する発振周波数制御信号をリークさせる電流経路160が設けられ、電圧制御発振器110のサイクル数をカウントするカウンタ170のカウント結果に応じた所定の周期で、位相検出器120の出力のオン/オフの状態が切り替えられる。位相検出器120の出力がオフの時には、電流経路160で発振周波数制御信号がリークさせられることによって電圧制御発振器110の発振周波数が低下する。次に位相検出器120の出力がオンになると、フィードバック制御により低下した電圧制御発振器110の発振周波数が所定の周波数まで上昇する。

(もっと読む)

検出回路及び半導体装置

【課題】

簡易な回路構成により、外部クロックの停止を効率よく検出できる検出回路及び半導体装置を提供すること。

【解決手段】

本発明にかかる半導体装置は、発振クロックを逓倍したPLL出力クロックを生成するPLL回路11と、PLL出力クロックに基づいて動作する内部回路13と、発振クロックとPLL出力クロックに基づいて発振クロックの停止を検出し、検出した結果を内部回路13へ出力する発振停止検出回路12と、を有するものである。

(もっと読む)

フリーラン周波数の調整方法

【課題】 ステレオ複合信号から左右の音声信号を分離するステレオ分離度を常に一定にするフリーラン周波数の調整方法を提供する。

【解決手段】 上記課題を解決するために、本発明に係るフリーラン周波数の調整方法では、同期可能な範囲の調整点のフリーラン周波数を計測し(ステップS202)、計測結果から2つの最終調整点の候補を決定し(ステップS203)、各最終調整点の候補におけるフリーラン周波数を連続的に複数回計測して得た平均値(ステップS206)のうち中央値に近い調整点を最終調整点とする(ステップS207)。そして、この最終調整点の位相とパイロット信号の位相とを同期する(ステップS208)。

(もっと読む)

クロック切り替え装置及びクロック切り替え方法

【課題】装置の処理を中断することなく自動的にバックアップ用のクロック分配系に切り替えることのできる、クロック切り替え装置及びクロック切り替え方法を提供する。

【解決手段】第1のクロック分配系CIN0のあるクロックパルスT0とその1周期前のクロックパルスT0’の位相を合わせる第1の検出用位相調整手段1と、クロックパルスT0とT0’の論理レベル(HIGH/LOW)が一致しているかどうかチェックし、不一致の場合ALM0をHIGHにする第1の異常検出手段2と、第2のクロック分配系CIN1のあるクロックパルスT1とその1周期前のクロックパルスT1’の位相を合わせる第2の検出用位相調整手段3と、切替信号生成手段6と、切替手段7を有する。

(もっと読む)

位相周波数検出回路およびPLL

【課題】 媒体の傷等の影響を受けず、変調マークに左右されずに安定に高速にPLLを引き込むことが可能な位相周波数検出回路およびPLLを提供することにある。

【解決手段】 再生信号に基づいて再生クロック信号を生成する回路において、前記再生クロック信号を生成する電圧制御発振器と、前記再生クロックから前記所定周期の信号を発生する第1の周期発生器と前記第1の周期発生器とは位相が異なり、前記再生クロックから前記所定周期の信号を発生する第2の周期発生器と、前記再生信号と前記第1の周期発生器の出力とを乗算する第1の乗算器と、前記再生信号と前記第2の周期発生器の出力とを乗算する第2の乗算器と、前記第1の乗算器の出力と第2の乗算器の出力に応じて前記電圧制御発振器の制御電圧を制御するPLL。

(もっと読む)

FMステレオ送信用回路

【課題】FMステレオ送信機において、水晶発振子を1つにし、コストダウンを図るとともに、PLLの基準発振器の高調波によりFM放送帯に妨害を与えないようにする。

【解決手段】 Lチャネル信号、Rチャネル信号及びパイロット信号からステレオコンポジット信号に変換する手段12、15を備える。周波数変調手段16、C4〜C6、R1〜R3、L1、D1、D2で搬送波が前記ステレオコンポジット信号により周波数変調された変調波を送信する。分周することにより38kHzが得られるような発振周波数の発振器2を設け、周波数変調手段16、C4〜C6、R1〜R3、L1、D1、D2はPLL回路3〜8を用いて前記発振周波数によって前記搬送波の周波数が制御されるようにする。一方、前記発振周波数を分周することにより前記パイロット信号とする。

(もっと読む)

FMステレオ送信用回路

【課題】FMステレオ送信機において、水晶発振子を1つにし、コストダウンを図るとともに、PLLの基準発振器の高調波によりFM放送帯に妨害を与えないようにする。

【解決手段】 Lチャネル信号、Rチャネル信号及びパイロット信号からステレオコンポジット信号に変換する手段12、15を備える。周波数変調手段16、C4〜C6、R1〜R3、L1、D1、D2で搬送波が前記ステレオコンポジット信号により周波数変調された変調波を送信する。分周することにより38kHzが得られるような発振周波数の発振器2を設け、周波数変調手段16、C4〜C6、R1〜R3、L1、D1、D2はPLL回路3〜8を用いて前記発振周波数によって前記搬送波の周波数が制御されるようにする。一方、前記発振周波数を分周することにより前記パイロット信号とする。

(もっと読む)

自動車音響システム

【課題】FMステレオ送信機において、水晶発振子を1つにし、コストダウンを図るとともに、PLLの基準発振器の高調波によりFM放送帯に妨害を与えないようにする。

【解決手段】 Lチャネル信号、Rチャネル信号及びパイロット信号からステレオコンポジット信号に変換する手段12、15を備える。周波数変調手段16、C4〜C6、R1〜R3、L1、D1、D2で搬送波が前記ステレオコンポジット信号により周波数変調された変調波を送信する。分周することにより38kHzが得られるような発振周波数の発振器2を設け、周波数変調手段16、C4〜C6、R1〜R3、L1、D1、D2はPLL回路3〜8を用いて前記発振周波数によって前記搬送波の周波数が制御されるようにする。一方、前記発振周波数を分周することにより前記パイロット信号とする。

(もっと読む)

FMステレオ送信用回路

【課題】FMステレオ送信機において、水晶発振子を1つにし、コストダウンを図るとともに、PLLの基準発振器の高調波によりFM放送帯に妨害を与えないようにする。

【解決手段】 Lチャネル信号、Rチャネル信号及びパイロット信号からステレオコンポジット信号に変換する手段12、15を備える。周波数変調手段16、C4〜C6、R1〜R3、L1、D1、D2で搬送波が前記ステレオコンポジット信号により周波数変調された変調波を送信する。分周することにより38kHzが得られるような発振周波数の発振器2を設け、周波数変調手段16、C4〜C6、R1〜R3、L1、D1、D2はPLL回路3〜8を用いて前記発振周波数によって前記搬送波の周波数が制御されるようにする。一方、前記発振周波数を分周することにより前記パイロット信号とする。

(もっと読む)

281 - 300 / 351

[ Back to top ]