Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

261 - 280 / 351

クロック信号発生装置、クロック信号発生方法及びプログラム

【課題】位相の変化に迅速に追従しつつ、クロックスリップが起こり難い(安定した)クロック信号を再生するクロック信号発生装置等を提供することである。

【解決手段】位相比較器1Aは、データ信号と、デジタルVCO1Cの再生クロック信号を基準としたデータ信号の位相の遅れ及び進みを検出する。ランダムウォークフィルタ1Bは、この遅れ進みの回数差を計測して、回数差の絶対値が所定値に達すると、差を打ち消す方向に再生クロック信号の位相を変化させるようデジタルVCO1Cを制御し、計測結果をリセットして計測を再開する。再生位相比較器3は、デジタルVCO1C及び2Cの各再生クロック信号の位相差を検出してランダムウォークフィルタ1Bに通知する。ランダムウォークフィルタ1Bは、通知された位相差が所定量に達している間は、計測結果のリセットやデジタルVCO1Cの再生クロック信号の位相の変更を行わない。

(もっと読む)

PLL制御回路

【課題】省電力モード等において周波数が大きく変動するリファレンスクロックに応答し、PLLクロックを出力するPLL制御回路では、省電力モード時等においてリファレンスクロックの変動に追随できず、誤動作が生じる場合があった。

【解決手段】リファレンスクロックに応答し、PLLクロックを出力するPLL制御回路において、リファレンスクロックの変動の際にも、PLLクロックの周波数が実質的に一定になるような周波数調整を行う周波数調整回路を備えている。周波数調整回路はPLLクロックの周波数を決定するカウンタの設定値をリファレンスクロック周波数の変動に応じて変化させる。

(もっと読む)

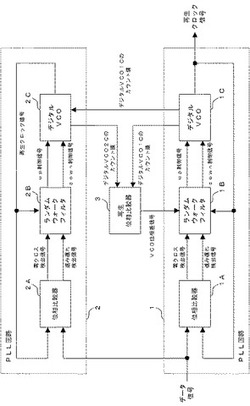

無線通信装置及び無線エントランスシステム

【課題】現用系装置と待機系装置との間での位相同期を効率よく行う無線通信装置及び無線エントランスシステムを提供する。

【解決手段】PLL回路14aは、インターフェース部100からの第1タイミング信号と読出カウンタ20aからの第2タイミング信号とが同相となるように、第2クロックを読出カウンタ20a、送信用無線フレーム処理部122a及びフレーム変調部124aに出力する。PLL回路14bは、前記第1タイミング信号と読出カウンタ20bからの第3タイミング信号とが同相となるように、第3クロックを読出カウンタ20b、送信用無線フレーム処理部122b及びフレーム変調部124bに出力する。

(もっと読む)

デューティ検知回路、これらを備えたDLL回路及び半導体装置

【課題】 従来のデューティ検知回路においては、デューティずれを精確に電位差に反映できないという問題がある。またクロックの分周及び逓倍が行われる2分周DLL回路のデューティ検知回路においては、連続サイクルでのデューティの検知が出来ないという問題がある。

【解決手段】 クロックの一方のレベル検知を半サイクル遅延させ、デューティ検知を2サイクルに1回とする。遅延期間に共通接点の電位を初期設定値とすることで、精確なデューティが検知できる。2分周方式のDLL回路には偶数、奇数のサイクル別にデューティ検知回路を備え、偶数、奇数のサイクルに対しそれぞれのデューティを検知する。これらの構成とすることでクロックに精確にタイミング調整できるDLL回路及び半導体装置が得られる。

(もっと読む)

遅延ロックループ回路、タイミング発生器、半導体試験装置、半導体集積回路及び遅延量校正方法

【課題】 遅延量の測定に代わる手法で、カウンタの初期設定値を決めて、遅延回路の校正にかかる時間を短縮可能とする。

【解決手段】 複数のカウンタ設定値の中から一つのカウンタ設定値がロードされ、遅延ロックループ回路10−1がロックモードに切り替えられ、サイクルスリップ検出回路20−1の順序回路22がリセットされ、その後、順序回路22から出力されるサイクルスリップ検出信号が読み込まれると、このサイクルスリップ検出信号にもとづき、遅延回路11の出力信号がサイクルスリップを起こしているか否かが判定され、起こしているときはカウンタ設定値が切り替えられ、一方起こしていないときは、ロックされて完了する。

(もっと読む)

ディジタル情報記録再生装置およびディジタルフェーズロックドループ回路

【課題】ユーザ領域で用いるトラッキング用位相比較器では、PLLの引込み範囲が狭く、所定長のRUN−IN領域だけでは、PLLの引込みが完了できない課題があった。

【解決手段】ゼロクロス検出手段と、ゼロクロス検出手段の通過タイミングに合わせて動作を開始しカウント値を出力する周期カウンタと、前記ゼロクロス検出手段から出力された通過方向情報と前記カウント値から、再生信号がゼロクロスするタイミングを予測し、初期位相誤差を出力するアクイジション用位相誤差検出器を備える。ゼロクロス検出手段は、プリアンブル領域に含まれる特定パターンの立上り又は立下りエッジのゼロクロス点を検出し、検出されたゼロクロス点から所定周期の周期カウンタを動作させ、プリアンブル領域の特定パターンから予測されるゼロクロス点を予測し、アクイジション用位相誤差を出力する。

(もっと読む)

DLL装置及びDLLクロック生成方法

【課題】長時間パワーダウンモード状態にとどまる場合にロックフェイル(fail)が発生するのを防止すること。

【解決手段】外部クロックを受信して、バッファリングして、内部クロックを生成するクロックバッファと、クロックイネーブル信号CKEに応答して、ノーマルモードなのか、パワーダウンモードなのか、に対する情報を有する制御信号を生成するパワーダウンモード制御部と、前記の制御信号に応答して、内部クロックに基づいた、ソースクロックを提供するソースクロック生成部と前記のソースクロックに基づいてDLLの位相更新を行い、DLLクロックを提供する位相更新部を備える遅延固定ループを提供する。長時間にパワーダウンモードにとどまる場合にも、パワーダウンモード区間の一部の区間で、DLL位相更新を行なうことによって、ロックフェイル(fail)が発生することを防止できる。

(もっと読む)

遅延固定ループのクロックドライバー制御装置

【課題】パワーダウンモードや、セルフリフレッシュモードだけでなく、ノーマルモード動作においても、実際にクロックが用いられる必要区間以外の区間に対して、意味無くDLLクロックがトグルリングされることを防止して、DRAMの動作電流を低減させるためのDLL装置を提供する。

【解決手段】DLLドライバー制御装置は、DLLクロックをドライビングするDLLドライバーと、アクティブモードに関する情報を有する信号に応答して、前記DLLドライバーの駆動を制御するための制御信号を生成するDLLドライバー制御部とを備える。

(もっと読む)

PLL同期回路

【課題】 参照入力信号が大きく変化し又は出力信号が参照入力信号に対して誤差を生じた場合に迅速且つ適正に同期した信号を生成できるPLL同期回路を提供する。

【解決手段】 電圧制御発振器3からの出力信号を位相比較器1に内部変化信号として帰還させ、この位相比較器1が参照入力信号S1の周期における帰還制御される制御周期の直前周期の波長を所定値で分割部により分割し、この分割された分割波長のカウント値と制御周期における現在カウント値とをカウント位相比較部16で比較し、この比較結果に基づき前記参照入力信号S1の周波数変化を位相検出部で検出するようにしているので、選局の変更等で参照入力信号が大きく変化した場合であっても迅速且つ確実に変更後の周波数に同期する発振出力が可能となり、ジッタの発生を極力低減できると共に、周波数ステップの応答性を向上させることができる。

(もっと読む)

クロック位相同期回路

【課題】 回路構成を簡素化するとともに高速な位相同期を行う。

【解決手段】 B/U変換部1は、バイポーラ信号のプラス側波形のRZユニポーラ信号およびマイナス側波形のRZユニポーラ信号を発生し、OR回路2は2列のRZユニポーラ信号を1列のRZユニポーラ信号に変換する。フリップフロップ3は、クロック端子に1列のRZユニポーラ信号を入力し、データ端子に“H”レベルを入力しており、バイポーラ信号の64kHz成分の信号を抽出する。カウンタ5はフリップフロップが抽出した64kHz成分の信号により有効化され、512kHz以上のクロックをカウントする。リセットパルス発生回路6はカウントが所定回数になるとリセットパルスを出力する。

(もっと読む)

半導体集積回路

【課題】 トリミングを行わずに電圧制御発振回路の発振周波数を調整すること。制御回路の面積を抑え、調整誤差の少ない発振回路を内蔵した半導体集積回路を提供すること。

【解決手段】 電圧制御発振回路(VCO)の周波数を調整する可変容量素子を、プロセスや素子のばらつき調整用可変容量素子群と、周波数選択用可変容量素子群との2系統に分離して調整を行い、可変容量素子の切り替えスイッチの数と回路面積の増大を小さくする。調整誤差については、調整期待値との差分を記憶素子で記憶し、その差分値が最小となる容量素子値を求めることにより影響を最小限に押さえることが可能となる。

(もっと読む)

PLL回路

【課題】ジッタ環境や電圧制御発振器の特性の差異に応じて、電圧制御発振器への電圧制御勾配のパラメータ変更を容易に行うことができ、ジッタ環境や電圧制御発振器の特性の差異に柔軟に対応できるPLL回路を提供する。

【解決手段】分周器10は入力クロックCLK_Aを分周する。分周器11は出力クロックCLK_Bを分周する。位相比較部12は分周器10が出力する分周クロックCLK_aと分周器11が出力する分周クロックCLK_bの位相差を位相比較結果として保持する。ソフト処理部13は位相比較結果をソフト処理して制御電圧生成用パルス列CPを出力する。ループフィルタ14は制御電圧生成用パルス列CPを平滑化してなる制御電圧VCを電圧制御発振器15に与え、電圧制御発振器15は制御電圧VCに対応する周波数の出力クロックCLK_Bを出力する。

(もっと読む)

位相制御装置、周波数制御装置、発振装置、位相制御方法及び周波数制御方法

【課題】

DDSなどの発信源の位相をより多彩に制御すること。

【解決手段】

本発明の位相制御装置は、所定の信号を、この信号の位相を示す第1の位相情報に基づいて出力する複数の信号源から出力される信号間の位相を制御する位相制御装置であって、複数の信号源ごとに設けられ、信号源から出力される信号の位相を示す第2の位相情報を格納する複数の位相情報格納手段と、位相情報格納手段によって格納された第2の位相情報に基づいて、複数の信号源のうち少なくとも1つの信号源から出力される信号の位相を変えて前記複数の信号源から出力される信号間の位相差を制御する位相制御手段とを具備する。また、第2の位相情報を第1の位相情報より高分解能となるよう構成することができる。

(もっと読む)

タイミング発生器、試験装置、及びタイミング発生方法

【課題】遅延量を精度よく測定し、遅延量が精度よく制御されたタイミング信号を発生するタイミング発生器、半導体試験装置、及びタイミング発生方法を提供する。

【解決手段】所定の周波数を発生する基準信号発生部と、基準信号を所定の時間遅延させたタイミング信号を出力する可変遅延回路部と、可変遅延回路部の遅延量を測定する遅延量測定部とを備え、遅延量測定部が測定した遅延量に基づいて可変遅延回路部の遅延量を制御するタイミング発生器において、基準信号の周波数を微小周波数範囲で連続的に変調させることにより、遅延量測定部が精度よく可変遅延回路部の遅延量を測定することができる。また、測定した遅延量に基づいて可変遅延回路部の遅延量を制御することにより、精度よく遅延されたタイミング信号を発生することが可能となる。

(もっと読む)

局間補正装置

【課題】電圧制御水晶発振器の使用を回避することにより、コストの削減及び消費電力の低減を図ることができるとともに、視聴者が違和感を感じることなく送信局と受信局との映像・音声信号の同期をとることが可能な、局間補正装置を得る。

【解決手段】比較器6は、カウンタ値K1,K3の差Y3が許容値Mを超えたことを検出すると、補正実行命令S4,S5を出力する。補正実行命令S4は補正部2に入力され、補正部2は、デコード部1から出力されたデータD2に対してリニアスケーリング補正を行って、補正後のデータD3を出力する。また、補正実行命令S5は自走PCRカウンタ5に入力され、自走PCRカウンタ5は、補正部2によるリニアスケーリング補正の補正量に応じて、カウンタ値K3を補正する。

(もっと読む)

ジッタを減少させた半導体装置、分散スペクトルクロック発生器、及び信号出力方法

【課題】ジッタを減少させた半導体装置、分散スペクトルクロック発生器、及び信号出力方法を提供する。

【解決手段】出力信号を受信し、出力信号の周波数を異なる分周比で分周させた第1フィードバック信号FDB1及び第2フィードバック信号FDB2を生成する分周部430、及び第2フィードバック信号FDB2に応答して基準信号と所定の位相差を有する出力信号を生成する位相オフセット部を備え、第2フィードバック信号FDB2は、第1フィードバック信号FDB1より高い周波数を有する半導体装置であり、直列に連結される複数個の分周器及び複数個の分周器の出力のうち少なくとも一つの出力に応答して、複数個の出力信号のうち一つを選択して出力する選択器420を備え、複数個の出力信号のそれぞれは、基準信号に比べて互いに異なる位相差を有する分散スペクトルクロック発生器400である。

(もっと読む)

広範囲かつダイナミックに再構成可能なクロックデータ回復アーキテクチャ

【課題】広範囲のデータレートに渡って動作可能なCDRアーキテクチャを提供する。

【解決手段】広範囲およびダイナミックにリプログラミング可能なCDRアークテクチャは、広範囲の動作周波数でシリアル入力データから埋め込まれたクロック信号を回復する。広範囲のデータレートをサポートするために、CDRアーキテクチャは、複数の動作パラメータを含む。これらのパラメータは、様々な先行/後行の分割器設定、チャージポンプ電流、ループフィルタおよび帯域幅選択、および、VCOギアを含む。パラメータは、回路またはPLDのパワーダウンなしに、ダイナミックにリプログラミングされ得る。これは、CDR回路が、様々な規格とプロトコルとの間を迅速に切り替えることを可能にする。

(もっと読む)

スペクトル拡散クロック発生器を自動的に補正する方法と装置

【課題】位相ロックループ回路内の受動素子値およびシステム利得およびチャージポンプ電流の変動を自動的に補正するスペクトル拡散クロック発生器回路を提供する。

【解決手段】位相周波数検出器122のUPおよびDOWN信号124、126のパルス幅を特定の間隔で監視し、標準パルス幅持続時間と比較して、これらのUPおよびDOWN信号124、126の偏差誤差を判別する。パルス幅持続時間の実際の値で誤差を測定した後、誤差信号の大きさと方向に応じて位相ロックループ回路100を調整する。位相ロックループ利得パラメータ、特に電圧制御発振器134の利得およびチャージポンプ電流に変化があると、位相周波数検出器122の出力に著しい影響が出て、スペクトル拡散プロファイルに沿って周波数が変化するときにUPおよびDOWN信号124、126の幅が変動する。

(もっと読む)

逓倍型PLL回路のノイズ補償システム

【課題】車両走行時のように、周囲の建造物等による障害物の影響により、急激な電界変動や車両機器特有のノイズ等による瞬間的な同期信号の乱れに対して、PLL回路が誤動作を生じる場合がある。

【解決手段】外部から入力された同期信号のノイズ量に応じて、1水平期間に受信装置内部で生成された仮想同期信号の挿入数を決定する回路と、仮想同期信号を外部から入力された同期信号に重畳する回路と、仮想同期信号を受信装置内部の同期信号に重畳する回路とを備え、仮想同期信号を挿入した外部同期信号と内部同期信号とを比較することにより、安定したPLL動作を可能とするノイズ補償システム。

(もっと読む)

クロックデータリカバリ回路

【課題】 データ信号とクロックとの周波数に差がある場合でも、2相の内部クロックを必要とせずに、データ信号とクロックとの同期が可能なCDR回路を提供すること。

【解決手段】 PD14は、DATAとVDL11からのVDL出力との位相差を検出する。CODE Operator13は、出力クロックの1周期と同じ遅延に相当する制御コードの値を検出する。そして、PD14による検出結果に応じて制御コードを変更しながら出力クロックをデータ信号に同期させる際、VDL11の遅延量がクロックの1周期分を超えるときに、制御コードに対して出力クロックの1周期と同じ遅延に相当する制御コードを一度に加算または減算する。したがって、データ信号とクロックとの周波数に差がある場合でも、同一のクロック位相を与えながらデータ信号とクロックとの同期をとることが可能となる。

(もっと読む)

261 - 280 / 351

[ Back to top ]