Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

181 - 200 / 351

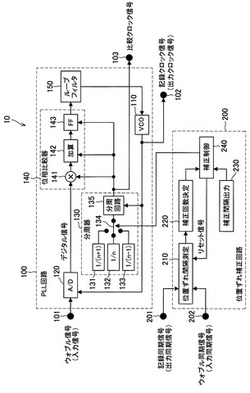

クロック生成回路、記録装置及びクロック生成方法

【課題】入力信号の欠落により発生する出力クロック信号のずれを適切に補正しつつ、入力信号に同期した出力クロック信号を生成することができるクロック生成回路を提供する。

【解決手段】所定の周波数を有する入力信号を所定の逓倍比で逓倍して出力クロック信号を生成するクロック生成回路10を提供する。このクロック生成回路10は、入力信号を逓倍して出力クロック信号を生成するPLL回路100と、PLL回路100の逓倍比を変更する補正回路200と、を備え、補正回路200は、入力信号に同期した入力同期信号と出力クロック信号に同期した出力同期信号との時間差が減少するにように、入力信号の1周期より長い補正周期毎の補正区間においてのみPLL回路100の逓倍比を所定の逓倍比から当該所定の逓倍比を増加又は減少した逓倍比に変更し、PLL回路100は、補正区間において、変更された逓倍比で入力信号を逓倍する。

(もっと読む)

従属同期クロック信号生成装置

【課題】従属同期クロック信号生成装置に関し、従属同期用クロック信号の系切替え時に瞬断なくクロック信号を供給し、擾乱の無い装置供給用クロック信号を供給する。

【解決手段】外部から2系統の従属同期クロック信号を入力し、該従属同期クロック信号の1周期分の信号の開始部分を検出してハイレベル信号を出力し、該従属同期クロック信号の1周期未満のタイミングでローレベル信号を出力する2系統のクロック信号生成部(#0)1−1,(#1)1−2と、該クロック信号生成部から出力される信号の論理和信号をクロック信号としてPLO部6−7出力する論理和信号出力部1−3を備える。クロック信号生成部は、内部自走クロック源1−4のクロックをカウントして従属同期クロック信号の1周期未満のタイミングでローレベル信号をフリップフロップ回路1−12,1−22のリセット端子に入力して強制的にローレベル信号を出力させる。

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

クロック信号出力回路

【課題】逓倍クロック信号の基準クロック信号に対する同期ずれを補正することができるクロック信号出力回路を提供する。

【解決手段】位相誤差補正回路12は、基準クロック信号PREFと逓倍クロック信号POUTとの位相差を検出し、その位相差に応じて、逓倍クロック信号POURの出力位相を基準クロック信号PREFに同期させる補正を、1制御周期の間に複数回実行する。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックに応答して1ビットずつレベル遷移する複数のビットの周波数制御信号を生成する周波数制御信号生成部と、及び前記複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。また、他の発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

周波数同期システム及び周波数同期方法

局部発振器からの局部信号と遠隔発振器からの基準クロック信号の間で周波数を同期させるデジタル周波数ロックループに関連するシステムおよび方法。基準カウンタは、基準クロック信号内のパルスごとにその計数を増分する。基準カウンタ内の値は、設定可能な基準値と比較される。基準カウンタ値と基準値の一致が発生するたびに、ヒット信号が生成され、基準カウンタ値が再初期化される。上記と同時に、局部信号からのパルスごとにフィードバックカウンタが増分される。ヒット信号が生成されると、フィードバックカウンタ内の値が設定可能なフィードバック値と比較(減算による)されて、差の値を生成する。次いで差の値が、局部発振器の周波数を増大または減少させるのに使用するための周波数調整信号に変換される。ヒット信号はまた、フィードバックカウンタを再初期化する。 (もっと読む)

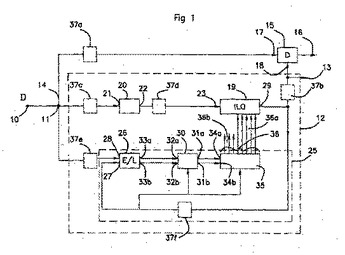

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

電圧制御発振器およびそれを用いたPLL回路

【課題】 電源ノイズの影響を抑制し、ジッタを低減できる電圧制御発振器を提供する。

【解決手段】 入力電圧を該入力電圧に応じた制御電流に変換する電圧電流変換回路1と、該制御電流に基づいて発振信号を出力する電流制御発振回路2とを備えた電圧制御発振器60において、電圧電流変換回路1は、電圧制御発振器60の発振を開始させる動作電流を供給する定電流生成部と、該動作電流により入力電圧に応じた制御電流を生成する制御電流生成部と、起動信号に基づいて該動作電流の供給および遮断を行う電流供給スイッチ17とを有し、電流供給スイッチ17を制御することにより、発振周波数が安定するまでの時間を短縮し、電源ノイズの影響を抑制する。

(もっと読む)

PLL回路

【課題】エクステンダ部の動作遅延時間を短縮して、分周比切り替え動作の誤動作に対するマージン時間を十分に確保し得るプリスケーラを提供する。

【解決手段】プリスケーラ21bは、分周比切り替え信号に基づいて、分周比を切り替えながら入力信号fvcoを分周する分周切り替え部Cと、分周切り替え部の出力信号を所定の分周比で分周するエクステンダ部Eとを備える。分周切り替え部Cは複数段のフリップフロップFF1〜FF3を有し、エクステンダ部Eの少なくとも一部を同期型カウンタで構成するとともに、少なくとも一部を非同期型カウンタで構成する。

(もっと読む)

DLL回路

【課題】DLL回路を備えたLSIの電磁放射強度を低減し、電磁放射ノイズの電子機器への影響を低減する。

【解決手段】DLL回路は、入力信号に基づいて同期基準信号を生成する入力回路101と、同期基準信号を遅延する第1遅延部102と、前記第1遅延部102によって遅延された同期基準信号の同期位置を調整し、同期対象信号を生成するタイミングオフセット回路103と、 前記同期基準信号と前記同期対象信号との位相差を比較する位相比較回路105と、前記位相比較回路105の比較結果に基づいて前記第1遅延部102の出力信号を選択する第1制御回路106と、前記同期基準信号又は前記同期対象信号を遅延する第2遅延部104と、前記位相比較回路105の比較結果が所定の範囲内である場合に、前記第2遅延部104の出力信号を選択する第2制御回路107と、を備え、前記位相比較回路105は、前記同期基準信号と前記同期対象信号のうち前記第2遅延部104によって遅延された信号と他方の信号との位相差を比較する。

(もっと読む)

ジッタ判定回路およびジッタ判定方法

【課題】従来のジッタを測定する回路では、簡単な回路構成で、正確にジッタの変動率を測定することが困難であった。

【解決手段】ジッタ判定回路は、発振回路と、PLL回路の出力クロックが与えられ、測定期間指定信号に基づいて、測定期間信号を出力する測定期間設定回路と、測定期間信号が出力されている間に発振回路の出力するクロック数をカウントするカウンタと、測定期間信号が出力されている間に発振回路の出力するクロック数の基準カウント値を設定する基準カウント値決定回路と、カウンタのカウントした最大カウント値、最小カウント値及び基準カウント値に基づいてPLL回路のジッタの誤差を判定する誤差判定回路とを有する。

(もっと読む)

クロック補正回路と方法並びにシステム

【課題】同期元基準信号のジッタ、ワンダの影響を除去可能とする回路の提供。

【解決手段】到着クロックに同期した同期基準信号を出力する同期元クロック受信部と、同期元クロック監視用の複数のウィンドウを生成するウィンドウ生成部と、ウインドウがアクティブのとき同期基準信号がアクティブの場合、アクティブの出力信号を出力する複数の判定部と、複数の判定部からの出力信号をカウントし同期基準信号が各ウィンドウのタイミングで何回検出されたかをカウントする複数のカウンタとを備えている入力クロック監視部と、予め設定された閾値と複数のカウンタよりそれぞれ出力されたカウント値の比較を行い、比較結果とカウント値を出力する複数の比較部と、複数の比較部から出力された閾値との比較結果を元に入力クロック監視部の判定部の制御を行う閾値判定部を備えたクロック補正判定部と、判定結果収集部と、PLLを備える。

(もっと読む)

位相調整回路および位相調整方法

【課題】 VCOの出力に生じている周波数変動を動的に補正し、これによりロングタームジッタを削減することが可能な位相調整回路の提供。

【解決手段】 周波数比較部12において、基準クロックRIN1の分周クロックREF1の周波数とフィードバッククロックFIN1の分周クロックFB1の周波数を測定および比較し、位相調整部13において、周波数比較部12の比較結果により、FB1の周波数がREF1より高ければカウンタ13−1をカウントアップして可変遅延回路13−2の遅延量を増やし、FB1の周波数がREF1より低ければカウンタ13−1をカウントダウンして可変遅延回路13−2の遅延量を減らす。

(もっと読む)

クロック信号生成回路、及び半導体装置

【課題】製造プロセスにおけるばらつきが原因による同期期間や同期期間終了後の自走期間において、周波数が変動することがなく、安定した動作を実現し、また安価な半導体装置を提供する。

【解決手段】第1の基準クロック信号を生成する基準クロック信号生成回路と、第1基準クロックの信号及び同期信号を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第1のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第2のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号を分周し、第2の基準クロック信号を生成する第1の分周回路と、第2の基準クロック信号を分周し、クロック信号を生成する第2の分周回路と、を有するクロック生成回路を半導体装置に搭載する。

(もっと読む)

分数分周PLL装置、およびその制御方法

【課題】設定すべきパラメータ数が減ぜられて使い勝手の向上が図られると共に、回路の簡略化を図ることが可能な分数分周PLL装置、およびその制御方法を提供すること

【解決手段】第1分周信号fprの初期のAサイクルの期間は、第2分周信号fAがハイレベル、第3分周信号fBがローレベルに維持される。3モジュラスプリスケーラ13は(M+1)分周値となる。引き続くBサイクルでは、第2分周信号fAがローレベル、第3分周信号fBがハイレベルである。3モジュラスプリスケーラ13は、ΣΔ変調器8から出力される擬似乱数の符号に合わせて、負値の場合に(M−1)分周値、正値の場合に(M+1)分周値となる。その後は、M分周となる。比較分周器4では、擬似乱数値Bxを含む(MN+A+Bx)の分周値が得られる。負値を含む擬似乱数をそのまま使用してΣΔ変調による分数分周を実現できる。

(もっと読む)

タイマ回路及びプログラム

【課題】本発明は携帯装置等のタイマ回路及びプログラムに関し,低周波数(32KHz )の水晶発振子を使用しても長時間の計時を行っても誤差の累積を防ぐことを目的とする。

【解決手段】低周波数の水晶発振子の出力をカウントしてほぼ1ミリ秒毎の出力を発生する第1のカウンタと,該カウンタの出力をカウントしてmミリ秒毎の出力を発生する第2のカウンタと,第2のカウンタの出力を処理装置に供給するタイマ回路であって,第1のカウンタを「32」または「33」のカウント容量の一方でカウントするよう切替える切替回路を設け,第2のカウンタのカウント値が予め設定した分散した多数の値の一つと一致するか判別して切替指示を発生する調整判別回路を備え,切替指示により第1のカウンタのカウント値を切替えることにより,時計回路との誤差が補正された信号が第2のカウンタから出力するよう構成する。

(もっと読む)

記録装置及び記録装置の制御方法

【課題】ディスクの回転に安定して同期した記録クロックを生成できるようにする。

【解決手段】ディスク状記録媒体に形成されているウォブルを読み取ってウォブル信号を検出し、前記ウォブル信号に基いて記録用のクロック信号を生成する記録装置であって、前記ディスク状記録媒体のウォブル周期に関連した周波数を有するクロックを生成する第1のクロック生成手段と、前記ディスク状記録媒体にデータを記録するためのチャネル周期に関連した周波数を有するクロックを生成する第2のクロック生成手段とを備え、前記第1のクロック生成手段に組み込まれているDVCO部と同一のDVCO部を組み込んで前記第2のクロック生成手段を構成する。

(もっと読む)

記録再生装置及び記録再生方法

【課題】回路規模や消費電力を増大させることなく、記録クロック及び再生クロックを安定して生成できるようにする。

【解決手段】ディスク状記録媒体に形成されたウォブル信号を検出するウォブル信号検出手段と、前記ウォブル信号検出手段によって検出されたウォブル信号に基いて、ウォブル周期に関連した周波数を有する第1のクロックを生成する第1のクロック生成手段と、前記第1のクロック生成手段が前記第1のクロックを生成する際の制御信号に予め設定された処理が施された周波数成分を制御信号とし、チャネル周期に関連した周波数を有するチャネルクロックを生成する第2のクロック生成手段とを有し、前記第1のクロック生成手段に組み込む電圧制御発振器と、前記第2のクロック生成手段に組み込む電圧制御発振器とを同一の構成にする。

(もっと読む)

自動周波数制御回路

【課題】 自動周波数制御回路における検出部の起動および停止を簡単に制御し、消費電力を低減する。

【解決手段】 受信パケットから送信装置と受信装置との間のクロック周波数の誤差を検出し、その周波数誤差に対する補正値を出力する検出部と、検出部から出力された補正値に基づいて受信パケットの周波数誤差を補正する補正部とを備えた自動周波数制御回路において、検出部とは別のアルゴリズムで、受信パケットの周波数誤差の有無を簡易に判定し、周波数誤差があれば検出部を動作させ、周波数誤差がなければ検出部の動作を停止させ、検出部の動作時に出力した補正値を受信パケットの周波数誤差の補正に用いる制御を行う簡易判定部を備える。

(もっと読む)

181 - 200 / 351

[ Back to top ]