Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

101 - 120 / 351

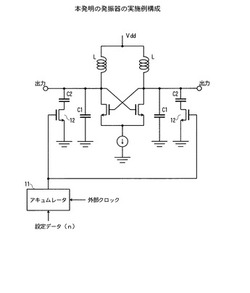

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

クロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路

【課題】動作信頼性を向上させるクロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路を提供すること。

【解決手段】受信信号を再生するタイミング情報が重畳された前記受信信号とリカバリクロックとの位相差に基づいて、前記受信信号とリファレンスクロックとの周波数オフセット情報を検知する周波数差検知部34と、前記周波数検知部34が検知した前記周波数オフセット情報に基づいて、前記受信信号と前記リカバリクロックとの位相差を補正する補正部30とを具備する。

(もっと読む)

PLL回路、PLL回路無線通信機、及びPLL回路のロック検出方法

【課題】デジタル回路で構成出来、ロック検出のエラーやロストの発生を抑制することが出来ると共に、検出時間を短縮することが出来るPLL回路、無線通信機、及びロック検出方法を提供する。

【解決手段】ウィンドウ幅の異なる複数のロック検出部6b−1〜6b−nによる検出結果を用いて検出を行う。ロック判定部7は、複数のロック検出部6b−1〜6b−nによる検出結果に基づいて、ロック状態の検出を行う。

(もっと読む)

半導体装置

【課題】従来のデューティ検出回路では、キャパシタに対するプリチャージ後の充放電動作が、通常のデューティ検出動作中の充放電動作とは異なるものとなり、正確なデューティ検出ができなかった。

【解決手段】内部クロック信号CLKがハイレベルを取る期間とロウレベルを取る期間との比(デューティ比)を積算し、電気的に記憶する記憶部(キャパシタC1,C2)と、記憶部(キャパシタC1,C2)における積算動作(デューティ検出動作)を制御する積算動作制御回路42と、一端が積算動作制御回路42と接続され、他端が電源線(VDD,GND)に接続された定電流回路(バイアストランジスタBTr1,BTr2)と、積算結果を初期化するプリチャージ回路43とを備え、プリチャージ回路43による初期化の実施中に電流回路(バイアストランジスタBTr1,BTr2)に電流を流すようにする。

(もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】ノイズの影響でディレイラインが逆方向に調整されたり、ジッタ成分の影響でループに入ることのないDLL回路を提供する。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD1に基づいて、サンプリング周期ごとにカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が所定の論理レベルを示したことに応答して、同じサンプリング周期内におけるその後の位相判定信号PD0の変化を無効化した位相判定信号PD1を生成する無効化回路200とを備える。これにより、短い周期で位相判定信号に影響を与える成分を排除することが可能となる。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

信号生成回路

【課題】 プロセス要因で生じるクロック信号の位相バラツキを抑える。

【解決手段】 信号生成回路100は、クロック信号PLLCKが通るクロック信号線30に1以上のクロックバッファ31が配置され、1以上のクロックバッファ31によりクロック信号PLLCKを遅延させ、遅延したクロック信号に基づき所定の信号を生成する。この信号生成回路100は、前記クロックバッファ31と同一チップ上に形成された複数のクロックバッファ41を有して構成される参照用クロックバッファ40と、参照用クロックバッファ40の遅延量を検知し、この遅延量と予め定められた遅延量との差に基づく位相調整信号PHADJを出力する遅延検知回路50と、位相調整信号PHADJに応じて、クロック信号PLLCKの位相を変える位相調整回路20と、を備える。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】従来のADPLL回路では、出力クロックにデューティ劣化がある場合、最終的に導き出される位相差に大きな誤差が生じてしまう。

【解決手段】第1クロックをカウントする第1カウンタと、第2クロックを分周した第3クロックをカウントする第2カウンタと、第3クロックの遅延クロックと第1クロックを比較した第1比較結果と、第1クロックの遅延クロックと第3クロックを比較した第2比較結果とに応じ第1、第3クロックの相対的位相差を検出する第1位相検出器と、第2クロックの周期を測定する第2位相検出器と、第2位相検出器の検出結果により第1位相検出器の検出結果を正規化した値と、第1、第2カウンタの値とに応じて第1、第3クロックとの位相差を演算する位相誤差演算部と、位相誤差演算部の演算結果に応じ第2クロックを出力するDCOとを有するデジタルPLL回路。

(もっと読む)

PLL回路

【課題】位相比較回路と、チャージポンプと、ループフィルタと、電圧制御発振回路とがこの順に接続されてなるPLL回路において、ループ帯域幅に変動が起こっても容易に対応できるPLL回路を提供する。

【解決手段】位相比較回路は、電圧制御発振回路から出力される帰還信号と、外部より入力される基準信号とが接続される2入力を備え、チャージポンプは種々の利得に対応した電流源を備え、基準信号と位相比較回路の出力からPLLがロックしたときのロック信号を出力するPLLロック検出回路と、基準信号をカウントするカウント回路と、ロック信号とカウンタ回路のカウンタ信号からロック時のカウンタ信号をラッチするラッチ回路と、基準信号を入力する前に一定の利得に対応した電流源のコードに設定され、基準信号を入力後ロック信号及びラッチされたカウンタ信号から適切な利得に対応した電流源のコードを選択して出力する選択手段とを備えている。

(もっと読む)

基準信号発振装置及び基準信号発振方法

【課題】基準信号の周波数を容易かつすばやく校正し、無線基地局の安定動作を実現すること。

【解決手段】GPSユニット14と、基準信号を発振し、電圧を印加することで前記基準信号の周波数が可変する発振源22と、予め定められた測定時間における基準信号のパルス数を測定し、予め定められた基準パルス数からの測定したパルス数の誤差を示す周波数偏差tfを測定する制御ユニット11と、周波数偏差をなくすために発振源22に印加される電圧値の指標を示す調整基準値を記憶するRAM17と、周波数偏差tfが閾値Bを超えた場合、調整基準値を用いて、基準信号の周波数を補正し、且つ、周波数偏差tfが閾値Bを超えない場合、周波数偏差tfをなくすような電圧値を基準信号発振部に印加することで前記基準信号の周波数を繰り返し補正する制御ユニット11と、を備える。

(もっと読む)

PLL回路

【課題】電圧制御発振器が発振信号出力動作を停止した場合、自動的に最適消費電流で電圧制御発振器の発振信号出力動作を復帰させることができるPLL回路を提供する。

【解決手段】リセット制御回路7は、電圧制御発振器5の発振信号出力動作の停止を検出し、電圧制御発振器5の発振信号出力動作の停止を検出している間、基準信号Ref_CKを分周してなるリセット信号RESETを生成する。カウンタ8は、リセット信号RESETの立ち上がり変化の回数をカウントする。ローパスフィルタ4は、前記リセット信号RESETがLレベルの間に周波数制御電圧Vcntを初期化する。電圧制御発振器5が有する出力アンプは、前記カウンタ8が出力するカウント値Cnt[1:0]が増加する毎に駆動電流を段階的に増加させることにより出力駆動能力を段階的に増加させ、周波数帯域を段階的に上げる。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

デッドロック検出回路およびデッドロック復帰回路

【課題】誤検出することなく、デッドロック状態を正確に検出することができるデッドロック検出回路を提供する。

【解決手段】デッドロック検出回路は、PLL回路のデッドロック状態を検出するものであり、PLL回路の電圧制御発振器の出力信号を分周して、第1の分周クロックを出力するPLL内蔵分周器と、電圧制御発振器の出力信号を分周して、PLL回路の位相比較器へのフィードバッククロックとなる第2の分周クロックを出力するフィードバック分周器と、第1の分周クロックの周期によって決定される所定の期間に含まれる、第2の分周クロックのクロック数に基づいて、デッドロック状態であるか否かを表す判定信号を出力する誤ロック検出回路とを備えている。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

情報システムおよび半導体装置とその制御方法

【課題】周期の小さいジッタに対する低減効果を向上する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路14を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路14における遅延量を制御する。位相補正回路21は、入力クロック信号CLKiおよび出力クロック信号CLKoを入力とし、DLL回路がロック状態に入った後に、入力クロック信号CLKiおよび出力クロック信号CLKoの位相がずれた場合に、出力クロック信号CLKoの位相に基づいて入力クロック信号CLKiの位相に補正を加え、電圧制御遅延回路14に出力する。

(もっと読む)

DLL回路、DLL回路のアップデート制御装置、及びDLL回路のアップデート方法

【課題】本発明は、アップデート条件を緩和させて効率的なアップデートを行い、位相比較感知結果値が不規則に変化しても内部クロックの位相をより正確に制御することができるDLL回路、DLL回路のアップデート制御装置、及びDLL回路のアップデート方法を提供する。

【解決手段】本発明のDLL(Delay Locked Loop)回路は、基準クロックとフィードバッククロックの位相を比較感知して位相感知信号を生成する位相感知手段;前記基準クロックに応答して前記位相感知信号が有する第1論理値と第2論理値の個数の差を判別して有効区間信号とアップデート制御信号を生成するアップデート制御装置;及び前記有効区間信号のイネーブル時に前記アップデート制御信号に応答して遅延ラインに付与する遅延値をアップデートするシフトレジスタ;を備える。

(もっと読む)

DLL回路とその制御方法

【課題】安定的にジッタを低減する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路12を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路12における遅延量を制御する。位相比較結果判定回路15は、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果を所定の期間に亘って積算し、積算結果の分布に基づいて遅延量を制御する。

(もっと読む)

ループ設定調整回路

【課題】ループ回路において、フィードバック遅延やPVT変動を自動的に検出して、ループ設定を調整し最適化することができるループ設定調整回路を提供する。

【解決手段】ループ設定調整回路は、クロックツリーシンセシスがフィードバック経路に挿入されたループ回路のループ特性を決定するループ設定を調整する。ループ設定調整回路は、クロックツリーシンセシスによる遅延時間を検出する検出回路と、検出回路によって検出される遅延時間に相当する時間、遅延時間よりも短い周期の発振クロックを出力する発振回路と、発振回路から出力される発振クロックのクロック数をカウントし、カウント値に対応する制御信号を出力する制御回路とを有し、制御回路から出力される制御信号により、クロックツリーシンセシスによる遅延時間に応じて、ループ設定を調整する。

(もっと読む)

基準クロック周波数の決定および/またはループ発振器のロックを行うための方法、アルゴリズム、回路、およびシステム

【解決手段】 基準クロックの周波数を決定する装置、方法、システム、アルゴリズム、および回路を開示する。一実施形態によると、基準クロックの周波数を検出する回路であって、周波数が既知であり、精度は所定の値であるスリープクロックの所定の部分の間、基準クロックのサイクル数をカウントして、基準クロックサイクルカウント値を得るクロックカウンタと、基準クロックサイクルカウント値および既知であるスリープクロックの周波数に基づいて、基準クロックの周波数を推定する周波数推定部と、複数の許容周波数から、推定された基準クロックの周波数に最も近い周波数を選択する周波数選択部とを備える回路が提供される。 (もっと読む)

101 - 120 / 351

[ Back to top ]