Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

21 - 40 / 351

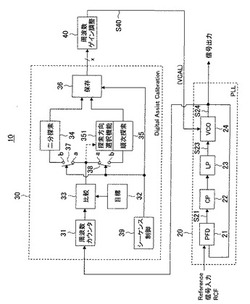

位相同期装置および位相同期回路の周波数キャリブレーション方法、並びにプログラム

【課題】アナログ特性を容易な設計で高速なデジタルアシストが可能な位相同期装置および位相同期回路の周波数キャリブレーション方法、並びにプログラムを提供する。

【解決手段】デジタルアシストキャリブレーション回路は、探索範囲を所定の値から順番に検索値を変更して、検索値と目的値との大小関係を確認する順次探索と、探索範囲の検索値の中央値と上記目的値との大小関係を確認し、目的値が含まれる側の半分の検索範囲に対してのみその半分の検索範囲の検索値の中央値と目的値との大小関係を確認して、目的値を検索していく二分探索と、を選択的に処理可能で、検索過程における最初の過程と最後の過程のうち、少なくとも最初の過程と最後の過程のいずれかにおいて二分探索を行い、残りの過程では順次探索処理を行う。

(もっと読む)

半導体装置、及び情報処理装置

【課題】

安定的な動作を確保できる半導体回路装置、及び情報処理装置を提供することを課題とする。

【解決手段】

半導体装置は、入力信号に遅延を与える遅延部と、前記遅延部から出力される出力信号の位相を検出する位相検出部と、前記位相検出部から出力される位相情報に基づき、前記出力信号の位相の安定動作範囲を設定する設定部と、前記安定動作範囲から位相が外れた前記出力信号の検出回数をカウントするカウンタと、前記遅延部の動作条件又は外的要因に応じて、前記カウンタのカウント数のディスカウント数を表すディスカウント信号を生成するディスカウント制御部と、前記カウンタのカウント数と前記ディスカウント信号が表すディスカウント数とに基づき、前記出力信号の位相のエラーの有無を判定するエラー判定部とを含む。

(もっと読む)

クロック発生装置及びクロック信号生成方法

【課題】CPUに供給するクロック信号の周波数に関わらず、周辺回路に所定の周波数のクロック信号を供給することができるクロック信号生成回路及びクロック信号生成方法を提供する。

【解決手段】本発明にかかるクロック信号生成回路は、CPUに入力される第1クロック信号から、周辺回路に入力される所定の周波数を有する第2クロック信号を生成する。外部から入力される逓倍比及び分周比のうち少なくとも1に基づき、発振子が出力するクロック信号から入力される第1クロック信号を生成する第1クロック生成部と、第1クロック信号から第2クロックを作成するための基準値を算出する基準値算出部と、第1クロック信号のカウント値と基準値との比較結果に基づき、第2クロックを生成する第2クロック生成部とを有し、基準値算出部は、逓倍比及び分周比のうち少なくとも1つが変更され第1のクロック信号の周波数が変更されると、基準値を再度算出する。

(もっと読む)

デジタルPLL回路及びクロック生成方法

【課題】位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供する。

【解決手段】デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器10と、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を範囲に限定されない位相値に補正する補正部11と、補正部の出力する位相値に応じてスレーブクロックを生成するスレーブクロック生成部15とを含む。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

クロック信号生成装置およびクロック信号生成方法

【課題】クロック信号の精度を向上させる。

【解決手段】パルス信号S2を決められた数だけカウントする毎にクロック信号S3を生成する際に、2回の1秒信号S1の出力時点間におけるパルス信号S2の第1カウント数とパルス信号S2の周波数との差分値である第1の誤差を決められた数から増減する補正処理を実行する処理部31〜33を備え、処理部は、1秒信号S1の出力時点から1秒間に生成すべき数のクロック信号S3を生成する毎に出力する1秒完了信号S6の出力時点までの間におけるパルス信号S2の第2カウント数が第1規定値以下のときに第2カウント数を第2の誤差として特定し、第2カウント数が第1規定値よりも大きくかつ周波数の値および第1の誤差を合計した値と第2カウント数との差分値の絶対値が第1規定値以下のときにその差分値を第3の誤差として特定し、補正処理において第1〜第3の誤差の合計値を決められた数から増減する。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

発振装置

【課題】環境温度の検出結果に基づいて出力周波数を補正する発振装置において、出力周波数の温度補償を高精度に行うこと。

【解決手段】共通の水晶片により第1及び第2の水晶振動子を構成すると共に、これら水晶振動子に夫々接続される第1及び第2の発振回路の発振出力をf1、f2とし、基準温度における第1及び第2の発振回路の発振周波数を夫々f1r、f2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分である周波数差をそのときの温度として取り扱う。そしてこの周波数差に基づいて多項式近似により周波数補正値を求める。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

PLL回路

【課題】PLL回路の引き込時間を短縮する。

【解決手段】位相比較器10は、PLL回路100への入力クロックの位相と、PLL回路100の出力から分周器40を介して帰還される帰還クロックの位相とを比較し、その位相差に応じた信号を生成する。LPF20は、位相比較器10の出力信号に応じた直流電圧を生成する。電圧制御発振器30は、LPF20により生成された電圧に応じた周波数のクロックを出力する。サイクルスリップ予測回路50は、位相比較器10により生成される信号を監視し、サイクルスリップの発生を予測する。サイクルスリップ予測回路50によりサイクルスリップの発生が予測されたとき、入力クロックの位相、帰還クロックの位相および電圧制御発振器に入力される電圧のいずれかが調整される。

(もっと読む)

GPSジッタ低減装置

【課題】後段側の装置を軽量に設計することのできるGPSジッタ低減装置を得る。

【解決手段】位相比較調整処理部105は、GPS11が出力する1PPSと、出力パルス生成部104から出力される平滑化された1PPSとの位相差をカウントし、位相差目標値と比較して、固定値にて調整を実施する。出力パルス生成部104は、移動平均処理部103の出力と、位相比較調整処理部105の調整値に基づいて平滑化した1PPSを生成する。

(もっと読む)

基準信号発生装置および基準信号発生方法

【課題】基準信号発生装置全体の消費電力を削減する。

【解決手段】OCXO120が、GPSモジュール110が同期信号を受信している間、当該同期信号を用いて基準信号を発生し、GPSモジュール110が同期信号を受信していない間は、あらかじめ設定された値を用いて基準信号を発生し、温度制御部130が、GPSモジュール110が同期信号を受信している間、OCXO120の温度を所定の温度よりもあらかじめ設定された温度だけ高い温度で変化させ、GPSモジュール110が同期信号を受信していない間は、OCXO120の温度をGPSモジュール110が同期信号を受信しなくなった際の温度に固定させる。

(もっと読む)

位相同期発振器および送信機

【課題】従来に比べて正確にロック状態およびアンロック状態を判定することができる位相同期発振器を提供する。

【解決手段】位相同期発振器はサンプリング位相検波器SPDを備える。サンプリング位相検波器は、基準信号と、電圧制御発振器VCOから出力される発振信号の位相差に応じた電圧信号を出力する。シュミット回路34は、サンプリング位相検波器の出力に応じてパルス信号を生成する。判定回路は、パルス信号の有無に応じてロック/アンロックを判定する。

(もっと読む)

PLL回路、PLL回路の誤差補償方法及び通信装置

【課題】デジタル制御発振器を持つPLL回路に用いられるTDC回路の有限な分解能により発生する周期性誤差を補償することが可能なPLL回路を提供する。

【解決手段】発振回路の累積クロック数をデジタル値として検出する累積クロック数検出部と、前記発振回路の累積クロック数の小数部のデジタル値の、第1の基準クロックを基準とする周期性を検出する周期検出部と、前記発振回路の出力クロックの1周期のデジタル値、前記発振回路の累積クロック数の小数部が持つ周期性の1周期のデジタル値、および前記発振回路の累積クロック数の小数部が持つ周期性の各周期の開始点から前記第1の基準クロック数をカウントした値から補正値を算出する補正値算出部と、前記周期性の各周期の開始点から前記第1の基準クロックの周期で、前記累積クロック数の小数部に前記補正値を加算する加算部と、を備える、PLL回路が提供される。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

PLL回路

【課題】周波数やロックアップ時間が変動したり、PLL特性が劣化したりするのを抑えることのできるPLL回路を提供する。

【解決手段】演算器15a,15bは、出力信号の目標の周波数を示す目標周波数設定値が変化した時、フラクショナル分周器17に対して目標周波数設定値で示される周波数と異なる周波数を示す周波数設定値を複数回設定する。そして、演算器15a,15bが周波数設定値を複数回設定した後に、演算器15a,15bから出力される周波数設定値は、目標周波数設定値と同じ値になる。これにより、周波数の引き込み動作時に、アナログスイッチング素子を用いてループフィルタの切り替えを行う必要がないため、スイッチング切り替え時に発生するノイズや、切り替え前後のループフィルタに生じる電圧差によって、発振器にノイズが発生することがない。

(もっと読む)

送信装置、受信装置及び伝送システム

【課題】簡易な構成によりクロックリカバリを実現し、伝送時のオーバーヘッドを削減する。

【解決手段】送信装置1−1は、制御用メタデータを生成し、制御用メタデータを定期的に受信装置2−1へ送信する。また、送信装置1−1は、コンポーネントの符号化を行い、自身のコンポーネントのクロックを用いてPCR、DTS及びCTSを生成し、または、他のコンポーネントのクロックを用いてDTS及びCTSを生成し、コンポーネントの符号データ等を受信装置2−1へ送信する。受信装置2−1は、制御用メタデータを定期的に受信すると共に、コンポーネントの符号データ等を受信する。そして、受信装置2−1は、制御用メタデータに従って、受信したPCRに基づいて自身のコンポーネントのクロックに対しクロックリカバリを行い、復号等を行う。また、受信装置2−1は、他のコンポーネントのクロックを流用して復号等を行う。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

分周回路およびそれを備えたPLL回路並びに半導体集積回路

【課題】回路規模および消費電力を増大させることなく、回路全体の分周比の可変範囲をより拡大することのできる分周回路を実現する。

【解決手段】周期信号(s5)を2種類の分周比で分周して第1の分周信号(c1)を出力する可変分周器(2)と、第1の分周信号(c1)のサイクル数のカウント値(c2)を出力し、リセットされるとカウント動作を初期値から再開するカウンタ回路(3)と、カウント値(c2)が比較基準値(a)と一致する度にHighとLowとを反転させたパルス信号(s1)を、第2の分周信号として出力するとともに分周比の切替信号として可変分周器(2)に供給し、カウント値(c2)が比較基準値(a)と一致する度にカウンタ回路(3)にリセット信号(r)を出力する比較器(4)と、比較器(4)に比較基準値(a)を供給する制御回路(5)とを備えている。

(もっと読む)

21 - 40 / 351

[ Back to top ]