Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

221 - 240 / 351

PLL回路

【課題】 引込み時間の短縮化が図られたPLL回路を提供する。

【解決手段】 第1のクロックCLK1のN・Y倍の周波数の第2のクロックCLK2が入力されるリセット付分周器18が、断検出回路17で検出された入力クロックCLKINの停止を受けて分周をリセットし、再び入力クロックCLKINが入力されたことが断検出器17で検出されたことを受けて分周を開始して第3のクロックCLK3を生成して位相比較器12に入力する。

(もっと読む)

クロック発生回路

【課題】

サイドバンドを低減する。

【解決手段】

カウンタ22は、基準クロックCLKrefをカウントし、カウント値CNTを比較回路24に印加する。加算器26は、入力端子14からの周波数設定値にN+MビットのDFF28のQ出力を加算し、加算結果をDFF28のD入力に印加する。DFF28は、比較回路24からのイネーブル信号ENと基準クロックCLKrefの立ち上がりと立ち下がりに従い、加算器26の出力をラッチする。加算器32は、ランダム値発生回路30からのランダム値をDFF28のQ出力の上位Nビットに加算し、加算結果を比較回路24に印加する。比較回路24は、両入力が等しいときにイネーブル信号を出力する。インバータ20によりQ出力がD入力に帰還接続されるDFF18は、イネーブル信号と基準クロックCLKrefに従いQ出力をハイからロー又はその逆に遷移する。

(もっと読む)

クロック同期回路及びそれを備えた半導体装置

【課題】複数の回路間で異なるクロックを使用した場合であっても、安定した通信が可能であるクロック同期回路及びそれを備えた半導体装置の提供を課題とする。

【解決手段】受信したデータの変化点を検出し、リセット信号を出力する手段と、クロック信号を出力する基準クロック発生回路と、クロック信号をカウントする基準クロックカウンター回路と、基準クロックカウンター回路から出力された信号を分周する分周回路と、分周回路から出力された信号により回路動作用基準クロック信号を出力する手段とを設ける。

(もっと読む)

PLL回路を備えた半導体集積回路

【課題】製造条件によるデバイス特性のバラツキや使用温度、電源電圧などの使用環境によるデバイス特性のバラツキがある場合でも、未然にVCO6の発振停止を防止すると共に、安定的に起動を行うことができるPLL回路を備えた半導体集積回路を提供する。

【解決手段】PLL回路2の過渡応答時間とデバイス及び使用環境に応じたチャージポンプ4の電流値を、事前にメモリ10に保存しておき、マイコン9からの制御信号ICPctlに基き、チャージポンプ4は、PLL回路2起動時から発振安定時までの過渡応答期間中は、電流値をメモリ10の設定情報に従って低減させる。

(もっと読む)

クロック発生回路

【課題】クロック逓倍してクロック信号を発生するクロック発生回路のロックインタイムを短縮する。

【解決手段】ロックイン状態において、2つの数値データCi,C(i+1)を積和演算器が出力し、各数値データに従って発振器11の発振周期を設定して、その出力クロック信号のパルス数をカウントして第1および第2のカウント値を生成する。これらの2つの数値データと2つのカウント値と周期目標データとに従って、発振器の発振周期を設定する第3の数値データを生成して、発振器の発振周期を設定する。

(もっと読む)

PLL回路

【課題】複数のVCOを有するPLL回路のチップ上の占有面積を削減でき、且つ、PLL回路に対するマイコンの負担を軽減できる。

【解決手段】本発明の例に関わるPLL回路は、位相差信号を出力する位相比較回路1と、位相差信号に基づくチューニング電圧を出力するチャージポンプ回路2と、チューニング電圧に基づく発振周波数を出力する複数のVCO51〜5nと、複数のVCOの中から1つのVCOを自動的に選択するオートセレクト回路を具備し、オートセレクト回路は、チャージポンプ回路2と接続される比較回路3と、比較回路3とVCO51〜5nと接続されるカウンタ4とを具備し、比較回路3は、チューニング電圧に基づき、カウンタ4をアップカウント、又は、ダウンカウントさせるアップ/ダウン信号を出力し、カウンタ4は、アップ/ダウン信号に基づき、複数のVCO51〜5nの中から1つのVCOを選択するセレクト信号を出力することを備える。

(もっと読む)

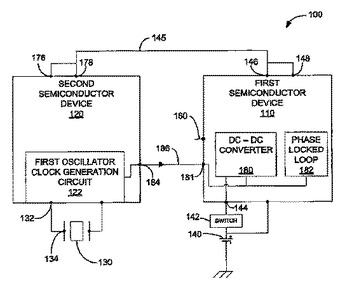

半導体デバイス及び水晶発振体を共有するシステム並びに方法

システムは、第1の半導体デバイス、第2の半導体デバイス、及び外部水晶発振器を含む。第1の半導体デバイスは、電源電圧出力及び外部ピン入力を含む。第1の半導体デバイスは、電源電圧出力を提供する直流−直流(DC-DC)変換回路を含む。第2の半導体デバイスは、第1の半導体デバイスの電源電圧出力に接続された電源電圧入力とクロック信号出力とを含む。外部水晶発振器は、第2の半導体デバイスを介して第1の発振クロック発生回路に接続されている。  (もっと読む)

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】スイッチオーバーから発生する出力信号における不所望の位相変化を信頼性を持って回避することが可能なフェーズロックループ。

【解決手段】制御可能オシレータDCOが出力信号CKoutを発生し、PLL12入力クロックとして使用するために第一クロック/第二クロックCKin2、CKin1を切り換えることが可能である。使用中のCKin1又はCKin2と、CKoutのプリセットされ、位相シフトされたCK<1:8>間の位相差を決定し、DCOを制御するために使用され、使用されていないCKin2又はCKin1がCKoutを発生するために、位相が調節される。入力クロックの幾つかのCKin1,CKin2,CKin3間の位相差がスイッチオーバーの前に調節されることで、スイッチオーバーから発生するPLL出力信号における不所望の位相変化を高い精度で回避し且つヒットレススイッチングを達成する。

(もっと読む)

複数個の出力信号を発生させるフェーズロックループ

【課題】入力クロック信号と同期した複数個の出力クロック信号を調節可能な相対的位相差でもって供給する。

【解決手段】制御可能なオシレータDCOがフェーズロックループの出力信号CKoutを発生し、且つ位相検知器PDがPLL12の入力クロック信号CKinとPLL出力信号CKoutとの間の位相差を決定し、且つオシレータDCOを使用されているクロック信号CKinと同期させる位相検知器出力信号を供給する。ここで、クロック信号CKinと同期されている調節可能な相対的な位相差を有する複数個のPLL出力信号を供給可能にするために、位相差の決定のためにPLLの出力信号CKoutの位相シフトをしたバージョンCK<1:8>を発生し且つ使用されているクロック信号CKinの位相と比較し、且つPLL出力信号CKoutの調節し位相シフトしたバージョンCK<1:8>を更なるPLL出力信号CK<1:8>として供給する。

(もっと読む)

半導体集積回路装置

【課題】DLL回路のリセット時に、より安定して動作させる。

【解決手段】電圧比較回路21は、電源電圧VAAが参照電圧REF以下であれば第1のレベルとなり、電源電圧VAAが参照電圧REFを超えれば第2のレベルとなる比較結果信号を保持回路22に出力する。保持回路22は、比較結果信号が第1のレベルを示す場合には、入力されたリセット信号RSTをそのままDLL回路23に出力し、比較結果信号が第2のレベルを示す場合には、比較結果信号が第1のレベルを示すまでリセット信号RSTを保持してDLL回路23に出力する。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】PLL及びPLLの動作方法に関し、制御可能なオシレータが出力信号を発生し且つPLLの入力クロック信号として使用するために第一クロック信号及び第二クロック信号の間でスイッチオーバーさせる。

【解決手段】現在使用されているクロック信号(CKin1又はCKin2)が出力信号を発生するために、このクロック信号と出力信号との間の位相差が決定され且つオシレータの制御のために使用され、一方現在使用されていないクロック信号(CKin2又はCKin1)が出力信号を発生するために、出力信号に関してのその周波数差が決定され且つ格納され且つ継続的にアップデートされ且つ、前に使用されていないこのクロック信号へのスイッチオーバーの後にオシレータの制御のために提供される。PLL出力信号はどのようなスイッチオーバーに関連する周波数変化よりも迅速に追従することが可能である。

(もっと読む)

半導体集積回路

【課題】 バーンインテスト時のように低周波数の基準クロック信号3を入力した場合にも、電圧制御発振器などのアナログ回路の特性を低周波数用に切り替えることなく、通常時使用する周波数範囲で各構成回路を動作させストレスをかけることで、PLL回路の評価を可能にする半導体集積回路を提供する。

【解決手段】 基準クロック信号3が低周波数のため、電圧制御発振器12の発振周波数が入力電圧対発振周波数特性の下限に達した場合は、周波数検出回路9により、セレクタ回路8がフリップフロップ回路4からの信号を選択するようにセレクト信号7を出力する。発振周波数が入力電圧対発振周波数特性の上限に達した場合は、周波数検出回路9により、セレクタ回路8が内部クロック信号6を選択するようにセレクト信号7を切り替え、発振周波数が、入力電圧対発振周波数特性の下限と上限の間となるようにする。

(もっと読む)

デジタル信号のデューティ・サイクルを補正するための方法および装置

【課題】デューティ・サイクル測定(DCM)回路に供給する基準クロックのデューティ・サイクルの測定、補正方法および装置の提供。

【解決手段】クロック回路は、既知のデューティ・サイクル値で基準クロックのデューティ・サイクルを変動させる。DCM回路は、変動されたデューティ・サイクル対応のチャージポンプ→コンデンサに蓄積される電圧値を得て、データ・ストアに格納する。DCM回路は、未知のデューティ・サイクル値のテスト・クロックから上記と同様の方法で電圧値を得る。制御ソフトウェアはデータ・ストアにアクセスして、テスト・クロック対応のデューティ・サイクルを決定する。装置は、テスト・クロック対応のデューティ・サイクルが所定のデューティ・サイクルとは異なる場合に、誤差を低減するためにテスト・クロック信号のデューティ・サイクルを変更する。

(もっと読む)

クロック生成回路、情報再生装置、電子機器及びクロック生成回路の設計方法

【課題】 PLLを用いることなく、低コスト且つ低消費電力で、複数のクロックを生成するクロック生成回路、情報再生装置、電子機器等を提供する。

【解決手段】 クロック生成回路200は、周波数fHを有する入力クロックiclkに基づいて、第1の出力クロック及び周波数f0を有する第2の出力クロックを生成する。クロック生成回路200は、前記入力クロック又は該入力クロックを間引いたクロックを第1の分周比d1(d1は正の整数)で分周した前記第1の出力クロックを生成する第1の分周カウンタと、前記第1の出力クロックを第2の分周比d2(d2は正の整数)で分周し前記第2の出力クロックを生成する第2の分周カウンタと、前記第2の出力クロックに基づいて、前記第1の分周カウンタで分周される前記入力クロックの間引き制御を行う間引き制御部とを含む。

(もっと読む)

信号受信装置

【課題】小型化および低消費電力化が可能な信号受信装置を提供する。

【解決手段】本発明の信号受信装置は、N個の信号受信ブロック(Nは2以上の整数)を備え、N組のシリアル信号とサイクル数がそれぞれ等しいN個のクロックとを受信する。第1の信号受信ブロックは、第1のクロックと第1の内部クロックとの位相差を表す位相差信号を生成する位相差検出回路と、位相差信号の値に応じて第1のクロックの位相を遅延させた第1の内部クロックを生成する第1の位相遅延回路と、第1の内部クロックに基づいて第1組のシリアル信号を変換するシリアル−パラレル変換回路とを有する。他の第nの信号受信ブロックは、第1の信号受信ブロックからの位相差信号の値に応じて第nのクロックの位相を遅延させた第nの内部クロックを生成する第nの位相遅延回路と、第nの内部クロックに基づいて第n組のシリアル信号を変換するシリアル−パラレル変換回路とを有する。

(もっと読む)

デジタル放送受信装置およびデジタル放送システム

【課題】本発明は、可変周波数の水晶発器(VCXO)を用いること無く、基地局と受信装置間の時間情報および基準クロックの同期を実現することができる、デジタル放送受信装置等を提供する。

【解決手段】水晶発振子22は、所定の固定周波数のクロックを発振する。可変デジタル分周回路24は、固定周波数を分周比によりデジタル分周し、分周比を変更することができる。システムでコーダ5は、基地局からの基準時間情報を検出する。基準カウンタ18は、受信装置20の時間情報を生成する。位相比較器13は、基準時間情報と時間情報との差分を検出する。分周比制御回路25は、前記差分に基づいて前記分周比の変更を制御する。また、基準カウンタ18は、可変デジタル分周回路24により分周された周波数を有するクロックに基づいて時間情報の生成を行い、時間情報を位相比較器13にフィードバックさせている。

(もっと読む)

クロック生成回路

【課題】逓倍回路から正確な逓倍クロックが出力されず、温度等の変動に対する補正能力が低下し、ロックが困難になるという課題があった。

【解決手段】入力された入力クロックの所定逓倍数の出力クロックを供給する逓倍回路40内で、外部からリセット信号が入力されるか、あるいは入力クロックの1周期内にクロック生成回路20の出力クロックのパルス数が所定逓倍数未満の時、カウンタ52を初期化してデジタルディレイライン56の遅延動作を初期化し、初期化直後の遅延時間を最小値に設定し、徐々に遅延時間を増加して所望の逓倍数の出力クロックを生成するものである。

(もっと読む)

PLL回路

【課題】ループフィルタの出力を上限値、下限値と比較して、PLL回路がロックしているかどうかを判定するロック判定回路の上限値、下限値が固定されているので、入力信号の周波数のずれや部品特性のばらつきによっては、キャプチャーレンジがこの上下限値から外れてロックしなくなるという課題を解決する。

【解決手段】ロックしたときのループフィルタの出力の上限値と下限値を上限値/下限値検出回路で検出して保持し、この保持した上下限値をリミット回路に入力し、このリミット回路でループフィルタの出力を前記上下限値の間の値に規制するようにした。ループフィルタの出力電圧が常にキャプチャーレンジ内に規制されるので、入力信号の周波数のずれや部品特性のばらつきに関わらず、確実にロックさせることができる。

(もっと読む)

発振器制御装置

【課題】高精度に電圧制御発振器を制御するとともに、回路面積、消費電流を削減することが可能な発振器制御装置を提供する。

【解決手段】本発明に係る発振器制御装置100は、基準信号Srefと分周信号Sdとを比較し位相差信号を出力する位相周波数検出器1と、この位相周波数検出器が出力した位相差信号に応じて位相誤差信号を出力するチャージポンプ2と、このチャージポンプ2が出力した位相誤差信号をフィルタリングし発振周波数制御電圧Vctrlを出力するループフィルタ3と、電圧制御発振器4と、この電圧制御発振器4の出力を分周する分周器5と、Rカウンタ6と、Nカウンタ7と、Rカウンタ6、Nカウンタ7の出力に基づいて周波数比較信号を出力する第1のコンパレータ8と、電圧制御発振器4、R、Nカウンタ6、7、分周器5、第2のコンパレータ9に信号を出力して制御する制御回路10と、を備える。

(もっと読む)

クロック変換回路

【課題】クロック変換時の収束時間を短縮し安定性を向上する。

【解決手段】位相比較部10は基準クロックをカウントした基準クロックカウンタ値と、供給された再生クロックステップ値を加算して再生クロックのタイミングでラッチした再生クロックステップ値加算結果との位相比較を行い、位相誤差を検出する。ループフィルタ11は検出された位相誤差を平滑化し位相誤差に対応した電圧値を出力する。電圧制御発振部12はループフィルタ11により出力された電圧値により再生クロックを生成する。

(もっと読む)

221 - 240 / 351

[ Back to top ]