Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

161 - 180 / 351

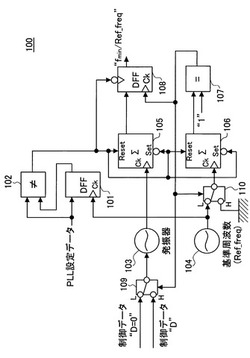

PLL回路、無線端末装置、および周波数検出方法

【課題】DCOの最低発振周波数を検出し、分周比Nに比例した制御データから、DCOの制御データへの変換を精度良く行うことが可能な、新規かつ改良されたPLL回路を提供すること。

【解決手段】ディジタル値を用いて制御される発振回路を有するPLL回路であって、搬送波周波数値を設定する搬送波周波数設定部と、搬送波周波数値が変化したことを検出する検出部と、搬送波周波数値が変化したことを示す信号に同期して、発振回路を最低周波数で発振させるための制御信号を送信し、基準周波数の1周期内の発振回路の出力クロック数を計測する計測部と、を含むことを特徴とする、PLL回路が提供される。

(もっと読む)

デジタルPLL回路

【課題】同期信号消失時の同期維持精度が向上されるとともに簡素な回路構成のデジタルPLL回路を提供することである。

【解決手段】同期信号の入力があるときの2つのクリアパルスの間に含まれる内部クロックの数の時系列的な平均値を学習値として記憶する学習値記憶回路と、PLLクロックカウンタのカウント値が学習値の整数成分と一致したとき一致検出パルスを生成する一致検出回路と、一致検出パルスを内部クロックの1周期分遅延して遅延パルスを生成するフリップフロップと、一致検出パルスまたは遅延パルスのいずれか一方を小数補正信号に従って選択し擬似同期パルスとして出力する擬似同期パルス選択回路と、補正区間において遅延パルスの数の擬似同期パルスの数に対する割合が学習値の小数成分に近似するよう選択する小数補正信号を出力する小数補正演算回路と、を有する。

(もっと読む)

同期クロック生成回路及び同期クロック生成回路を備えたアナログ/ディジタル角度変換器と角度検出装置

【課題】安価に構成することができる同期クロック生成回路を提供する。

【解決手段】角度検出器10の出力する2相の角度信号S1とS2を、第1二乗回路11と第2二乗回路12でそれぞれ二乗し、それぞれの二乗信号を加算回路14で加算し、加算回路14の出力信号の直流成分をフィルタ16で除去する。フィルタ16の出力信号と基準電位とを比較するコンパレータ18で矩形波に変換し、その矩形波の位相を移相器20で所定量遅らせる。移相器20の出力信号を、同期化分周回路22で角度検出器10に供給する励磁信号に同期して1/2分周して同期クロックSQ3を得る。

(もっと読む)

位相ロックループ(PLL)のループ帯域幅を較正するシステムおよび方法

位相ロックループ(PLL)のループ帯域幅を較正する方法が記述される。PLLフィルタの中の少なくとも一つの抵抗器は、入力基準信号の周波数に応じて調整される。前記PLLフィルタ中の一つ又は複数の蓄電器は、入力基準信号の周波数に応じて調整される。一つ又は複数の電圧制御発振器(VCO)の出力パルス群が数えられる。対象のループ帯域幅に関連付けられている第1の電荷ポンプ電流は、前記数えられた出力パルス群に従って数えられる。プログラマブル電荷ポンプ電流は、前記計算された第1の電荷ポンプ電流に合わせられる。  (もっと読む)

(もっと読む)

クロック生成回路およびその使用方法

【課題】基準信号の周波数を逓倍又は分周したクロック信号を生成するクロック生成回路において、一つの基準信号から任意周波数のクロック信号を発生可能とする。

【解決手段】クロック生成回路1は、リング状に連結したm個の遅延素子DUからなるパルス遅延回路10と、各遅延素子DUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの周期を遅延素子DUでの遅延時間を単位として表した周期データDTを生成する周期測定部20と、除数又は乗数として使用される設定値MNを格納する設定値レジスタ50と、周期データDTに、設定値MNを乗・除してクロック信号の出力周期を表す制御データCDを生成する制御部30と、制御データCDと通過信号P1〜Pmとに基づき、基準信号CKIを分周又は逓倍したクロック信号CKOを出力する出力部40とを備え、実数で表された設定値MNを用いる。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

信号生成回路

【課題】基準クロックの周期より細かい周期で制御された複数の出力信号を出力する信号生成回路を提供する。

【解決手段】本発明にかかる信号生成回路は、基準クロックを出力する状態と、基準クロックに基準クロックの1周期より短い第1時間の遅延を持たせた信号を出力する状態と、を切り換え可能な入力段遅延回路10と、入力段遅延回路10の出力が変化した時点から入力段遅延回路10の出力を基準クロックの1周期より短い第2時間保持するゲート回路33を有し、ゲート回路33の出力に対応する信号を出力する制御部30と、制御部30の出力信号に第2時間の遅延を持たせた信号を出力する出力段遅延回路20と、を備え、入力段遅延回路10は、制御部30の出力信号の変化に応答して出力状態の切り換えを行う。

(もっと読む)

DLL回路およびその制御方法

【課題】より向上したデューティ比特性を有するクロックを生成する。

【解決手段】本発明は、デュアルループタイプ(Dual Loop Type)のDLL回路であって、第1位相検知信号に応答し、第1遅延制御信号を生成して第1遅延ラインの遅延量を制御し、第1遅延量情報信号を出力する第1遅延制御手段と、第2位相検知信号に応答し、第2遅延制御信号を生成して第2遅延ラインの遅延量を制御し、第2遅延量情報信号を出力し、前記第1遅延制御信号と半周期情報信号に応答して前記第2遅延ラインの遅延量を再び制御する第2遅延制御手段と、前記第1遅延量情報信号と前記第2遅延量情報信号の入力を受け、基準クロックの半周期情報を抽出して前記半周期情報信号を生成する半周期検知手段と、前記第1遅延ラインの出力クロックと前記第2遅延ラインの出力クロックを組み合わせてデューティ比補正クロックを出力するデューティーサイクル補正手段とを含む。

(もっと読む)

電子機器

【課題】発振子ごとに周波数偏差を0ppmに自動的に合わせ込むことにより、安定した発振周波数を得るとともに、温度偏差も考慮することでさらに安定した発振周波数を得る。

【解決手段】システムコントローラ10は、接続端子T4に周波数カウンタ101が接続されたタイミング、またはリモコン11からの指示信号に基づいて水晶発振子Zを発振させることにより当該水晶発振子Zの発振周波数を調整する調整モードに移行し、周波数カウンタ101によってカウントされた発振周波数が内部に設定されている基準発振周波数と一致するように制御端子T3の印加電圧を制御するとともに、一致したときの印加電圧値をフラッシュメモリ6に記憶して調整モードを終了。以後の機器の動作時には、フラッシュメモリ6に記憶されている印加電圧値を制御端子T3から印加して発振回路17からクロック信号を取得する。

(もっと読む)

小数部の入出力位相に基づいたデジタル位相同期ループ動作

1つの態様では、デジタルPLL(DPLL)は、入出力位相の小数部に基づいて動作する。DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積する。DPLLは、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。 (もっと読む)

注入同期型発振器

【課題】より小型化が可能な周波数逓倍器を提供する。

【解決手段】注入同期型発振器20は、インバータ(22a、22b、22c)を3段リング状に接続してリングオシレータを備えている。そして、2段目のインバータ22bの出力と、3段目のインバータ22cの出力とをnMOSトランジスタ24で接続する構成を採用している。このnMOSトランジスタ24のゲートは、外部から基準周波数信号が供給される。このような構成によって、、リングオシレータの自励発振周波数に近い周波数であって、注入された基準周波数信号と同期した整数倍の周波数で発振が行われる。このように、インジェクションロックを用いて、位相雑音を減らすことができるので、ループフィルタを必要とせず、より小面積で周波数逓倍器を構成することが可能である。

(もっと読む)

位相同期回路

【課題】 中心周波数を変更することなく、外部クロック信号の周波数特性のバラツキにより広く対応でき、周波数特性の安定性向上を図ることができる位相同期回路を提供する。

【解決手段】 外部クロック信号Siを第1入力信号S1、出力クロック信号Soまたはその分周信号を第2入力信号S2とし、これらの位相差に応じた電圧の位相差検出信号Sdを出力する位相比較回路11と、位相差検出信号Sdの所定帯域の信号成分から位相差に応じた電圧値の発振制御信号Sfを出力するループフィルタ12と、発振制御信号Sfの電圧値に応じた周波数で発振する出力クロック信号Soを出力する電圧制御発振回路13と、電圧制御発振回路13の第2入力信号S2がロック状態であるかアンロック状態であるかを検出するロック状態検出回路14を備え、ループフィルタ12が、ロック状態検出回路14におけるロック状態の検出結果に応じて、引き込み範囲を調整する。

(もっと読む)

PLL回路及び無線通信システム

【課題】複数の発振周波数帯域を有するVCOを備えたPLL回路において、設定されたPLL出力周波数に対応する最適な発振周波数帯域の検出動作に要する時間を短縮する。

【解決手段】TDC回路30は、固定分周器2からの所定の基準信号11の立ち上がり時に、その基準信号11と可変分周器7のPLL分周信号15との位相差を求め、更に、前記基準信号の次の立ち上がり時においても同様に、その基準信号とPLL分周信号15との位相差を求める。その求めた2つの位相差情報により、基準信号11の1周期の間にPLL分周信号15が基準信号11に対して進んだ又は遅れた位相量を検出して、基準信号11とPLL分周信号15との周波数の高低を検出する。よって、1つの発振周波数帯域に対して、基準信号11の1周期で周波数比較を完了でき、発振周波数帯域選択回路8は、設定されたPLL出力周波数に対応する最適な発振周波数帯域を短時間で検出する。

(もっと読む)

クロック生成回路

【課題】大きなジッタや周波数オフセットを有する時刻情報が入力された場合でも、ジッタに追従して安定したシステムクロックを、優れたノイズ特性の回路により生成する。

【解決手段】周波数調整範囲が広い1個の電圧発振器を用いるのではなく、それぞれ周波数調整範囲が比較的狭く、かつ、互いに異なる3個のVCXO12〜14を備え、その内で入力PCRの周波数帯に応じて、クロック切替部15と制御部16とからなる選択手段により、周波数調整範囲が最適なものを適応的に選択する。これにより、大きなジッタや周波数オフセットを有するPCRが入力された場合でも、PCRジッタに追従して安定したシステムクロックを生成することができる。VCXO12〜14は、全体としては広い周波数調整範囲を持っていながら、その広い周波数調整範囲を持つ1個のVCXOに比べて発振出力のノイズ特性を優れたものにできる。

(もっと読む)

受信回路及び電子機器

【課題】PLLの低消費電力化、回路規模の低減、設計の困難性の低減。

【解決手段】所定の局部発振周波数IPA,QPAを出力する局部発振回路110を含み、受信信号RFと局部発振周波数IPA,QPAとを乗算した中間周波信号Iin,Qinを出力するアナログ直交復調回路100と、中間周波信号Iin,Qinを入力しフィルタ信号Iout,Qoutを出力する中心周波数と通過帯域とのどちらか少なくとも一方を可変にできる可変バンドパスフィルタ200と、フィルタ信号Iout,Qoutをデジタル信号Idi,Qdiに変換するアナログ−デジタル変換回路310,320と、所定の数値制御発振周波数IPB,QPBを出力する数値制御発振回路410を含み、デジタル信号Idi,Qdiと数値制御発振周波数IPB,QPBとを乗算した復調信号Idm,Qdmを出力するデジタル直交復調回路400と、を含む受信回路。

(もっと読む)

データ駆動回路及び遅延固定ループ回路

【課題】アナログデータ信号のディスプレイパネルへの印加時に発生する誤りなどにも関わらず正常に動作可能なデータ駆動回路及び遅延固定ループ回路を提供する。

【解決手段】第1のデータ信号を第2のクロック信号に基づいてサンプリングし、アナログ変換することにより得られた第2のデータ信号を出力するデータ駆動部と、第2のデータ信号の変化開始時点から所定期間内であることを知らせるマスク信号を生成するマスク信号生成部と、第1のクロック信号から第2のクロック信号−第1のクロック信号と第2のクロック信号の間には遅延が存在し、該遅延は前記第1のクロック信号と第2のクロック信号の間の位相差に応じて変化し、位相差に応じる前記遅延の変化は前記マスク信号により遮断される−を生成する遅延固定ループと、を備える。

(もっと読む)

ジッタ検出回路及び半導体装置

【課題】サイクルトゥサイクルジッタの程度を検出する。

【解決手段】PLL回路(2)の発振クロック信号(vco)の遅延信信号を基準クロック信号(ref)の複数の遅延信号の変化に同期して複数のラッチ回路(23_1〜23_n)にラッチする。ラッチ回路毎にその出力又はその反転信号をセレクタ(24_1〜24_n)で選択する。セレクタ毎にその出力の変化回数をカウンタ(25_1〜25_n)で計数する。制御回路(28)は、発振クロック信号の2nサイクル毎に、前回のセレクタの選択が非反転出力であれば今回カウンタの計数値がn以上のときセレクタの選択状態を反転し、前回のセレクタの選択が反転出力であれば今回前記カウンタの計数値がn以上のときにセレクタの選択状態を反転する。前記第1カウンタの計数値が例えばジッタ検出情報として出力される。

(もっと読む)

位相同期ループ周波数合成に於ける低雑音化の方法

【課題】位相ジッタの少ない位相同期ループ回路を実現する。

【解決手段】第一および第二レジスタへ接続された第一および第二計数手段10,14を含む位相同期ループ回路が開示される。第一レジスタ18は数Mを第二レジスタ20は数Nを記憶する。第一計数手段は基準信号FrefのMサイクルに応答してF1出力信号を出力し、第二計数手段は出力信号FoutのNサイクルに応答してF2出力信号を出力する。F1,F2,Fref,Fout 信号は、位相検出器30へ接続され、FrefとFoutの位相が比較される。位相検出回路の出力信号は位相検出回路出力信号に比例したFout信号を発生する電圧制御発振器12に接続される。Fout信号は位相同期ループ回路が整定するまで第二レジスタへフィードバックされる。

(もっと読む)

位相調整装置

【課題】設計時以降に生じる位相差の変動を内部で自動的に調整することで、予め設定された位相差を有する2つの信号を出力する。

【解決手段】2つのクロック信号の位相差を予め定められた位相差に調整する位相調整装置であって、第1クロック信号に対する第2クロック信号の遅延量を選択的に変更可能な遅延部11と、前記遅延量を制御する制御部12とを備え、前記制御部12は、準備モードにおいて、前記遅延量を第1の時間間隔で段階的に増加又は減少させ、遅れ期間、又は、進み期間を検出し、調整モードにおいて、前記遅れ期間又は前記進み期間と同じ長さの期間において第2の時間間隔で前記遅延量を段階的に変化させることで、前記第2クロック信号の位相差を予め定められた位相差に調整し、前記第2の時間間隔と前記第1の時間間隔との比は、180度と予め定められた位相差との比に等しい。

(もっと読む)

クロック生成制御回路

【課題】 CPUの負荷を軽減することが可能なクロック生成制御回路を提供する。

【解決手段】 本願発明は、発振回路が出力するクロック信号のパルス数を所定期間カウントし、所定期間及び周波数に応じた設定値と等しくなったときにカウント制御信号の出力レベルを切り替えるカウンタと、所定期間を示すタイミング信号とカウント制御信号とのタイミングの誤差を検出し、誤差検出信号を出力する誤差検出回路と、を備え、周波数制御回路は、誤差検出信号に基づいて制御信号を生成することで、上記課題を解決することができる。

(もっと読む)

161 - 180 / 351

[ Back to top ]