Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

321 - 340 / 351

周波数基準信号発生装置および発生方法

【課題】 水晶発振器を用いながらも、その突発的な周波数変化を検知し、状況によっては補正することのできる周波数基準信号の発生装置および発生方法を提供する。

【解決手段】 n個(nは3以上の整数)の例えば水晶発振器を用いた信号発生装置OSC1〜OSCnと、信号発生装置OSC1の出力信号を基準信号として出力する出力信号切換手段SWと、その基準信号を基準にして残りの信号発生装置の出力信号の周波数を検出するn−1個の周波数検出手段(ゲート信号作成回路GSG、パルスカウンタPC1〜PCn−1)を備え、その周波数検出手段の出力は外部に出力される。そして、出力信号切換手段SWは、周波数検出手段の出力に基づいて基準信号の周波数に突発的な変化があったと判断された場合に、制御信号に基づいて他の信号発生装置の出力信号を基準信号として出力するように切り換える。

(もっと読む)

周波数ロック検出器

【課題】 1つのカウンタとクロック個数差検出部とを利用して、位相が同期されない2クロック信号の周波数を比較して、周波数ロックを判別(所望の周波数精度内にあるか否かを判別)することにより、集積化が容易な周波数ロック検出器を提供すること。

【解決手段】 本発明は、周波数ロック検出器において、外部から基準クロック信号を受け取って、基準クロック信号のクロック個数をカウントするためのカウンタと、前記外部から受け取った基準クロック信号と、前記基準クロック信号と互いに位相が同期されない復元されたクロック信号とのクロック個数の差を検出するためのクロック個数差検出部と、前記カウンタと前記クロック個数差検出部の結果値とを利用して、周波数ロックを判別するためのロック判別部とを備える。

(もっと読む)

クロック遅延回路

【課題】選択回路部で選択する遅延クロック信号を切り替える時に生じるジッタを抑制することができるクロック遅延回路を提供する。

【解決手段】本発明のクロック遅延回路は、クロック信号を遅延させた遅延クロック信号を出力する遅延回路部と、遅延回路部から出力される遅延クロック信号を任意に選択して出力する選択回路部とを有しており、遅延回路部と選択回路部との間に直列にジッタ抑制素子が接続されている。

(もっと読む)

PLL回路

【課題】周波数粗調整回路を備えるPLL回路において、その安定性を向上させることができ、ロック時間も短縮することができるようにする。

【解決手段】本発明のPLL回路は、電圧制御発振器の発振周波数を粗調整する周波数粗調整回路を備えている。周波数粗調整回路は、チャージポンプから出力されるコントロール電圧と基準電圧とを比較して、その比較結果となるアップ信号およびダウン信号を出力する比較器と、この比較器から出力されるアップ信号およびダウン信号に応じてアップカウントまたはダウンカウントされ、電圧制御発振器の発振周波数を粗調整するためのカウント値を出力するカウンタとを備えている。そして、比較器から出力されるアップ信号と位相比較器から出力されるダウン信号とがワイヤード接続され、比較器から出力されるダウン信号と位相比較器から出力されるアップ信号とがワイヤード接続されている。

(もっと読む)

発振周波数制御回路

【課題】小型で設計や調整が容易な発振周波数制御回路を提供すること。

【解決手段】入力されるアナログ制御電圧に応じた周波数の発振信号を生成する発振回路から出力される、発振信号の周波数を計数する周波数カウンタと、入力されるデジタル値に応じて前記アナログ制御電圧を生成する複数のD/Aコンバータと、入力される制御信号に応じたデジタル値を生成するデジタル値生成回路と、周波数カウンタにより計数される周波数を基準の周波数と比較して、比較の結果に応じて前記デジタル値生成回路に入力する制御信号を生成する演算回路とを備える発振周波数制御回路を提供する。

(もっと読む)

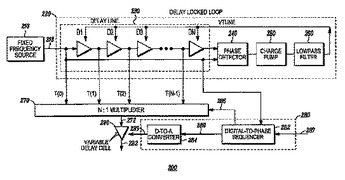

周波数合成の方法と装置

DPC(200)であって、周波数源(20)と、クロック信号を受信し複数の位相シフトされたクロック信号を生成する遅延ロックループ(220)と、合成信号の所望の周波数を識別する入力信号を受信する為の、DPS(282)とDAC(284)とを有した制御装置(280)と、複数の位相シフトされたクロック信号を受信し、位相シフトされたクロック信号の1シーケンスを選択し、粗い合成信号を出力する選択回路(270)と、可変遅延セル(290)とがあるDPC(200)であり、可変遅延セル(290)が、粗い合成信号を修正して、周波数が実質的には所望の周波数である合成信号(292)を生成する為に、粗い合成信号を受信するべく選択回路に結合された第1の入力と、微同調調整信号を受信する為に制御装置に結合された第2の入力とを有している。DPCには更に、DPCを較正するトレーニング装置がある。  (もっと読む)

(もっと読む)

周波数シンセサイザ

【課題】 プリスケーラのモジュラスを大きく維持したまま、可変分周器の総分周数の設定範囲の下限を低減させて基準周波数を高くすることで、ロックアップタイムの短縮と消費電力の削減とを両立する周波数シンセサイザ、を提供する。

【解決手段】 位相比較器(1)、チャージポンプ(5)、及びLPF(2)により基準信号(fr)と比較信号(fd)との間の位相差に応じて生成される制御信号(Vf)に従い、VCO(3)は発振周波数(fv)を調整する。プリスケーラ(6)はVCO(3)の出力信号(fv)を一定のモジュラス((k+2)個の整数からモード信号(S、S1、S2、…、Sk)に従って選択される)で分周する。プリスケーラ(6)の出力パルス(fc)を、メインカウンタ(7)は分周数(N)までカウントし、(k+1)個のスワロウカウンタ(8、9)は順次、各分周数(A0、A1、…)までカウントする。モード制御部(10)は各カウンタ(7、8、9)の出力信号に応じ、モード信号(S、S1、…、Sk)を切り換える。

(もっと読む)

周波数合成器

要約書なし。 (もっと読む)

位相比較器、PLL回路、FLL回路、ビット同期回路、受信装置

【課題】 伝送信号のS/N比が低い場合であっても正確にビット判定を行うことができて、ビット誤りを低減可能な位相比較器、PLL回路、FLL回路、ビット同期回路、受信装置を提供する。

【解決手段】 位相比較器9は、積分器1〜3と、積分器1の出力と積分器2の出力との差を出力する加算器4と、積分器1の出力と積分器2の出力との和を出力する加算器5と、加算器4の出力の極性から各ビットを判定し、ビット判定結果を復調データSdとして出力するビット判定器6と、加算器5の出力の1/2(半値)と積分器3の出力との差を出力する加算器7と、加算器7の出力にビット判定器6の出力を乗じて位相誤差信号Spとして出力する乗算器8とから構成される。積分器1〜3は、前半積分区間信号Sa、後半積分区間信号Sb、中間積分区間信号ScがHレベルのときのみ積分動作を各々行う。

(もっと読む)

位相同期ループ回路

【課題】 ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】 PLL回路内の電圧発振器1で駆動されるカウンタ6と、その出力を周期的に積算するアキュームレータ(ACL)と、ACLのカウント値とレジスタ9に予め設定された設計値とを比較する比較演算回路部8を設け、ACLのカウント値がループ利得と反比例することを応用してPLL回路のループ利得を検出する。検出結果に基づいてチャージポンプ電流等でループ利得の補正を行ってループ利得を校正する。これにより、PLL回路は、PLLを構成する各素子の特性のばらつきに影響しない安定したループ特性を保つことができる。

(もっと読む)

周波数合成器及びその動作方法

【課題】 シグマデルタ変調器を共有して、チップで占める面積を減少させることができる受信及び送信用の分数分周位相固定ループを利用した周波数合成器及び周波数合成方法を提供する。

【解決手段】 CDMA技術等を利用した無線移動通信で、送信チャンネル周波数と受信チャンネル周波数とは一定の間隔を維持する。これを利用して、基準周波数を出力するカウンタの値を調節して、周波数合成器を構成する送信用と受信用の分数分周位相固定ループの小数分周比を同一に維持させると、シグマデルタ変調器と基準周波数を決定するカウンタの数を一つに減少させることができる。従って、周波数合成器のチップ面積を大幅に減少させ、消耗電流量も減少させることができる。

(もっと読む)

信号発生装置

【課題】基準クロック信号が途絶えた場合の動作を実現する構成が、その基準クロック信号の周波数に依存しない信号発生装置を提供する。

【解決手段】第1の位相比較器22は、基準クロック信号と電圧制御発振器12が出力する信号との位相関係に基づく信号PD1を出力する。第2の位相比較器24は、自走クロック発生器が出力する信号と電圧制御発振器12が出力する信号との位相関係に基づく信号PD2を出力する。外部/自走切り換えスイッチ60は、PD1とPD2のいずれかを選択して、ループフィルタ14に入力する。

(もっと読む)

チャージポンプ回路及びPLL回路

【課題】 PLL(Phase Locked Loop)のチャージポンプ回路でアイドルパスを間欠的に有効化することで省電力化を図る場合に、制御の誤動作の起こる可能性が高いロックイン過程において、アイドルパス制御の抑制を行うこと。

【解決手段】 PLLがロックされてロック検出器8の出力iが正論理の時に限り、アイドルパスの制御を行う。基準発振器1と周波数可変発振器2を分周するカウンタ9、10にパルス幅の制御回路11、12を付加し、ラスター信号cとローカル信号dのパルス幅をチャージポンプの電流源の起動に充分な長さに設定する。これら2信号とロック検出器8の反転出力の論理和をとることでアイドルパス有効化信号hを作る。

(もっと読む)

PLLクロック出力安定化回路

【課題】源振クロックで所定サイクル毎に周波数を測定することで、PLL回路が安定したことをLSI内部等で検査可能にする。

【解決手段】PLLクロック出力安定化回路は、基準クロックclkを固定又は可変の逓倍数Nで逓倍してPLLクロックpll_clkを出力するPLL回路10と、一定期間の間、前記PLLクロックpll_clkでカウントアップするカウンタ17と、カウンタ17のカウント値と固定又は可変の逓倍数Nとを比較する比較回路18と、一定期間の間、比較回路18の比較値の等しい状態が続いた回数だけカウントアップするカウンタ20と、カウンタ20のカウント値が安定待ち回数kに達したときに出力イネーブル信号enableを生成し、出力イネーブル信号enableにより、PLLクロックpll_clkを遮断していたゲート回路25を開いてPLLクロックpll_clkを通過させる出力手段とを備えている。

(もっと読む)

通信用半導体集積回路

【課題】 使用周波数帯を決定するまでに要する時間が長くならないとともに回路の占有面積を小さくすることができ、また、リセット信号等の遅延により誤った周波数帯が選択されない自動バンド選択回路を備えたPLL回路を内蔵した高周波ICを提供する。

【解決手段】 VCO11の発振周波数を制御するPLLループにおいて、所定の周波数の基準信号に対する可変分周回路12の出力の位相の進みまたは遅れを判別する判別回路22と、該判別回路の出力に基づいてVCOの周波数帯を切り替える信号を生成する自動バンド選択回路20と、信号の遅延に基づく位相判別におけるずれを測定しそれを補償するような遅延を固定分周回路14で分周された信号に与える遅延補償回路25とを設け、2分探査方式でVCOの周波数帯を切り替えながら最適な周波数帯を見つけて使用周波数帯を決定するようにした。

(もっと読む)

PLL回路のノイズを抑制するシステム及び方法

位相ノイズおよび内部発生器内のミスマッチによって発生するノイズを抑制して周波数ジェネレータのSNRを向上させるシステム及び方法である。このノイズ抑制はスプリアスノイズ信号を発生器のループ帯域幅外にシフトする変調方式によって行われる。このシフトにより、例えば発生器の信号パス上のフィルタを使用して、ノイズ信号を完全に除去できるか又は所望の程度まで除去できる。一実施形態では、所望の程度のノイズ抑制を行うため、シグマデルタ変調器により、PLL回路のフィードバックパス上のパルススワロ分周器の値が制御される。別の実施形態では、PLL回路に入力されるレファレンス信号を変調することにより、ノイズが抑制される。別の実施形態では、所望の周波数シフトを行うため、前記の変調形式が組み合わされる。これら変調技術により、ロックタイムがより速くなるとともに、周波数ジェネレータのSNRが大幅に向上する。  (もっと読む)

(もっと読む)

発振装置及び発振制御方法

【課題】 1PPS信号等の定期信号に基づいて発振周波数を制御する場合に、その受信障害が発生しても好適な周波数での発振を維持することができる発振装置を提供する。

【解決手段】 指示値に応じた周波数で発振する発振部26と、定期信号である1PPS信号を受信するGPS受信機24と、前記定期信号の各受信間隔における発振部26の発振回数を計数するカウンタ22と、計数される発振回数に応じて指示値を順次決定し、発振部26に供給する加算器12及び制御器14と、を含む発振装置10において、制御器14は順次決定される指示値を記憶するとともに、前記定期信号の受信障害が発生した場合に、その記憶内容に基づいて指示値を発振部26に供給する。

(もっと読む)

複数のデジタルクロックの高速同期化方法およびシステム

【課題】異なる周波数でも可能な、自動テスト装置(ATE)のチャネル間の位相と周波数同期化を提供することのできる方法およびシステムを提供する。

【解決手段】本発明は、複数のデジタルクロック(PCLK)を同期信号(SYNC)に同期させる方法を提供する。方法は、基準クロック(RCLK)を中央で生成するステップと、基準クロック(RCLK)からデジタルクロック(PCLK)を、クロック乗算手段を用いて合成するステップと、クロック乗算手段を同期信号(SYNC)に応答してリセットするステップと、クロック乗算手段の出力信号(VCLK)をクロック乗算手段の整定時間中、マスキングするステップと、を含む。

(もっと読む)

通信用半導体集積回路および無線通信システム

受信用VCO(250)と送信用VCO(240a,240b)と中間周波数用VCO(230)のうち少なくとも1つのVCOが変復調回路と共に1つの半導体チップ上に形成された通信用半導体集積回路において、オンチップのVCOを複数の周波数帯で動作可能に構成し、また該VCOの発振周波数を測定する回路(22)および測定された値を記憶する記憶回路(18)と該記憶回路に記憶されている測定値と外部からの設定値とを比較して上記VCOの使用周波数帯を決定する回路(19)を設けるとともに、該記憶回路の記憶データを外部へ読出しまた外部から書き込むことができるように構成した。  (もっと読む)

(もっと読む)

クロック同期回路におけるクロック捕捉

クロック捕捉同期回路は、まず基準クロック信号から同期クロック信号を生成し、そして同期クロック信号を捕捉し、基準クロック信号が除かれた後も同期クロック信号を出力し続ける。クロック捕捉同期回路はまた、同期クロック信号の入力依存ジッタを低減する。本発明により、基準クロック信号が除かれた後、同期クロック信号を出力し続けるクロック同期回路が提供される。また、本発明により、同期クロック出力信号の入力依存ジッタをもし除去しないとしても低減はするクロック同期回路が提供される。  (もっと読む)

(もっと読む)

321 - 340 / 351

[ Back to top ]