Fターム[5J106HH09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | リセット (60)

Fターム[5J106HH09]に分類される特許

1 - 20 / 60

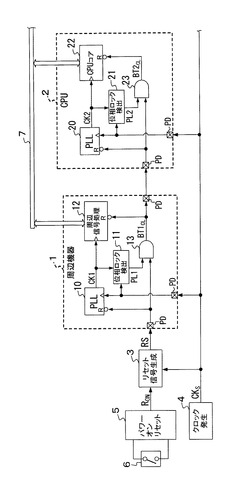

情報処理システム

【課題】システムリセット時の起動時間を短縮可能な情報処理システムを提供する。

【解決手段】複数の機能モジュールの内の機能モジュール1では、システムリセット信号にてPLL回路10及び信号処理部12をリセットした後にPLL回路10へのリセットを解除する。リセット解除後にPLL回路10で生成された内部クロック信号がシステムクロック信号に位相ロックしていない場合には起動中を示す第1の起動状態信号を機能モジュール2に供給する。位相ロックしている場合には起動完了を示す第2の起動状態信号を機能モジュール2に供給すると共に信号処理部12へのリセットを解除する。機能モジュール2では、第1の起動状態信号にてPLL回路20及び信号処理部22をリセットする。そして、第2の起動状態信号にてPLL回路20へのリセットを解除し、リセット解除後に、位相ロックした時に信号処理部22へのリセットを解除する。

(もっと読む)

半導体装置

【課題】DLL回路がロックしないという現象の発生を防止する。

【解決手段】カウンタ回路202と、カウンタ回路202のカウント値CNTに応じた遅延量を内部クロック信号LCLKに与えるディレイライン201とを有する。まず、カウンタ回路202は第1のカウント値にセットされ、判定信号PDに基づいてそのカウント値CNTが周期的に更新される。その結果、内部クロック信号LCLKの位相が所望の位相に到達しなかった場合、カウンタ回路202は、第1のカウント値とは異なる第2のカウント値にセットされ、DLL回路200がリスタートされる。これにより、DLL回路がロックしなかった場合であっても自動的にリスタートされることから、DLL回路がロックしないという現象が防止される。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

位相同期回路、CDR回路及び受信回路

【課題】基準クロックの周波数を低くして消費電力を抑制することのできる位相同期回路を提供する。

【解決手段】第1の位相比較器と第2の位相比較器とに、それぞれ帰還クロックの少なくとも1周期分異なる位相差をつけた分周クロックを入力して基準クロックとの位相比較を行い、受信信号と帰還クロックとの位相比較の結果で第1と第2の位相比較器の出力の重みづけを行い、重みづけされた出力により帰還クロックの位相調節を行う。

(もっと読む)

半導体集積回路

【課題】チップサイズの大型化を防止することができる半導体集積回路。

【解決手段】同一のリセット信号が入力されることにより、互いに同期が取られる複数の送信ブロックを備える半導体集積回路。各送信ブロックは、基準クロック信号とフィードバッククロック信号との位相差に応じた制御電圧に基づいて周期Tの第1のクロック信号を発振する電圧制御発振器と、第1のクロック信号がN(Nは自然数)分周された第2のクロック信号が入力され、当該第2のクロック信号から、第1の送信用クロック信号と当該第1の送信用クロック信号よりも周波数の低い第2の送信用クロック信号とを生成し、リセット信号に応じて少なくとも第2の送信用クロック信号を出力するリセット機能付き分周器と、第1及び第2の送信用クロック信号が分配される複数の送信機と、を備える。

(もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

PLL発振回路

【課題】 アンロック状態を検査すると共に、自動的に再同期する自動リトライ機能を備えるPLL発振回路を提供する。

【解決手段】 MPU4は、外部基準信号とVCXO3からの出力信号の位相を比較してVCXO3への制御電圧を出力するPLL−IC1からのロック検出信号を入力し、ロック状態においてアンロック状態にするためのアンロックアラームテスト用データをPLL−IC1に設定し、PLL−IC1からのロック検出信号によりアンロック状態を判定すると、外部にアンロックアラーム出力信号を出力し、アンロック状態が第1の期間継続しているか否かを判定し、アンロック状態が第1の期間継続していれば、再同期を行わせるためのデータをPLL−IC1に設定するリトライを実行するPLL発振回路である。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

遅延同期ループ回路

【課題】外部クロック信号が擾乱したとき、擬似ロックを検出し初期化したとき、電源を投入したとき、いずれの場合も確実にロックはずれを防止でき、レイアウトがコンパクトなDLL回路を提供する。

【解決手段】遅延同期ループ回路であって、入力クロックを、制御電圧の大きさに応じて遅延させて帰還クロックを出力する電圧制御遅延手段と、帰還クロックと基準クロックとを比較して位相差を検出し、該位相差に応じて、制御電圧を上昇させるための上昇信号と該制御電圧を下降させるための下降信号とを出力する位相比較器と、上昇信号と下降信号とに応じて制御電圧を決定し、電圧制御遅延手段に出力する制御電圧生成手段と、基準クロックと電圧制御遅延手段からの中間クロックとの論理和に基づき位相比較器をリセットする。

(もっと読む)

シンセサイザと、これを用いたシンセサイザモジュール、受信装置、及び電子機器

【課題】位相雑音の劣化の少ないシンセサイザを提供すること。

【解決手段】シンセサイザ1の制御部7は、発振器5に電圧を出力するループフィルタ17の平滑回路に蓄積された電荷を予め設定された値に戻すことなく、温度を検出する温度検出部8の出力信号に基づいて分周器6の分周比を変化させる。これにより、シンセサイザ1は、温度変化に対応して制御部7が分周器6の制御を行う場合、ループフィルタ17の平滑回路に蓄積された電荷を予め設定された値に戻さないので、発振器5の発振周波数が大きく変動することを抑制し、これにより、シンセサイザ1における位相雑音を低減させることができる。

(もっと読む)

位相補償用クロック同期回路

【課題】短時間で精度よく位相調整を行うことが可能な位相補償用クロック同期回路を提供する。

【解決手段】DLLは、入力レシーバ1と、遅延チェーン回路2と、遅延複製器4と、位相比較器5と、リセットパルス発生器6と、粗調整期間発生器7と、分周器8と、単位可変カウンタ9と、を備えている。まず単位可変カウンタ9の増減単位を17または1(平均で16)として粗調整を行って粗くロックさせた後に、単位可変カウンタ9の増減単位を1として微調整を行って細かくロックさせるため、短い期間で確実にクロックINTCKXとクロックEXTCKXの位相を合わせることができる。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

タイミング信号発生回路

【課題】 種々の時間間隔のタイミング信号を低コストで正確に発生させる。

【解決手段】 クロック回路と、クロック信号を入力するカウント回路と、外部から入力する基準タイミング信号を取得し、少なくとも2以上の基準タイミング信号を含む所定の2時点間のカウント回路のカウント値の増分と、該2時点間の時間とを対応させて記録する記憶回路と、カウント回路が所定の2時点間に対応するカウント値だけ増分した時点を中心とする所定の期間に基準タイミング信号を取得し、基準タイミング信号を受信した時点のカウント回路のカウント値を所定の2時点間に対応するカウント値として記録し、所定の2時点間の時間を周期とするタイミング信号をカウント回路のカウント値の増分を契機として発生させ、さらに基準タイミング信号を取得し、基準タイミング信号を取得した時点からカウント値の増分を計数し直す制御手段とを備える。

(もっと読む)

タイミング回復のためのサイクルスリップ検出

【課題】タイミング回復のためのサイクルスリップ検出の提供。

【解決手段】タイミング回復のために制御ループ中のループフィルタLFの出力信号を使用するステップと、前記フィルタ処理後のタイミング誤差信号から平均タイミング誤差値を生成するステップと、第1の閾値を超えるサンプルの隣接するブロックの平均タイミング誤差値の変化を累積するステップとを含む。第2の閾値を超える隣接するブロックの累積した平均タイミング誤差変化がサイクルスリップとして表明され、サイクルスリップの数が許容閾値である第3の閾値によって決定される。さらに、先入れ先出しメモリFIFOがサンプル挿入または削除のために設けられ、それは、サンプル挿入またはサンプル削除が向上した信頼性を伴ってサンプル領域で行われ、サイクルスリップ検出の改善された方法が雑音および不適切に選ばれたタイミングループパラメータに対する頑健性の増強のために推奨される。

(もっと読む)

PLL位相合わせ回路

【課題】PLL回路のリファレンスクロックが停止された後に再開された場合、再開後のリファレンスクロックとフィードバッククロックとの位相合わせを短時間で行い、再ロックさせることができるPLL位相合わせ回路を提供する。

【解決手段】PLL位相合わせ回路は、PLL回路と、フィードバッククロックを分周する第1の分周回路と、PLL回路の出力クロックを分周する第2の分周回路と、リファレンスクロックの動作状態を監視するクロックモニタ回路とを備える。第1の分周回路の分周数は、第2の分周回路の分周数と等しく、クロックモニタ回路が、リファレンスクロックが停止されたことを検出すると、第1の分周回路がリセットされてフィードバッククロックが停止され、リファレンスクロックが再開されたことを検出すると、第1の分周回路のリセットが解除されてフィードバッククロックが再開される。

(もっと読む)

PLL回路

【課題】同期信号の位相が大きく変化する場合にも、短時間で位相を同期させる。

【解決手段】本PLL回路における位相比較器10は、映像信号に含まれる同期信号SYNと位相比較信号BLKとの位相誤差を示す比較出力信号PDPを出力し、VCO30は、比較出力信号PDPを積分するLPF20から与えられる直流電圧に応じた周波数のクロック信号CKを出力する。カウンタ40は、クロック信号CKを分周した位相比較信号BLKを出力する。ロック確認回路50は、位相比較信号BLKと同期信号SYNとの位相が同期すべきロック状態であるか否かを確認し、ロック状態でない場合にはリセット信号RSTを出力し、カウンタ40をリセットすることにより強制的にロック状態にすることができる。よって、短時間で位相を同期させることができる。

(もっと読む)

クロック再生回路

【課題】短いビット同期時間、クロックワンダー追随性能、高い高周波ジッタ耐性、を同時に満たすクロック再生回路を提供する。

【解決手段】入力データ信号101と再生クロック102との位相差を検出する位相差検出回路103、位相差検出回路103の出力を平均化する平均化回路104、位相差検出回路103の出力をサンプル/ホールドするリセット付サンプル/ホールド回路105、平均化回路104の出力の積分値とリセット付サンプル/ホールド回路105の出力値との和に相当する位相の再生クロック102を生成する再生クロック生成回路106を備える。リセット付サンプル/ホールド回路105は、バースト伝送開始信号110を受けて位相差検出回路103の出力をサンプル/ホールドし、バースト伝送終了信号111を受けてホールドしている値を初期値にリセットする。

(もっと読む)

位相同期ループ周波数合成に於ける低雑音化の方法

【課題】位相ジッタの少ない位相同期ループ回路を実現する。

【解決手段】第一および第二レジスタへ接続された第一および第二計数手段10,14を含む位相同期ループ回路が開示される。第一レジスタ18は数Mを第二レジスタ20は数Nを記憶する。第一計数手段は基準信号FrefのMサイクルに応答してF1出力信号を出力し、第二計数手段は出力信号FoutのNサイクルに応答してF2出力信号を出力する。F1,F2,Fref,Fout 信号は、位相検出器30へ接続され、FrefとFoutの位相が比較される。位相検出回路の出力信号は位相検出回路出力信号に比例したFout信号を発生する電圧制御発振器12に接続される。Fout信号は位相同期ループ回路が整定するまで第二レジスタへフィードバックされる。

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

1 - 20 / 60

[ Back to top ]