Fターム[5J500AC92]の内容

Fターム[5J500AC92]の下位に属するFターム

コンデンサの不要化 (39)

コイル(インダクタンス)を不要とする (17)

抵抗を不要とする (18)

トランスを不要とする (10)

Fターム[5J500AC92]に分類される特許

21 - 40 / 661

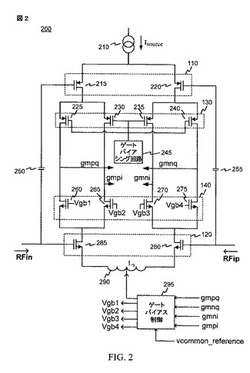

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

【課題】差動入力を有する直交出力低雑音トランスコンダクタンス増幅器を提供する。

【解決手段】低雑音トランスコンダクタンス増幅器200は、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部110と、PMOSトランスコンダクタンス部に結合されたPMOSカスコード部130と、RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部120と、NMOSトランスコンダクタンス部に結合されたNMOSカスコード部140と、を含み、PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号gmpq、gmnq及び差動同相出力信号gmpi、gmniを提供する。RF信号を増幅するための方法は、差動RF入力信号を受信することと、差動RF入力信号を電流信号に変換することと、電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供する。

(もっと読む)

RF電力増幅器およびその動作方法

【課題】ランプアップまたはランプダウンにおいてスイッチングスペクトラムの劣化を軽減すること。

【解決手段】初段と最終段のバイアス回路81、83が、初段と最終段の増幅回路41、43のアイドリング電流を決定する。電力検出回路5、6は、最終段出力信号Poutの信号レベルに応答する電力検出信号VDETを生成する。誤差増幅器7に検出信号VDETと目標電力信号VRAMPが供給され、電力制御電圧VAPCが制御信号増強回路9の入力に供給され、出力から増強制御信号VENを生成する。制御信号増強回路9は、所定の非線型の入出力特性を有する。増強制御信号VENが初段と最終段のバイアス回路81、83とに供給され、初段と最終段の増幅回路41、43のアイドリング電流は増強制御信号VENによって制御され、RF電力増幅器の制御利得の低下が補償される。

(もっと読む)

送信装置及びこの送信装置で使用される制御方法

【課題】EXCITERユニットの簡素化、コスト削減の実現を可能にする。

【解決手段】送信装置は、電力増幅部13と、送出部15と、冷却部27と、温度検出手段181と、出力電力検出手段182と、冷却制御手段183とを備えている。電力増幅部13は、伝送信号を電力増幅する。送出部15は、電力増幅部13の出力を伝送路へ送出する。冷却部17は、電力増幅部13を冷却する。温度検出手段181は、電力増幅部13の温度を検出する。出力電力検出手段182は、電力増幅部13の出力電力を検出する。冷却制御手段183は、温度検出手段181の検出結果及び出力電力検出手段182の検出結果に基づいて、冷却部17の冷却処理を制御する。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

電力増幅回路

【課題】簡単な構成により利得を下げずに効率を向上させることができる電力増幅回路を得る。

【解決手段】基板1上に、熱感応式分配器2、電力増幅素子3a,3b、及び合成器4が設けられている。熱感応式分配器2は、入力信号を最大で2つに分配する。電力増幅素子3a,3bは、分配された入力信号をそれぞれ電力増幅する。合成器4は、電力増幅素子3a,3bの出力信号を1つに合成する。電力増幅素子3a,3bで発生した熱が、基板1を介して熱感応式分配器2に伝わる。熱感応式分配器2は、温度が高くなるほど多くの電力増幅素子3a,3bに入力信号を分配する。

(もっと読む)

変調器およびそれを用いる増幅器

【課題】寄生振幅変調を自動的に除去し、LINC変調器の出力端子で変調器に入力される信号を再構成する変調器を提供する。

【解決手段】非線形コンポーネントを有するLINC変調器は、ソース信号から複数の定数包絡信号を生成する分離器と、前記複数の定数包絡信号が通過する複数のアームであって、入力信号の第一の周波数部分を含む第一の信号を生成するフィルタと、前記第一の信号の前記第一の周波数部分とは異なる周波数である、前記入力信号の第二の周波数部分を含む第二の信号を生成し、前記第一の信号と前記第二の信号を用いて定義される、前記第二の信号の周波数信号ディストーションを実行し歪んだ信号を生成するプロセッサと、前記第一の信号と前記歪んだ信号を掛け合わせて前記定数包絡信号を再構成する直交変調器と、を含む複数のアームを含む。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

信号処理装置

【課題】 抵抗及び小さな静電容量を用いた回路により、検出素子の出力信号を直流成分を除いて増幅する小型な信号処理装置を得る。

【解決手段】 入力信号が第1のインピーダンスを介して反転入力端子に入力される第1のオペアンプと、第1のオペアンプの反転入力端子と出力端子とに接続された第2のインピーダンスと、基準電圧が非反転入力端子に入力され、出力端子が第1のオペアンプの非反転入力端子に接続された第2のオペアンプと、第2のオペアンプの反転入力端子と出力端子とに接続された第1の静電容量と第1のスイッチと、第2のスイッチを介して第1のオペアンプの出力端子と前記第2のオペアンプの反転端子とに接続された第3の抵抗と、第3のスイッチを介して第1のオペアンプの出力端子と第2のオペアンプの反転端子とに接続された第4の抵抗とを備えた。

(もっと読む)

全差動増幅器

【課題】初期動作を安定させるスタートアップ回路を備え、消費電力を低減すると共に、回路規模の増加を抑制した全差動増幅器を提供する。

【解決手段】図1に示す全差動増幅器は、入力信号を受け付ける差動対を含み、差動信号を出力する差動増幅器と、差動信号を増幅し、差動出力信号から出力コモンモード電圧を生成する出力コモンモード電圧生成回路と、出力コモンモード電圧と所定の基準電圧を比較することでコモンモードフィードバック信号を生成し、コモンモードフィードバック信号を差動増幅器にフィードバックすることで、出力コモンモード電圧と基準電圧を実質的に一致させるコモンモードフィードバック回路と、入力信号に基づいて、差動信号を略電源電圧にプルアップ又は略接地電圧にプルダウンするスタートアップ回路と、を備える。

(もっと読む)

制御整合ステージを備える装置

【課題】比較的簡単な、制御整合ステージ、方法、およびプロセッサ・プログラム製品を提供する。

【解決手段】第1のステージに第2のステージを整合させるための制御整合ステージ10を備え、制御整合ステージは、第1のステージの出力信号から第1の信号と第2の信号とを導出するための導出手段11と、第1の信号と第2の信号の間の位相を検出するための検出手段12と、前記整合のために前記検出に応じて調整可能インピーダンス・ネットワーク14を制御するための制御手段13とを備える。

(もっと読む)

高周波電力増幅器

【課題】出力電力に応じて出力経路を選択することにより、中出力および低出力における電力効率を向上させた高周波電力増幅器を提供する。

【解決手段】PAモジュール100は、HBT101及び102が配置された高出力経路HR1と、HBT103が配置された中出力経路MR1と、HBT104が配置された低出力経路LR1とを含み、HBT103の出力ノードに接続されたインピーダンス変換回路117と、一端が上記出力ノードと出力端子との間に接続され、他端がコンデンサ135に接続されたスイッチ105と、HBT104の出力ノードと出力端子との間に接続されたインピーダンス変換回路116とを具備し、スイッチ105がオフ状態の場合、上記接続ノードから出力端子を見たインピーダンスを50Ωより小さいインピーダンスに変換し、HBT104の出力ノードから出力端子を見たインピーダンスを50Ωより大きいインピーダンスに変換する。

(もっと読む)

高周波電力増幅器

【課題】レイアウト面積を増加させることなく、各トランジスタの負荷インピーダンスを均一にすることができる高周波電力増幅器を得る。

【解決手段】半導体チップ2上に、トランジスタ3a,3bと、トランジスタ3a,3bに隣接したコレクタパッド4a,4bとが設けられている。トランジスタ3a,3bとコレクタパッド4a,4bはそれぞれコレクタ配線6a,6bにより接続されている。半導体チップ2外に外部パッド8が設けられている。この外部パッド8に出力端子9が接続されている。コレクタパッド4a,4bと外部パッド8はそれぞれワイヤ10a,10bにより接続されている。コレクタパッド4aは、コレクタパッド4bよりも外部パッド8から遠い位置に配置されている。コレクタパッド4aから出力端子9までの電気長は、コレクタパッド4bから出力端子9までの電気長と同じである。

(もっと読む)

保守運用支援装置

【課題】本発明は、機能、性能、特性等が点検の対象となるべき回路を備えた装置の保守や運用に供される保守運用支援装置に関し、構成が大幅に変更されることなく、負帰還の対象となる構成要素が異なる特性の要素で交換されても、様々な無線伝送系に対する柔軟な適応を安価に実現できることを目的とする。

【解決手段】回路の負荷に代えて擬似負荷が前記回路に接続された第一の状態で、前記回路に負帰還を施すことにより、前記回路の特性の設定、校正、監視の何れかに供される情報を得る制御手段と、前記擬似負荷の定格が確保される特定の値に、前記負帰還のループ利得を設定するループ利得設定手段と、前記擬似負荷に代わって前記負荷が前記回路に接続された第二の状態で、前記回路に対する前記情報の反映を図る反映手段とを備える。

(もっと読む)

保守運用支援装置

【課題】本発明は、機能、性能、特性等が点検の対象となるべき回路を備えた装置の保守や運用に供される保守運用支援装置に関し、構成が大幅に変更されることなく、多様な変調方式の組み合わせに対して柔軟に精度よく適応できることを目的とする。

【解決手段】回路の負荷に代えて擬似負荷が前記回路に接続された第一の状態で、前記回路を負帰還を施すことにより、前記回路の特性の設定、校正、監視の何れかに供される情報を得る制御手段と、前記擬似負荷に代わって前記負荷が前記回路に接続された第二の状態で、前記回路に対する前記情報の反映を図る反映手段とを備え、前記制御手段は、前記回路に入力される信号の信号空間上における振幅が複数通りある場合と1通りである場合とに、前記回路が出力する信号の振幅の尖頭値と平均値とに基づいてそれぞれ前記負帰還を施す。

(もっと読む)

利得制御装置および回路モジュール

【課題】本発明は、利得制御装置および回路モジュールに関し、構成の大幅な変更と性能の低下とを伴うことなく、ハードウェアの規模の縮小を可能とすることを目的とする。

【解決手段】回路に入力された入力信号、または出力された出力信号の周波数に対応して、前記回路に対する前記出力信号の負帰還に供される帰還路に設定されるべき利得が予め登録された記憶手段と、前記周波数に対応して前記記憶手段に登録された利得を前記帰還路に設定する制御手段とを備え、前記記憶手段には、前記周波数が分布し得る帯域の内、前記負帰還の下で前記出力信号のレベルが既定の範囲内に維持される部分帯域毎に、前記利得が共通の利得として登録され、前記制御手段は、前記部分帯域の内、前記周波数が属する特定の部分帯域に対応して登録された共通の利得を前記帰還路に設定する。

(もっと読む)

自動利得調整回路

【課題】利得可変回路の出力振幅の温度依存性を低減する。

【解決手段】自動利得調整回路は、利得可変回路3の出力信号のピーク電圧を検出するピーク検出回路10と、利得可変回路3の出力信号の平均値電圧を検出すると共に、平均値電圧に利得可変回路3の所望の出力振幅の1/2の電圧を加える平均値検出・出力振幅設定回路11と、ピーク検出回路10の出力電圧と平均値検出・出力振幅設定回路11の出力電圧との差分を増幅して、増幅結果を利得制御信号として利得可変回路3の利得を制御する高利得アンプ12とを備える。ピーク検出回路10の入力端子から出力端子までの経路に挿入されるトランジスタのベース−エミッタ接合の数と、平均値検出・出力振幅設定回路11の入力端子から出力端子までの経路に挿入されるトランジスタのベース−エミッタ接合の数とは同一である。

(もっと読む)

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

スイッチングアンプ

【課題】 簡単な回路構成であり、かつ、正確に、電源電圧のパンピング現象、および、出力電圧の直流成分を検出すること。

【解決手段】 トランジスタQ1は、スイッチングアンプの出力電圧に正の直流電圧が含まれることを検出する機能と、正側電源電圧+VBにパンピング現象が生じていることを検出する機能とを兼有する。トランジスタQ2は、スイッチングアンプの出力電圧に負の直流電圧が含まれることを検出する機能と、負側電源電圧−VBにパンピング現象が生じていることを検出する機能とを兼有する。パンピング現象が生じていない場合、ツェナーダイオードD1、D2は共にオフ状態である。従って、抵抗R4、R5が、直流電圧検出の精度の低下を防止できる。

(もっと読む)

半導体装置とその動作方法

【課題】半導体装置において、消費電力を低減する。また、スタンバイ回路を少ない素子で構成し、半導体装置の回路面積の増大を防ぐ。

【解決手段】半導体装置に備えるスタンバイ回路をトランジスタ一つのみで構成し、該トランジスタに供給する電圧を切り替えることで、半導体装置の出力電流を制御する。これにより、スタンバイ状態での半導体装置の出力電流をほぼゼロにすることができるため、消費電力の低減が可能になる。なお、トランジスタの半導体層に酸化物半導体を用いることで、リーク電流を極小に抑えることができる。

(もっと読む)

21 - 40 / 661

[ Back to top ]