Fターム[5J500AC92]の内容

Fターム[5J500AC92]の下位に属するFターム

コンデンサの不要化 (39)

コイル(インダクタンス)を不要とする (17)

抵抗を不要とする (18)

トランスを不要とする (10)

Fターム[5J500AC92]に分類される特許

81 - 100 / 661

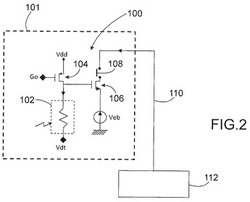

抵抗式熱検出器にバイアスをかけて読み取るための電子回路

【課題】画素のSN比を改良するために読み取り回路によりもたらされるノイズを低減する。

【解決手段】少なくとも1つの抵抗式熱検出器(102)にバイアスをかけて読み取るための電子回路(100)であって、抵抗式熱検出器の電気抵抗に変動があると、抵抗式熱検出器に一定値のバイアス電流を流すことによって抵抗式熱検出器にバイアスをかけることができるバイアス手段と、抵抗式熱検出器(102)の端子で電圧を電流に変換することができ、抵抗式熱検出器の端子の一つにゲートが電気的に接続させる少なくとも1つのMOS型トランジスタ(106)を備える変換手段と、変換手段のMOS型トランジスタのソースに電気的に接続されるベースクリップ電圧生成手段とを備える電子回路を提供する。

(もっと読む)

電力増幅器

【課題】チップサイズを増加させることなく、使用する経路に応じてフィードバック経路の接続・未接続を切替えることができる電力増幅器を得る。

【解決手段】スイッチSW1は、制御信号に従って入力端子Tin1を出力端子Tout1と出力端子Tout2の何れかに接続する1入力多出力のスイッチである。スイッチSW1の入力端子Tin1は、トランジスタTr1のコレクタ(出力端子)に接続されている。フィードバック経路12は、スイッチSW1の出力端子Tour1をトランジスタTr1のベース(入力端子)に接続させる。

(もっと読む)

差動増幅器及びデータドライバ

【課題】従来の差動増幅器は出力誤差が増大する問題がある。

【解決手段】本発明の差動増幅器は、内挿機能を有し、第1導電型トランジスタで形成される第1、第2の差動対(21、22)と、第2導電型トランジスタで形成される第3、第4の差動対(23、24)と、第1、第2の差動対に動作電流を供給する第1、第2の電流源(41、42)と、第3、第4の差動対に動作電流を供給する第3、第4の電流源(43、44)と、第1、第2の差動対にそれぞれ流れる電流量が第1、第2の電流源が出力する動作電流よりも小さくなる第1の動作範囲において、第1の差動対に供給される動作電流の変化点を制御する第1の制御回路51と、第3、第4の差動対にそれぞれ流れる電流量が第3、第4の電流源が出力する動作電流よりも小さくなる第2の動作範囲において、第4の差動対に供給される動作電流の変化点を制御する第2の制御回路52と、を有する。

(もっと読む)

チョッパ増幅とデジタル変換の複合回路

【課題】チョッパアンプの出力電圧には所定時間毎に反転する増幅後電圧(Vs)または所定時間毎に反転するオフセット電圧が含まれており、出力電圧から増幅後電圧(Vs)のみを取出してデジタル変換する必要があり、回路が大規模化する。

【解決手段】チョッパアンプとデジタル変換回路を構成する比較回路の間に伝達回路を設ける。伝達回路は、重畳電圧(V1)とデジタル値から変換したアナログ電圧(Vd)を入力し、2種類の電圧(第1出力電圧(VI),第2出力電圧(VII))を出力する。第1出力電圧(VI)と第2出力電圧(VII)の差は、増幅後電圧(Vs)とアナログ電圧(Vd)の差に比例している。この結果、比較回路で増幅後電圧(Vs)とアナログ電圧(Vd)の大小関係を判別することができ、カウンタ回路のカウント値をアップまたはダウンさせ、カウント値を増幅後電圧(Vs)に追従させることができる。

(もっと読む)

電流電圧変換回路、物理量測定装置

【課題】 回路規模の増加を抑えつつ、高い精度の電流電圧変換を行い、低ノイズの電圧信号を出力する電流電圧変換回路等を提供する。

【解決手段】 電流電圧変換回路10であって、電圧信号101P、101Nを出力するオペアンプ20と、入力された電流信号100P、100NのDCオフセット電流に応じた電荷を充放電する第1のキャパシタ40P、40Nと、オペアンプのオフセット電圧に応じた電荷を充放電する第2のキャパシタ41P、41Nと、第1の期間においてオン状態となり第2の期間においてオフ状態となる第1のスイッチ30P、30Nおよび第3のスイッチ32P、32Nと、第1の期間においてオフ状態となり第2の期間においてオン状態となる第2のスイッチ31P、31Nとを含む。

(もっと読む)

スイッチトキャパシタ積分および加算回路

【課題】単一の演算増幅器を使用して積分器と加算器の両方を実現するスイッチトキャパシタ回路を提供する。

【解決手段】1つの入力信号は、(1)1つまたは複数の積分ブランチと、(2)1つまたは複数の第1の加算ブランチとを介して演算増幅器の入力に送られる。第2の入力信号は、1つまたは複数の第2の加算ブランチを介して演算増幅器の入力に送られる。ブランチの各々は、キャパシタと、異なるクロック位相によって制御されるいくつかのスイッチとを含む。スイッチトキャパシタ回路はシングルエンドまたは差動とすることができる。

(もっと読む)

歪補償装置及び無線基地局

【課題】データテーブルの更新期間中も無線基地局の運用を停止する必要がなく、しかも、装置規模及び製造コストの増大を回避しつつ、高精度の歪補償を実現することが可能な、歪補償装置を得る。

【解決手段】DPD処理部2は、HPA6の入出力特性の歪を補償するための、複数の補正データを含むデータテーブル24を記憶する記憶部23と、データテーブル24に基づいてHPA6への入力信号S1を補正することにより、歪補償処理を実行する歪補償部21と、データテーブル24の更新処理を実行する更新部30と、を備え、更新部30が、データテーブル24の一部の領域に関して、補正データの読み出しを制限した状態で更新処理を実行しつつ、歪補償部21が、データテーブル24の他の領域に基づいて歪補償処理を実行する。

(もっと読む)

半導体集積回路

【課題】DCオフセットキャンセル回路の回路規模と消費電力とを低減する。

【解決手段】差動増幅器5の非反転出力端子と反転出力端子にDCオフセットキャンセル回路51の差動入力端子が接続され、キャンセル回路51の出力信号は差動増幅器5の出力DCオフセット電圧を低減する。回路51はオンチップローパスフィルタ51と直流制御増幅器512を有し、フィルタ511は第1定電流源CS1、差動対の第1と第2のトランジスタ素子Mp1、Mp2、オンチップ容量C1を含む。第1定電流源CS1は素子Mp1、Mp2の共通電極に接続され、回路51の差動入力端子Vinp、Viinは素子Mp1、Mp2の制御入力電極に接続される。オンチップ容量C1の一端と他端に素子Mp1、Mp2の出力電極とが接続され、直流制御増幅器512は容量C1の両端の電圧に直流的に応答する。

(もっと読む)

電力増幅器および送信機

【課題】従来に比べて小さな占有面積で配置され、かつ、出力信号の損失をできる限り低減することができる電力増幅器および送信機を提供する。

【解決手段】電力増幅器16はハイブリッド電力分配器22およびハイブリッド電力結合器23の間に設けられたアンプ回路24を有するバランスアンプ21を備える。ハイブリッド電力結合器23のアイソレーションポート23dに検波回路27が接続される。

(もっと読む)

レベルシフト回路及びその方法

【課題】レベルシフト回路及びその方法の提供。

【解決手段】本発明のレベルシフト回路及びその方法は、レベルシフト回路のラッチ装置と電圧源の間に限流回路を接続して、前記ラッチ装置の駆動電流が設定値を超えないように制限する。これにより、レベルシフト回路を変換する時の消耗電流を減らし、通路の短いトランジスタを使用したラッチ装置を実現し、レベルシフト回路面積を縮小する。前記設定値は調節可能とし、レベルシフト回路の出力駆動能力を調整することにより、前記レベルシフト回路の変換速度を加速させることができる。

(もっと読む)

高周波電力増幅器

【課題】高周波電力増幅器と方向性結合器を多層基板内に一体化した高周波モジュールであって、小型、低コスト、高性能な高周波モジュール及び、高周波モジュールを搭載することで、小型化、低コスト化が可能な無線装置を提供する。

【解決手段】多層基板と前記多層基板の上層部で構成された高周波電力増幅器と前記多層基板の内層の上下2層を用いた方向性結合器と、前記高周波電力増幅器と前記方向性結合器の間にある内層のグランドパターンと、前記内層のグランドパターンと裏面のグランドパターン間に設けられている前記高周波電力増幅器用の多数のサーマルビアが方向性結合器と同じ層にある前記高周波電力増幅器用のバイアスラインとの間に設けられている高周波モジュールとする。このことによって小型、低コスト、高性能な高周波モジュールが実現出来る。

(もっと読む)

通信装置および歪補償方法

【課題】DPD方式の歪補償機能を有する簡易な構成の通信装置および当該通信装置の歪補償方法を提供することである。

【解決手段】サーキュレータ12は、第1、第2、第3の端子を備える、第1の端子は、送信信号処理部201からの送信信号を受け、第2の端子は、送受信アンテナ10からの受信信号を受けるとともに、送受信アンテナ10へ第1の端子から入力された送信信号を出力し、第3の端子は、第2の端子から入力された受信信号を出力し、かつ第1の端子から入力された送信信号が漏れ出した信号をフィードバック信号として出力する。受信信号およびフィードバック信号処理部204は、受信信号に対して増幅を行なう低雑音増幅器26を含むとともに、受信信号およびフィードバック信号に対して無線周波波数帯から中間周波数帯への周波数変換を行なう。フィードバック信号は、さらに歪補償部56に入力される。

(もっと読む)

増幅回路

【課題】回路を簡素化することができる増幅回路を提供することである。

【解決手段】増幅回路100は、PNPトランジスタQ1、Q4と、NPNトランジスタQ2、Q3と、バイアス回路20と、を含む。PNPトランジスタQ1のベース、および、NPNトランジスタQ2のベースには入力信号が入力され、PNPトランジスタQ1のエミッタとNPNトランジスタQ3のエミッタとが接続され、NPNトランジスタQ2のエミッタとPNPトランジスタQ4のエミッタとが接続され、PNPトランジスタQ1のコレクタが第1電位に接続され、NPNトランジスタQ2のコレクタが、第1電位と同一又は異なる第2電位に接続され、NPNトランジスタQ3のコレクタが定電源V1ラインに接続され、PNPトランジスタQ4のコレクタが定電源V2ラインに接続され、バイアス回路20がNPNトランジスタQ3のベースとPNPトランジスタQ4のベースとの間に接続される。

(もっと読む)

電流電圧変換回路

【課題】回路構成を簡素化した電流電圧変換回路を提供することである。

【解決手段】NPNトランジスタQ1のエミッタとPNPトランジスタQ2のエミッタとが入力端子INに接続される。NPNトランジスタQ1のコレクタが定電源V1ラインに接続され、PNPトランジスタQ2のコレクタが電源C2ラインにされる。NPNトランジスタQ1のベースと、PNPトランジスタQ2のベースとの間に、バイアス回路20が接続され、フローティング状態とされる。

(もっと読む)

高周波電力増幅器

【課題】部品の使用点数を減少させて実装面積を縮小すると共に、信号のスイッチ通過による通過損失を抑制する高周波電力増幅器を提供する。

【解決手段】整合回路23,25,26,27と少なくとも1以上の高周波電力増幅素子24とを有する高周波電力増幅器21であって、前記整合回路は2つのリアクタンス素子37,38,39,40が直列に接続された第1の整合ライン41及び第2の整合ライン42が並列に接続された回路と、前記第1の整合ラインの前記リアクタンス素子間及び前記第2の整合ラインの前記リアクタンス素子間とグランドに接続され何れか一方を選択可能なスイッチ43とを有し、該スイッチを切替えることで前記第1の整合ライン及び前記第2の整合ラインの何れか一方に信号を伝搬させ、他方を前記グランドに接続させる。

(もっと読む)

出力スイッチング回路

【課題】アナログ回路の規模をできるだけ小さくした出力スイッチング回路を提供する。

【解決手段】出力スイッチング回路1は,高電源に接続された第1のトランジスタ31と低電源に接続された第2のトランジスタ32とを有し第1,第2のトランジスタ31,32の接続ノードを出力端子33とするスイッチング回路30と,出力端子33の出力信号Voをローパスフィルタ40を介してフィードバックしたフィードバック信号FBと,入力信号Inとを比較し,比較信号Vcompを生成する比較ユニット10と,比較信号Vcompに応じて第1,第2のトランジスタ31,32を駆動する第1,第2の駆動パルスVp,Vnを生成する駆動パルス生成ユニット20とを有する。

(もっと読む)

オーブン制御用の積分回路

【課題】 抵抗器の抵抗値、コンデンサの容量に制約されず、積分時間を長くすることができ、更に、当該積分時間を任意に変更できる積分回路を提供する。

【解決手段】 抵抗1、コンデンサ2、オペアンプ3を備える積分器を備え、入力段にクロックのハイ/ローでオン/オフするアナログスイッチ5と、当該クロックを発生させるクロック発生回路4と、クロックの周期Tとハイ部分の長さT1を制御する制御回路6とを設け、抵抗器1を介してオペアンプ3に入力される入力信号をクロックがハイ部分でのみ入力し、クロックの周期Tとハイ部分の長さT1を制御回路6で制御可能としたOCXOのオーブン制御用の積分回路である。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止することにより、規格値を超過するドレイン電流を発生することを回避できる接合形電界効果トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面にイオン注入によりn型不純物層を設け、p+型半導体基板とpn接合を形成して接合容量をハイパスフィルタ5の容量4とする。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止し規格値を超過するドレイン電流が発生することを回避できる増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量4を付加し、当該容量4とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタを構成する。ハイパスフィルタの遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面に絶縁層を設けてこれを誘電体とし、導電部材と基板とで平行平板型の容量4を接続する。

(もっと読む)

増幅回路装置

【課題】J−FETを増幅回路装置として採用する場合に、意図しない低周波信号の入力を防止し、規格値を超過するドレイン電流が発することを回避する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FETのゲート−ソース間に接続される抵抗とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。n型半導体基板上にバックゲート領域となるp型半導体層を設けてpn接合を形成し、この接合容量をハイパスフィルタ5の容量とする。

(もっと読む)

81 - 100 / 661

[ Back to top ]