Fターム[5J500AH02]の内容

Fターム[5J500AH02]の下位に属するFターム

ラテラルトランジスタ (2)

マルチエミッタトランジスタ (4)

マルチコレクタトランジスタ (1)

HBT(ヘテロジャンクションBi−Tr) (105)

構造や閾値 (7)

nPnトランジスタとPnPトランジスタの組合せ (173)

Fターム[5J500AH02]に分類される特許

161 - 180 / 1,082

電力増幅回路

【課題】電源の供給が停止された際に安定に立ち下がる電力増幅回路を提供する。

【解決手段】電力増幅回路は、入力信号を増幅する増幅回路と、増幅回路を駆動するためのバイアス電流を生成するバイアス電流回路と、電源電圧が所定レベルよりも低くなると、増幅回路が発振することを防ぐべくバイアス電流回路にバイアス電流の生成を停止させる制御回路と、を備える。

(もっと読む)

半導体集積回路装置および電力増幅器

【課題】電力増幅を行う増幅回路のレイアウト面積を低減させながら、トランジスタの熱暴走などを防止し、動作を安定化させる。

【解決手段】パワー段増幅回路4では、ユニットセル81〜8Nに、ベースバラスト抵抗Rb1〜RbNに付加するバイアス回路となるトランジスタQ21〜Q2Nをそれぞれ設けた構成とする。この場合、コントロール電源電圧Vregとトランジスタのエミッタ電圧Ve31の間の電位差は、ベース−エミッタ間電圧Vbeと抵抗Rb1の電圧降下に加えて、トランジスタQ21のベース−エミッタ間電圧Veb31の3つにより支えられ、ベース電流Ib1の増大に伴って、ベース−エミッタ間電圧Vbe31も大きくなり、熱暴走の開始を遅らせることができ、熱暴走の開始電流Icritを増大させることができる。

(もっと読む)

電力増幅器

【課題】多段接続される増幅器からのバイアス電流の逆流に起因するバイアス変動を効果的に抑制し、安定して信号増幅できる電力増幅器を提案する。

【解決手段】電力増幅器11は、多段接続されるトランジスタTr1,Tr2,Tr3を備え、これらのトランジスタTr1,Tr2,Tr3は、トランジスタTr1,Tr2を含む第一のグループと、最終段のトランジスタTr3を含む第二のグループとにグループ分けされる。バイアス回路31は、第一のグループに属するトランジスタTr1,Tr2にバイアス電流Ib1,Ib2を分岐供給する。バイアス回路32は、第二のグループに属するトランジスタTr3にバイアス電流Ib3を供給する。

(もっと読む)

差動増幅器およびその制御方法

【課題】高スルーレートの差動増幅器を提供する。

【解決手段】差動増幅器は、差動入力信号を受ける差動対トランジスタ(TN12/TN13、TP12/TP13)と、定電流源(ICS11、ICS12)と、スイッチ(TN11、TP11)とを具備する。定電流源(ICS11、ICS12)は、差動対トランジスタ(TN12/TN13、TP12/TP13)に流れる電流を制御する。スイッチ(TN11、TP11)は、定電流源(ICS11、ICS12)と並列に配置され、差動入力信号の反転動作に同期して差動入力信号の反転動作の遷移時間より短い時間だけ差動対トランジスタTN12/TN13、TP12/TP13)に流れる電流を増加する。

(もっと読む)

光受信器

【課題】帰還抵抗を極端に大きくすることなく、高感度に広帯域な動作を実現できる光受信器を提供する。

【解決手段】同一極性方向に直列接続された2個の受光素子より構成されたバランスドフォトダイオードと、このバランスドフォトダイオードの出力信号が入力されるチェリーホッパー型増幅部と、このチェリーホッパー型増幅部を構成している差動入力ペアトランジスタからのそれぞれの出力信号をレベルシフトするエミッタフォロワ部と、このエミッタフォロワ部の出力信号を前記チェリーホッパー型増幅部の各入力端子に帰還する経路に設けられた第1および第2の帰還抵抗と、この第2の帰還抵抗と前記チェリーホッパー型増幅部を構成している差動増幅回路の一方のトランジスタのベースに接続されている第1のコンデンサとを有することを特徴とする。

(もっと読む)

高周波電力増幅器

【課題】バイアス制御部を比較的簡素化し、且つ多段接続された各半導体増幅素子に対して所望のバイアス電圧を設定する。

【解決手段】高周波電力増幅器1は、バイアス制御部10と電力増幅部20とを備える。電力増幅部20は半導体増幅素子211,212,213が多段接続されてなり、高周波信号を増幅して出力する。バイアス制御部10では、バッファアンプ111を介したバイアス制御用信号が定抵抗器131、可変抵抗部132,133へ供給される。可変抵抗部132,133はレジスタ130のスイッチ制御信号より抵抗値が可変でき、所定の抵抗値に設定される。バイアス制御信号に基づき、定抵抗器131はバイアス電圧Vbias1を半導体増幅素子211へ供給し、可変抵抗部132はバイアス電圧Vbias2を半導体増幅素子212へ供給し、可変抵抗部133はバイアス電圧Vbias3を半導体増幅素子213へ供給する。

(もっと読む)

電流電圧変換回路、光学機器、及び光学ドライブ装置

【課題】ゲインを大きくする場合のノイズの増加及び狭帯域化を抑制する。

【解決手段】電流電圧変換回路は、フォトダイオード1から出力される電流信号を増幅する第1の差動増幅回路10と、第1の差動増幅回路10の出力信号を増幅する第2の差動増幅回路20と、第2の差動増幅回路20の出力信号が入力される反転入力端子を有するオペアンプ30と、オペアンプ30の反転入力端子と出力端子の間に接続された帰還抵抗31とを備える。

(もっと読む)

発振回路

【課題】 クロック発振回路のジッタが音質に重要だとは気が付かなかったか、CMOSの発振回路のジッタ性能で十分だと思われていた。しかし、ジッタが多いと、音質的に十分でないことが判明した。そこで、高音質化のため低ジッタ化し、なおかつ高周波化、低電圧化、波形のエッジの急峻さ、波形の対称性を達成する必要性がある。

【解決手段】 CMOSよりもノイズ特性に優れるバイポーラトランジスタを使い、これをコンプリメンタリ接続にすることで、低ジッタ、高周波化、低電圧化、波形のエッジの急峻さ、高い対象性を得ることができた。

(もっと読む)

演算増幅器

【課題】極力小さな入力端子間電位差で、スルーレートを増大可能とする。

【解決手段】差動接続された第1及び第2のトランジスタ11,12の差動接続部分に第1の定電流源3が接続される一方、第1及び第2のトランジスタ11,12の差動接続部分と反対側に、カレントミラーを構成する第3及び第4のトランジスタ13,14が接続される一方、第1のトランジスタ11とダーリントン接続される第5のトランジスタ15が設けられると共に、そのダーリントン接続に電流供給可能に第2の定電流源4が設けられ、第2のトランジスタ12とダーリントン接続される第6のトランジスタ16が設けられると共に、そのダーリントン接続に電流供給可能に第3の定電流源5が設けられ、さらに、第5のトランジスタ15と差動対をなす電流補償用トランジスタ17が設けられ、その入力及び出力は、第2のトランジスタ12と同一に接続されてなるものである。

(もっと読む)

利得可変回路

【課題】飽和に強い差動形式の利得可変回路を提供すること。

【解決手段】利得可変回路は、差動増幅回路部Aと、バイアス回路部Bと、コントロール回路部Cと、で構成されている。差動増幅回路部Aは、トランジスタTr1、Tr2を用いた初段の差動増幅回路と、トランジスタTr3、Tr4を用いた次段の差動増幅回路との2段増幅回路である。コントロール回路部Cの入力端子Vcontに制御電圧が印加されない場合は、バイアス回路部BによってトランジスタTr1、Tr2がバイアスされて活性領域で動作し、通常の増幅動作を行う状態となる。入力端子Vcontに制御電圧が印加された場合は、通常の増幅動作状態に比べてベース電流は増加するが、コレクタ電流は一定のため、コレクタ−エミッタ間電圧は低下する。その結果、トランジスタTr1、Tr2は飽和領域で動作し、利得が低下する。

(もっと読む)

高周波増幅器

【課題】分配器を用いずに入力信号を分配して小型化を実現した高周波増幅器を得る。

【解決手段】入力端子3に接続されたノードNと、出力端子4に接続された出力整合回路8と、ノードNと出力整合回路8との間に並列接続された第1および第2の分岐線路と、第1の分岐線路に挿入されて入力端子3からの入力信号を増幅するキャリア電力増幅器1と、第2の分岐線路に挿入されて入力信号のピーク成分を増幅するピーク電力増幅器2と、キャリア電力増幅器1の入力側に挿入された第1の入力整合回路と、ピーク電力増幅器2の入力側に挿入された第2の入力整合回路とを備え、キャリア電力増幅器1およびピーク電力増幅器2の合成出力信号を出力端子4から出力する。第1の入力整合回路は、LPF型回路5により構成され、第2の入力整合回路は、λ/4電気長の伝送線路6およびLPF型回路7からなる直列回路により構成されている。

(もっと読む)

電気機器

【課題】音声出力回路による音声出力をミュートする音声ミュート回路を備えた電気機器において、音声出力回路への電源供給停止時のポップ音の発生を防止し、かつ、音声ミュート回路の構成を小型で安価なものとする。

【解決手段】音声ミュート回路5は、音声出力回路である音声ICへの電源供給の停止を検出する検出回路51と、その検出結果に基づき、音声ICのミュート端子31にミュート信号を入力する入力回路52とを備える。検出回路51は音声ICへの電源供給停止時に非導通状態となるフォトカプラ53で構成され、その非導通時に入力回路52がミュート信号を出力する。これにより、音声ICへの電源供給停止後に音声出力回路が動作し続けたとしても、音声ICによる音声出力をミュートさせて、ポップ音の発生を防止することができる。また、フォトカプラは小さく、かつ、安いので、音声ミュート回路5の構成を小型で安価なものとすることができる。

(もっと読む)

電力増幅器及びその製造方法

【課題】低耐圧のトランジスタを用いた高出力の電力増幅器を提供すること。

【解決手段】本発明に係る電力増幅器は、制御端子に第1の入力信号が入力される第1のトランジスタ6と、第1のトランジスタ6と縦列接続され、制御端子に第2の入力信号が入力される第2のトランジスタ10とを備え、第1の入力信号と第2の入力信号とが、同期し、かつ、同位相であるものである。これにより、出力電圧が、最大電圧振幅時に、第1のトランジスタ6と第2のトランジスタ10とに略均等に分割して印加される。

(もっと読む)

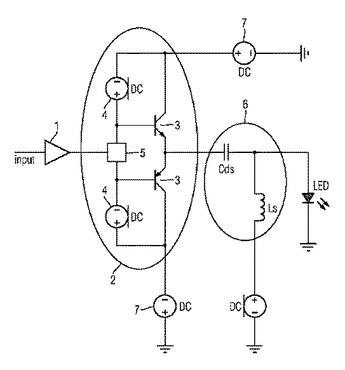

高い出力性能とコンパクトな構造を有する広帯域高線形性LED増幅器

本発明は、発光ダイオードを駆動制御する増幅回路に関する。この増幅回路は、約3オームの小さい出力インピーダンスと、200KHzの下方境界周波数と例えば5MHzの上方境界周波数とを備えた広い帯域幅と、例えば数100mAの出力電流振幅とを有する。この増幅回路は、直流電流供給部(6)によって発光ダイオードを駆動制御するドライバー回路(2)を駆動制御する入力段を有している、という特徴を有している。  (もっと読む)

(もっと読む)

音声出力装置、及び表示装置

【課題】音声信号を減衰させる音声出力装置において、スタンバイ期間における消費電力を低減することが可能な音声出力装置を提供する。

【解決手段】音声信号を減衰させてミュート処理を行なう音声出力装置において、入力されるベース電流の値に応じて減衰量を設定する減衰回路と、当該音声出力装置を駆動するための電源を供給するとともに、スタンバイ期間に電源の供給量を低下させる電源部と、前記電源部が供給する電源の供給量に応じて、ベース電流の値を設定し、前記減衰回路に前記設定されたベース電流を供給するベース電流設定回路と、を有する。

(もっと読む)

トランスインピーダンスアンプ

【課題】高速信号を処理するトランスインピーダンスアンプの消費電流を低減すること。

【解決手段】差動増幅回路9と、メインTIAコア5及びダミーTIAコア7とを有する。メインTIAコア5は、受光素子1からの電流信号を電圧信号に変換して差動増幅回路9に出力し、ダミーTIAコア7は、基準信号を差動増幅回路9に出力する。ダミーTIAコア7の出力インピーダンスの絶対値は、低周波側では、メインTIAコア5の出力インピーダンスの絶対値よりも高く、高周波側では、メインTIAコア5の出力インピーダンスの絶対値と同様となる。

(もっと読む)

H級共鳴電気外科手術発電機

【課題】電気外科手術デバイスと共に使用する発電機を提供すること。

【解決手段】第一の電圧レールと第二の電圧レールとの間に電気的に配置された利得ステージと、利得ステージの入力に動作可能に結合された電圧供給源と、増幅器の動作パラメータを感知することと、動作パラメータに対応するセンサ信号を提供することとを行うように構成された少なくとも1つのセンサと、少なくとも1つのセンサ信号を受信することと、その信号に応答して、駆動制御信号を電圧供給源に提供することとを行うように適合されたコントローラと、利得ステージの出力が第一の電圧レールの電圧と第二の電圧レールの電圧との間に入るとき、対応する出力電圧を供給するように構成され、出力電圧が第一の電圧レールの電圧より大きいか、または第二の電圧レールの電圧より小さいときには、ピーク電圧出力を供給するように構成される、増幅器出力とを備えている、発電機。

(もっと読む)

出力駆動回路

【課題】出力信号が不安定になる可能性があった。

【解決手段】第1、第2の電源間に直列接続される第1、第2のトランジスタを備えた出力部と、入力パルス信号に応じて、前記第1のトランジスタがオン状態となるとき、前記第1の電源端子と前記第1のトランジスタの制御端子を導通させオン状態に駆動させる第1の駆動部と、一端が第1のノードとの間に接続されるインダクタと、前記第1のスイッチング素子の少なくともオフ後にオン状態となることで、前記第1のノードと前記第1のトランジスタの制御端子を導通し、前記第1の所定の期間後に前記第1のノードに供給される前記インダクタの逆起電力を、前記第1のトランジスタの制御端子に伝達する第2のスイッチング素子と、を有する出力駆動回路。

(もっと読む)

検波回路、及び、高周波回路

【課題】検波回路における検波特性の温度依存性を抑制する。

【解決手段】バイアス抵抗5、及び/又は、負荷抵抗6を、温度係数の大きい抵抗体により構成することによって、ダイオード検波回路3に含まれる検波ダイオードの温度変化に伴う検波出力のシフトを、バイアス抵抗5の温度変化に伴う検波出力のシフト、及び/又は、負荷抵抗6の温度変化に伴う検波出力のシフトによりキャンセルする。

(もっと読む)

入力信号の電力増幅用回路及びそのような回路を組み込んでいる信号発信システム

【課題】 入力信号の電力増幅用回路及びそのような回路を組み込んでいる信号発信システムを提供する。

【解決手段】 本発明は、入力段(EE)及び出力段(ES)を含む入力信号の電力増幅用回路(CIR)に関し、前記入力段(EE)は:

―いわゆる主駆動トランジスタ(T3)を組み込んでいる駆動手段(MP)と、

―入力信号を受信可能で、主駆動トランジスタ(T3)と共に電流ミラーとして組み立てられた、第1のいわゆる主入力トランジスタ(T1)とを備える。

第1の主入力トランジスタ(T1)は、入力段(EE)内へ組み込まれた第2のいわゆる主入力トランジスタ(T2)を介して出力段(ES)に連結され、かつ駆動手段(MP)によって制御され、第1の主入力トランジスタ(T1)と第2の主入力トランジスタ(T2)は相互に連結され、かつ共振回路(BB2,Cp)を経由してDarlington型の構造に従ってアースに連結される。

(もっと読む)

161 - 180 / 1,082

[ Back to top ]