Fターム[5J500AH10]の内容

増幅器一般 (93,357) | 回路素子 (16,323) | 半導体素子 (6,058) | FET (3,573) | MOSFET、MISFET(絶縁ゲート形電界効果トランジスタ) (1,872)

Fターム[5J500AH10]に分類される特許

121 - 140 / 1,872

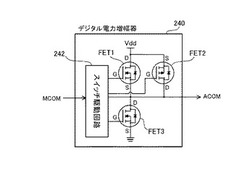

容量性負荷駆動回路および流体噴射装置

【課題】変調信号のオンデューティー比が上限付近の状態が継続しても、D級増幅器を正

常に動作させて駆動信号を出力が可能とする。

【解決手段】駆動波形信号から生成した変調信号を電力増幅した後、平滑化することによ

って駆動信号を生成する。変調信号を電力増幅するデジタル電力増幅器では、電源とグラ

ンドとの間で2つのNチャンネル(以下ch)MOSFETをプッシュ・プル接続し、更

に、電源側のNchMOSFETに対して並列にPchMOSFETを接続する。こうす

れば、電源側のNchMOSFETをONにするためのブートストラップコンデンサーに

蓄えられた電荷が不足してNchMOSFETをONにすることができない場合でも、P

chMOSFETをONにすることで電力増幅を行うことができ、駆動信号を出力するこ

とが可能となる。

(もっと読む)

差動増幅回路

【課題】チップ面積を小さくする。

【解決手段】一端がグランド端子14に接続される定電流源13と、ソースが共通に定電流源13の他端に接続され、ゲートが入力端子A、Bにそれぞれ接続される第1および第2の差動対(Q11、Q12およびQ13、Q14に相当)と、第1の差動対のそれぞれのドレインにそれぞれのソースを接続するnMOSトランジスタQ15、Q16と、nMOSトランジスタQ15、Q16のそれぞれのドレインを出力端子C、Dとし、出力端子C、Dと電源端子11との間に接続される負荷部(図1のQ17、Q18に相当)と、を備え、第1の差動対のそれぞれのドレインを第2の差動対の逆相となるそれぞれのドレインに接続し、nMOSトランジスタQ15、Q16のそれぞれのゲートは、nMOSトランジスタQ15、Q16のドレインにそれぞれ接続する。

(もっと読む)

傾斜増幅器システム

【課題】電力損失を低減するような傾斜増幅器システムの設計を提供する。

【解決手段】傾斜増幅器システムは、その各々が第1の切替え周波数で動作する複数のブリッジ増幅器を有する電力段と、電力段の出力端子に結合され、電力段により供給されるコイル電流信号に比例した磁場を発生する傾斜コイルと、電力段の入力端子に結合され、コイル電流信号及び基準電流信号に基づいてパルス幅変調ゲート信号を生成する制御器段とを含んでおり、基準電流信号に関連付けされたスルーレートが決定されたしきい値レート未満であること並びに基準電流信号に関連付けされた振幅レベルが決定されたレベルを超えることの発生時にパルス幅変調ゲート信号は第2の切替え周波数で生成される。制御器段は、複数のブリッジ増幅器の各々の動作周波数を第1の切替え周波数から第2の切替え周波数に変更するために、発生させたパルス幅変調ゲート信号を電力段に加える。

(もっと読む)

電力増幅器および通信装置

【課題】 温度変動や製造ばらつきに伴う利得変動を抑制する。

【解決手段】 電力増幅器は、信号を増幅する複数の増幅部が多段接続された増幅回路と、各増幅部にバイアス電圧を供給するバイアス供給回路とを有し、バイアス供給回路は、増幅部のトランスコンダクタンスを安定させるための第1モードでバイアス電圧を制御する第1バイアス回路と、増幅部のバイアス電流を安定させるための第2モードでバイアス電圧を制御する第2バイアス回路とを有し、複数の増幅部の少なくとも1つの増幅部のバイアス電圧は、第1モードで制御可能であり、複数の増幅部の残りの少なくとも1つの増幅部のバイアス電圧は、第2モードで制御可能である。

(もっと読む)

定電流生成回路及びこれを含むマイクロプロセッサ

【課題】従来の定電流生成回路は、定電流の温度変動に対する変動率を十分に抑制できない問題があった。

【解決手段】本発明の定電流生成回路は、温度に対して電圧値が変動する第1の変動電圧Vfを生成する温度変動電圧生成部10と、温度に対して第1の変動電圧Vfよりも変動量が小さな基準電圧Vconstと、第1の変動電圧Vfとに基づき第2の変動電圧Vrefcを生成する変動傾き調整部12と、温度に対して抵抗値が変動する電流設定抵抗Riを含み、第2の変動電圧Vrefcと電流設定抵抗Riとに基づき出力電流を生成する電流生成部13と、を有し、変動傾き調整部12は、第2の変動電圧Vrefcの温度に対する変動率を、温度に対する電流設定抵抗Riの抵抗値の変動率との差が予め設定された第1の規定範囲内になるように設定する。

(もっと読む)

定電圧回路及び増幅回路

【課題】ゲート容量が大きなトランジスタを有する増幅器に接続しても発振を防止できる定電圧回路及び増幅回路を提供する。

【解決手段】定電圧回路40は、所定の電圧が印加される第1の入力端子44と、出力端子46に接続された第2の入力端子とを備えた差動増幅部41と、ソースが接地され、ドレインが出力端子46に接続され、ゲートに差動増幅部41の出力が与えられるトランジスタT46を備えたソース接地型増幅器42とを有する。そして、トランジスタT46のゲートとドレインとの間には、抵抗47とコンデンサ48とが直列に接続されている。定電圧回路40から出力される電圧Vgは、増幅器20のバイアス端子26bからバイアス給電用インダクタ25a,25bを介してトランジスタT3,T4に供給される。

(もっと読む)

固定音発生装置及びスイッチング増幅器

【課題】電源投入直後にビープ音や警告音などのような固定音をスピーカで鳴らす際に電力消費を減少させることができ、また、異音を防止することができる固定音発生装置及びスイッチング増幅器を提供する。

【解決手段】オーディオ装置11の内蔵マイコン12から、オーディオ装置の操作時に操作者に操作状態を知らせるためにビープ音などのような固定音を発生させる指令信号S1が固定音制御部2に入力されると、固定音制御部及び固定音生成部4は固定音生成信号S8を生成し、電圧可変電源部6は信号S8の電圧成分を電力増幅段8の電源電圧に付加し、PWM変調部3は、オーディオ信号の出力期間でオーディオ信号の値に応じたパルス幅のPWM変調信号S4を生成するとともに、固定音発生期間で所定のパルス幅のPWM変調信号を生成し、電力増幅段8は、電源電圧をPWM変調信号でスイッチングすることによりオーディオ信号及び/又は固定音を電力増幅する。

(もっと読む)

差動増幅器及びアナログ/デジタル変換器

【課題】スイッチに流れるオフリーク電流の影響を抑制し、利得の発振を抑える。

【解決手段】差動増幅器16は、入力信号が入力される入力端子27,28と、前記入力信号が増幅された出力信号を出力する出力端子25,26と、を備える差動増幅器16であって、前記入力信号を増幅し前記出力信号を生成する増幅部21と、前記増幅部21と電源端子との間に接続され、第1導電型トランジスタT34,T35と、前記第1導電型トランジスタT34,T35のゲート端子をドレイン端子に接続するかまたは前記出力端子25,26に接続するかを切り替える切り替えスイッチ22と、を有する負荷回路23と、前記切り替えスイッチ22のオフリーク電流を低減するキャンセル電流を生成するリークキャンセルスイッチ30と、を備える。

(もっと読む)

増幅回路

【課題】動作電流を減少させることが可能となり、低消費電力化が可能となる増幅回路の提供。

【解決手段】この発明は、差動対を構成し、互いに逆相の差動入力信号vipx、vinxが入力されるMOSトランジスM1、M2と、MOSトランジスタM1、M2のそれぞれの負荷となるMOSトランジスタM3、M4とを備えている。また、MOSトランジスタM3のバルクには、抵抗R5を介してバイアス電圧が印加されるととともに、キャパシタC3を介して反転出力信号vonが入力される。さらに、MOSトランジスタM4のバルクには、抵抗R6を介してバイアス電圧が印加されるととともに、キャパシタC4を介して出力信号vopが入力される。

(もっと読む)

半導体集積回路および受信装置

【課題】低コストかつノイズの影響を受けにくい半導体集積回路およびこれを用いた受信装置を提供する。

【解決手段】実施形態によれば、半導体集積回路は、トランスコンダクタンス回路と、第1の負荷回路と、第2の負荷回路とを備える。前記トランスコンダクタンス回路、前記第1の負荷回路および前記第2の負荷回路の少なくとも1つは、下式のパラメータPが低減されるようにインピーダンスを調整するインピーダンス調整部を有する。P=Z01*Z04−Z02*Z03。ここで、Z01は前記第1の出力端子から見た前記トランスコンダクタンス回路のインピーダンス、Z02は前記第2の出力端子から見た前記トランスコンダクタンス回路のインピーダンス、Z03は前記第1の負荷回路のインピーダンス、Z04は前記第2の負荷回路のインピーダンス。

(もっと読む)

差動増幅回路及び集積回路装置

【課題】差動対を構成する2つのPMOSトランジスターにおけるNBTIの発生を可能な限り防ぐことにより出力オフセット電圧の発生を抑制可能な差動増幅回路及び集積回路装置を提供すること。

【解決手段】差動増幅回路1は、第1の信号が入力されるPMOSトランジスター10(第1のPMOSトランジスターの一例)と、第2の信号が入力されるPMOSトランジスター20(第2のPMOSトランジスターの一例)と、制御信号XSTBに基づいて、PMOSトランジスター10のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター14(第1のスイッチ部の一例)と、制御信号XSTBに基づいて、PMOSトランジスター20のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター24(第2のスイッチ部の一例)と、を含む。

(もっと読む)

差動増幅器

【課題】差動増幅回路、カレントミラー回路およびレール・トゥ・レール回路を組み合わせた電気回路において、外部からの信号に応じて容量の充放電を高速化する機能を維持しつつ、容量の充放電に寄与しない無駄な電流を減少させた差動増幅器を提供する。

【解決手段】外部からの信号に基づくデジタル信号を生成する論理回路を内蔵するスイッチ制御回路を設けて、容量の充放電を高速化するスイッチをこのデジタル信号を用いて制御する。

(もっと読む)

トランスコンダクタンス調整回路、回路装置及び電子機器

【課題】トランスコンダクタンスを精度良く調整することができるトランスコンダクタンス調整回路、回路装置及び電子機器等を提供すること。

【解決手段】トランスコンダクタンス調整回路100は、第1の信号I及び第1の信号Iと位相が90度異なる第2の信号Qが入力され、第1、第2の抵抗素子RA1と、第1、第2のキャパシターCA1、CA2と、演算トランスコンダクタンス増幅器で構成される中心周波数シフト回路110と、トランスコンダクタンス調整信号AGMを出力する調整信号生成回路120とを含む。調整信号生成回路120は、第2の信号Qと第1の出力信号OIとに基づいて、又は第1の信号Iと第2の出力信号OQとに基づいて、又は第1の信号Iと第1の出力信号OIとに基づいて、又は第2の信号Qと第2の出力信号OQとに基づいて、トランスコンダクタンス調整信号AGMを生成する。

(もっと読む)

定電流回路

【課題】面積の小さい定電流回路を提供する。

【解決手段】高い抵抗値の抵抗によらず、強反転領域の非飽和領域で動作するNMOSトランジスタ13の高い抵抗値のオン抵抗により、定電流回路の定電流IREFが少なくなる。NMOSトランジスタ13の面積はこのトランジスタのオン抵抗の抵抗値と同じ抵抗値の抵抗の面積よりも小さいので、定電流回路の面積が小さくなる。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

C級増幅器

【課題】高効率でかつ広帯域化されたC級増幅器を提供する。

【解決手段】本実施の形態に係るC級増幅器は、電源電圧がVdc、最大電流がImaxの増幅素子の流通角θoがπ(rad)未満において、前記増幅素子の等価回路の従属電流源から見た基本波の負荷インピーダンスをZ1=R1+j・X1、2倍波の負荷インピーダンスをZ2=R2+j・X2とし、X1とR1の関係を−R1≦X1≦R1、R1をR1=Vdc/Imax・π・{1−cos(θo/2)}/{θo/2−sin(θo)/2}、X2/X1をX2/X1=−{θo/2−sin(θo)/2}/{sin(θo/2)−sin(1.5・θo)/3}に、あるいはそれぞれの近傍にする。

(もっと読む)

カレントミラー回路およびそれを用いた半導体装置

【課題】プロセス変動があった場合でも広い出力電圧範囲が得られるカレントミラー回路を提供する。

【解決手段】この低電圧カスコードカレントミラー回路は、NチャネルMOSトランジスタQ1〜Q5と抵抗素子1を備える。トランジスタQ3のオーバードライブ電圧Vov_Q3は、トランジスタQ4,Q5のオーバードライブ電圧Vov_Q4,Vov_Q5の和に等しい。定電流Icと抵抗素子1の抵抗値R1との積は、トランジスタQ5の飽和マージンVdsm_Q5となる。したがって、プロセス変動があった場合でも、トランジスタQ5の飽和マージンVdsm_Q5は変化しない。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

定電流回路

【課題】 電流値のバラツキの小さい定電流回路を提供する。

【解決手段】 Pチャネルトランジスタ3および9は、互いに比例した定電流を出力する第1および第2の定電流源として機能する。キャパシタ5は、Pチャネルトランジスタ3に直列接続されている。放電用スイッチであるNチャネルトランジスタ6は、周期的にキャパシタ5の充電電荷を放電させる。コンパレータ7は、キャパシタ5の充電電圧V1が基準電圧Va以内である期間だけPチャネルトランジスタ4および10をONにすることにより第1および第2の定電流源による電流の出力を行わせる。キャパシタ11、抵抗12およびキャパシタ13からなる平滑化回路19は、第2の定電流源の出力電流を平滑化する。Nチャネルトランジスタ14および15からなる出力用カレントミラーは、この平滑化回路19により平滑化された電流に比例した電流を出力する。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

121 - 140 / 1,872

[ Back to top ]