Fターム[5J500AH10]の内容

増幅器一般 (93,357) | 回路素子 (16,323) | 半導体素子 (6,058) | FET (3,573) | MOSFET、MISFET(絶縁ゲート形電界効果トランジスタ) (1,872)

Fターム[5J500AH10]に分類される特許

41 - 60 / 1,872

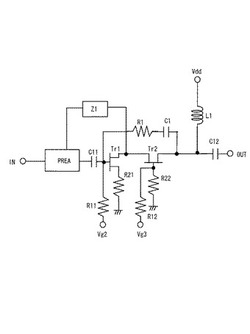

増幅器

【課題】歪の発生を少なくする。

【解決手段】入力信号(IN)を受ける初段増幅回路(PREA)と、ゲートに初段増幅回路(PREA)の出力信号を受けるソース接地の第1のトランジスタ(Tr1)と、ソースを第1のトランジスタ(Tr1)のドレインに接続し、ドレインから出力信号(OUT)を送出すると共にドレインに対して電源供給がなされるゲート接地の第2のトランジスタ(Tr2)と、初段増幅回路(PREA)の電源端と第2のトランジスタ(Tr2)のソースとの間に介在する第1のインピーダンス回路(Z1)と、を備える。第1のインピーダンス回路(Z1)は、直流を通過させると共に、所定の周波数帯域において所定のインピーダンス以上となるように構成された回路である。

(もっと読む)

電流電圧変換回路

【課題】回路全体の耐圧を高めることができ、入力側に高い電圧が印加される場合であっても素子破壊を効果的に防止し、正常に動作させ得る電流電圧変換回路を提供する。

【解決手段】電流電圧変換回路1は、検出抵抗10を流れる電流に応じた信号であって且つ抵抗11及び抵抗12の抵抗値に応じた電圧信号を出力するように構成されている。この回路では、第3トランジスタTra1と第4トランジスタTrb1とが対をなし、第3トランジスタTra2と第4トランジスタTrb2とが対をなしている。そして、駆動電圧生成部20は、これら複数のトランジスタ対における各第3トランジスタと各第4トランジスタとの各共通接続部に対し、検出抵抗10の高電位側よりも低くグランドよりも高い駆動電圧を、グランド側のトランジスタ対となるにつれて印加電圧が低くなるように段階的に印加している。

(もっと読む)

RFパワーモジュール

【課題】多段増幅段を含むRF電力増幅回路の低パワーおよび中間パワー時における電力付加効率(PAE)の低下を軽減する。

【解決手段】RF電力増幅回路313は、前段増幅器310、後段増幅器311、制御部312を具備する。前段増幅器310はRF送信入力信号Pinに応答して、前段増幅器310の出力の増幅信号に後段増幅器311が応答する。制御部312は、出力電力制御電圧Vapcに応答して、前段増幅器310と前記後段増幅器311のアイドリング電流を制御して前段増幅器310と前記後段増幅器311の利得を制御する。出力電力制御電圧Vapcに応答して、前段増幅器310のアイドリング電流と利得とは第1の連続関数2ndAmpに従って連続的に変化して、後段増幅器311のアイドリング電流と利得とは第2の連続関数3rdAmpに従って連続的に変化する。第2の連続関数3rdAmpは、第1の連続関数2ndAmpよりも1次以上高次の関数である。

(もっと読む)

差動増幅器

【課題】出力電圧の出力精度に段差が発生していた。

【解決手段】電流源で駆動される第1、第2の差動対と、その電流源を駆動する第1の基準電流発生回路と、を備える第1の差動入力部と、電流源で駆動される第3、第4の差動対と、その電流源を駆動する第2の基準電流発生回路と、を備える第2の差動入力部と、前記第1、第2の差動入力部との出力に応じて、出力する出力部と、を有し、前記第1、第2の基準電流発生回路の第1、第2の電流経路上に接続される第1、第2のトランジスタを入力信号に応じて制御することで、前記第1、第2の差動入力部の出力を制御する差動増幅器。

(もっと読む)

電源回路、電源回路の信号切替方法、帯電装置、画像形成装置

【課題】負荷の増加に伴い、駆動用ドライバをICの外付け素子として用いる場合でも、専用ICを新たに作成するまたは駆動用ドライバに対するプリドライバおよび端子を別途設けることなく、ICと出力端子を共用することで設計およびチップ製作にかかるコストを低減する。

【解決手段】入力信号2,3を切替選択信号22によって切り替え、出力信号13〜16を出力する信号切替ブロック12と、出力信号13〜16をそれぞれチャンネルの異なるスイッチング素子に入力する複数のD級アンプと、を備え、信号切替ブロック12は、複数のD級アンプを、負荷を駆動するための駆動用ドライバ、または外付けされた駆動用ドライバ回路に対するプリドライバとするかを前記切替選択信号により切り替える。

(もっと読む)

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

【課題】差動入力を有する直交出力低雑音トランスコンダクタンス増幅器を提供する。

【解決手段】低雑音トランスコンダクタンス増幅器200は、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部110と、PMOSトランスコンダクタンス部に結合されたPMOSカスコード部130と、RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部120と、NMOSトランスコンダクタンス部に結合されたNMOSカスコード部140と、を含み、PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号gmpq、gmnq及び差動同相出力信号gmpi、gmniを提供する。RF信号を増幅するための方法は、差動RF入力信号を受信することと、差動RF入力信号を電流信号に変換することと、電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供する。

(もっと読む)

受光回路

【課題】受光回路の消費電流を削減する。

【解決手段】一つの実施形態によれば、受光回路は、トランスインピーダンスアンプと出力回路が設けられる。トランスインピーダンスアンプは、フォトダイオード、帰還抵抗、及び第1のトランジスタが設けられる。フォトダイオードは、光信号を電気信号に変換する。帰還抵抗は、フォトダイオードと内部出力端子の間に設けられる。第1のトランジスタは、ゲートにフォトダイオードで光電変換された電気信号が入力され、ドレインが内部出力端子に接続される。出力回路は、第1のトランジスタと同一チャネル型であり、ゲートが内部出力端子に接続され、電流源負荷が接続されるとともにドレイン側から出力信号を出力する第2のトランジスタを含む。

(もっと読む)

RF電力増幅器およびその動作方法

【課題】ランプアップまたはランプダウンにおいてスイッチングスペクトラムの劣化を軽減すること。

【解決手段】初段と最終段のバイアス回路81、83が、初段と最終段の増幅回路41、43のアイドリング電流を決定する。電力検出回路5、6は、最終段出力信号Poutの信号レベルに応答する電力検出信号VDETを生成する。誤差増幅器7に検出信号VDETと目標電力信号VRAMPが供給され、電力制御電圧VAPCが制御信号増強回路9の入力に供給され、出力から増強制御信号VENを生成する。制御信号増強回路9は、所定の非線型の入出力特性を有する。増強制御信号VENが初段と最終段のバイアス回路81、83とに供給され、初段と最終段の増幅回路41、43のアイドリング電流は増強制御信号VENによって制御され、RF電力増幅器の制御利得の低下が補償される。

(もっと読む)

トランスインピーダンスアンプおよび受光回路

【課題】出力電圧範囲を広げることが容易なトランスインピーダンスアンプおよび受光回路を提供する。

【解決手段】第1のMOSトランジスタと、カレントミラー回路と、第2のMOSトランジスタと、負荷と、第1帰還抵抗と、を有する。前記第1のMOSトランジスタは、フォトダイオードが接続されるゲート端子を有する。前記カレントミラー回路には、前記第1のMOSトランジスタからの出力電流が入力される。前記第2のMOSトランジスタは、前記カレントミラー回路の出力端子の電圧が入力されるゲート端子を有し、ソース接地とされ、前記第1のMOSトランジスタの極性と同じ極性を有する。前記負荷は、前記カレントミラー回路の前記出力端子に接続される。第1帰還抵抗は、前記第1のMOSトランジスタの前記ゲート端子と、前記第2のMOSトランジスタのドレイン端子と、の間に接続される。前記第2のMOSトランジスタは、前記ゲート端子電圧に対応した電圧を前記ドレイン端子から出力することを特徴とする。

(もっと読む)

D級アンプ

【課題】負荷を駆動するトランジスタの駆動能力を落とすことなく、トランジスタの電源である電池の消耗を少なくしたD級アンプを提供する。

【課題の解決手段】D級アンプは、外部電池10の供給電圧から昇圧電圧を生成する昇圧回路20と、電池10を電源として駆動されるその正負極間に直列接続されたPMOSトランジスタ30及びNMOSトランジスタ40と、昇圧電圧及び接地電圧を電源とし入力信号をPWM変調したパルスに基づいて各トランジスタ30,40を交互にオンオフ駆動する駆動回路60と、この駆動回路60の出力端とPMOSトランジスタ30のゲートとの間に接続された容量素子70と、駆動回路60の出力が昇圧電圧であるタイミングで電池10の正電極とPMOSトランジスタ30のゲートとを接続するスイッチ素子80とを備え、各トランジスタ30,40の接続点の電圧に基づき負荷100を駆動する。

(もっと読む)

定電圧バッファ回路

【課題】スタートアップ時などに、演算増幅回路の出力電圧が、駆動能力の高い側とは反対方向に大きくずれた場合においても、出力段の定電流源に制限されることなく、所定電圧へのセットリングを加速することが可能な定電圧バッファ回路を提供すること。

【解決手段】基準電圧(Vref)をバッファし、一定電圧の出力電圧(Vout)を供給する定電圧バッファ回路であって、出力電圧と基準電圧とを取得する差動増幅器(1)と、差動増幅器(1)の出力信号に応じて制御されるP型駆動の出力手段(2)と、出力電圧が基準電圧よりも大きいことを検出する検出手段(M11)と、検出手段(M11)において、出力電圧が基準電圧に対して大きいことが検出された場合には、出力ノードから電流を引き出すように電流を制御する電流制御手段(3)とを有する定電圧バッファ回路。

(もっと読む)

オーディオ信号処理回路および電子機器

【課題】アンプに対する電源電圧を好適に制御する。

【解決手段】メインアンプ4は、オーディオ信号S1を増幅する。電源回路2は、アンプの上側電源ラインに正の電源電圧CPVDDを、下側電源ラインに負の電源電圧CPVSSを供給する。電圧検出部32は、アンプにより増幅されたオーディオ信号S2の振幅が所定のしきい値より大きいときアサートされる電圧検出信号S21を生成する。電流検出部34は、メインアンプ4の出力段に流れる負荷電流ILが所定のしきい値電流ITHより大きいときアサートされる電流検出信号S22を生成する。電圧制御部30は、電圧検出信号S21がネゲートされると、電源回路2が生成する正および負の電源電圧の絶対値を低下させる。また電圧検出信号S21がアサートされ、または電流検出信号S22がアサートされると、電源回路2が生成する正および負の電源電圧の絶対値を増大させる。

(もっと読む)

演算増幅器

【課題】所定のS/Nを維持しながら消費電流の増加を抑制することのできる演算増幅器を提供する。

【解決手段】実施形態の演算増幅器は、正相信号Vpと逆相信号Vmが入力される差動増幅回路100と、差動増幅回路100へ動作電流を供給するカレントミラー回路200とを有する。この演算増幅器は、入力信号電圧検出回路1が、正相信号Vpと逆相信号Vmとの間の電圧差を検出し、動作電流制御回路2が、その電圧差の大きさに応じた制御信号を出力する。この制御信号の制御により、可変定電流回路3が、カレントミラー回路200へ入力する定電流の大きさを変化させる。

(もっと読む)

高周波電力増幅装置

【課題】出力電力を高効率で伝達可能な高周波電力増幅装置を提供する。

【解決手段】例えば、差動増幅器AD101,AD102と、その各出力インピーダンスを整合するトランスフォーマTR101を備え、AD101の差動出力ノード間にインダクタL101、スイッチS101、インダクタL102を直列に接続する。AD102が動作状態、AD101が非動作状態の場合には、S101がオンに制御される。この場合、AD101に含まれる差動対のトランジスタのオフ容量を踏まえて1次コイルLD111/LD112の両端から見たAD101側のインピーダンスが高インピーダンス状態(並列共振状態)となり、等価的に、AD102の動作に際してLD111/LD112は影響しなくなる。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

可変調整精度を有する増幅器回路

【課題】 増幅器回路の可変精度の調整を実現するシステム及び方法を提供する。

【解決手段】 本開示の一態様によると、システムは、増幅器の利得を離散的な利得レベルに設定する複数の調整段を有する増幅器を有する。特定の実施形態では、調整段は直列に接続され、調整段の各々は、スイッチに並列に接続された抵抗器を有し、該スイッチはオフにされ、増幅器に利得を隣接する利得レベルに設定させる。特定の実施形態では、複数の利得レベルのうちの隣接する各々間の利得の差は、低い利得レベルより高い利得レベルにおいて大きい。

(もっと読む)

送信機の電力効率を向上させるシステム及び方法

【課題】 送信機の電力効率を向上させるシステム及び方法が提供される。

【解決手段】 本開示の幾つかの実施形態によると、回路は、入力コイルの第1の入力ポート及び第2の入力ポートにおいて無線周波数(RF)信号を受信するよう構成されたバランを有する。バランは、入力コイルに通信可能に結合された出力コイルにおいてRF信号を出力するよう更に構成される。回路は、入力コイルに結合され、入力コイルにおいて受信したRF信号の電力レベルに従って、入力コイルにおけるバイアス電圧を調整するよう構成された供給電圧選択回路も有する。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

41 - 60 / 1,872

[ Back to top ]