Fターム[5J500AH10]の内容

増幅器一般 (93,357) | 回路素子 (16,323) | 半導体素子 (6,058) | FET (3,573) | MOSFET、MISFET(絶縁ゲート形電界効果トランジスタ) (1,872)

Fターム[5J500AH10]に分類される特許

81 - 100 / 1,872

デジタルアンプ、デジタルアンプの制御方法およびプログラム

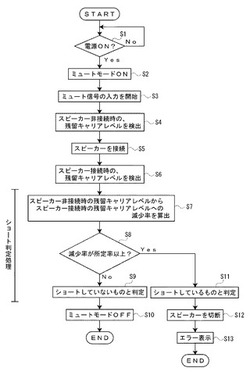

【課題】高い処理速度を必要とせず且つ簡単な回路構成にすることができると共に、自身の回路にダメージを与えることなくスピーカーのショート判定を行うことができる。

【解決手段】スピーカー12と接続されて用いられるデジタルアンプ11であって、アナログ音声信号をパルス信号に変調する比較回路23と、変調した音声信号を増幅する増幅回路25と、増幅した音声信号を、アナログ信号に復調しつつ、その高周波成分を減衰するローパスフィルター26と、起動時にテスト信号を入力するミュート切替部29と、テスト信号をローパスフィルターに通した後の残留キャリアレベルを検出するレベル検出部27と、検出したテスト信号の残留キャリアレベルに基づいて、スピーカーがショートしているか否かを判定する制御部31と、を備えた。

(もっと読む)

オペアンプ

【課題】位相余裕を減らすことなく電源立ち上げ時における出力電圧の立ち上がりを速くする。

【解決手段】電源電圧が立ち上がると、入力電圧VinpがVinmよりも高くなるので、トランジスタ9がオン、トランジスタ10がオフとなり、差動対11に供給される動作電流は全てトランジスタ9に流れる。電流検出回路62に電流が流れないので、トランジスタ73がオフし、第2の定電流回路69が出力する増分動作電流I2は、ダイオード72を通して差動対11に流れ込む。トランジスタ9に流れる電流は定常動作電流I1+増分動作電流I2となり、位相補償コンデンサ8の充電電流が増えて出力電圧Voの立ち上がりが速くなる。

(もっと読む)

パワーアンプ回路および回路装置

【課題】電源電圧が低下した場合も、出力信号の位相が変化しないパワーアンプ回路の実現。

【解決手段】電源VDDと、電源に接続されたMOSトランジスタTr,Trxと、MOSトランジスタのゲート・ドレイン間に接続された補償容量Cxgd,Cxgdxと、を有し、補償容量は、電源の電圧変化に応じて変化するMOSトランジスタのゲート・ドレイン間容量Cgd,Cgdxの変化を相殺するように、電源の電圧変化に応じて容量値が変化する特性を有するパワーアンプ回路。

(もっと読む)

差動増幅回路及びコンパレータ

【課題】オフセット電圧の変動を低減した差動増幅回路及びコンパレータを提供する。

【解決手段】実施形態によれば、差動回路と、出力回路と、クリップ回路と、を備えたことを特徴とする差動増幅回路が提供される。前記差動回路は、一対の入力信号の電位差に応じた一対の差動電流を生成する。前記出力回路は、前記一対の差動電流を受けて、電流差に応じた出力電圧を生成する。前記クリップ回路は、前記出力電圧に応じてオンし、前記出力電圧をしきい値電圧を含みローレベルまたは前記ローレベルよりも高いハイレベルに変換できる範囲に抑制するクリップ素子を有する。

(もっと読む)

バイアス回路を一体化した金属酸化膜半導体デバイス

【課題】デバイスの温度変動および/またはプロセス変動に起因するMOSデバイスのバイアス条件の変動を正確に補償できる技術を提供する。

【解決手段】ICデバイスがゲート端子、ソース端子およびドレイン端子を有するMOSデバイスを備え、ゲート端子はICデバイスの入力部に動作可能に結合され、ドレイン端子はICデバイスの出力部に動作可能に結合され、ソース端子は負電圧供給源に結合している。ICデバイスは、さらに、MOSデバイスのゲート端子に動作可能に結合されているバイアス発生器を備え、このバイアス発生器は、MOSデバイスにほぼ一定の静止動作点でバイアスをかけるバイアス電圧および/またはバイアス電流を発生する。バイアス発生器は、バイアス電圧および/またはバイアス電流がMOSデバイスの接合温度の関数として変化するように構成されている。このようにして、バイアス発生器が、MOSデバイスの1つまたは複数の動作条件を正確にたどり、それによってデバイスの性能を向上させる。

(もっと読む)

スイッチング回路

【課題】整数倍の信号成分に起因して、負荷回路やスイッチング素子に余分な電流が流れない電力効率を向上したスイッチング回路を提供する。

【解決手段】スイッチング回路1は、第1端子50a及び第2端子50bを有しており、パルス信号により駆動されて第1端子及び第2端子の導通状態をスイッチするスイッチング素子10と、スイッチング素子の第1端子13に電圧を供給する電源部30と、電源部に並列に接続される負荷回路40と、電源部と負荷回路との接続点Pと、スイッチング素子の第1端子との間に接続され、パルス信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、接続点からスイッチング素子へ流れる電流を抑制する受動回路部50と、受動回路部と接続点との間に接続され、N倍の周波数において共振する共振回路部60と、を備える。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】ゼロクロス付近においてもスイッチングの動作周期に基づく時間内にエネルギーの転送が終了するような駆動信号を生成して、その駆動信号によって容量性負荷を駆動するための各動作フェーズの動作を本来の動作時間通りに行うことのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】ゲートドライバ回路23は、駆動信号VCN,VCPがゼロクロス付近の範囲RZにあるときに、PMOSトランジスタ47,49およびNMOSトランジスタ50,51の導通状態を切り換える。これによって、圧電スピーカー駆動用アンプ14は、動作状態を、通常動作状態からゼロクロス動作状態にする。そして、その駆動信号VCN,VCPによって圧電スピーカー15を駆動するための各動作フェーズを、本来のスイッチング動作周期に基づく時間通りに行うことができる。

(もっと読む)

高線形性相補型増幅器

【課題】サブミクロンCMOSプロセスで製造されることができかつ良好な線形性および信頼性を有する相補型増幅器を提供する。

【解決手段】PMOSトランジスタ422とそれにスタック結合されたNMOSトランジスタ412で構成した相補型増幅器400で、NMOSトランジスタ412およびPMOSトランジスタ422は、別々のバイアス電圧を有し、それらのバイアス電圧は、各トランジスタの相互コンダクタンスの低高および高低遷移をオーバーラップさせるように選択され、各トランジスタの幅および長さ寸法は、中反転領域におけるNMOSトランジスタ412の入力容量の変化および相互コンダクタンスの変化を中反転領域におけるPMOSトランジスタ422の入力容量の変化および相互コンダクタンスの変化と整合させるように選択される。それによりほぼ一定の総入力容量およびほぼ一定の総相互コンダクタンスを有しうる。

(もっと読む)

電力増幅器、及び、電子装置

【課題】

出力の線形性を改善した電力増幅器、及び、電子装置を提供する。

【解決手段】

電力増幅器は、所望波が差動入力される一対の第1増幅部と、前記第1増幅部の出力側に接続される一対の第2増幅部と、前記第2増幅部の出力側に接続されるトランスと、電源から前記第1増幅部に電力を供給するとともに、前記トランスを介して前記第2増幅部に電力を供給する電力供給線と、前記第1増幅部と前記第2増幅部との間に接続され、前記所望波を前記第2増幅部に通過させるとともに、前記所望波の二次歪み成分を遮断する遮断回路とを含む。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】なるべく少ない数のスイッチング素子で差動信号の駆動信号を生成して、その駆動信号によって容量性負荷を駆動することのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】圧電スピーカー駆動用アンプ14は、キャパシタ41から圧電スピーカー15に転送されたエネルギーを抵抗等でなるべく消費させずに、圧電スピーカー15を駆動するためのエネルギーに再利用する。その際に、ゲートドライバ回路23は、第1フェーズから第4フェーズまでの各動作フェーズに合わせて、スイッチング駆動回路24のPMOSトランジスタ45〜49の導通状態を切り換える。これによって、圧電スピーカー駆動用アンプ14は、なるべく少ない数のスイッチング素子で、差動信号の駆動信号を生成して、その駆動信号によって圧電スピーカー15を駆動することができる。

(もっと読む)

レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置

【課題】レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置を提供する。

【解決手段】本願発明は、増幅器であって、入力信号を受け取るための入力ステージと、前記入力ステージに連結されると共に、前記入力信号に応答して出力ドライバステージに対して駆動信号を提供する高利得ステージと、前記出力ドライバステージに連結された出力端子とを具備することを特徴とする。前記出力ドライバステージは、前記高利得ステージから第1の駆動信号“pdrive”を受け取る第1の端子、第1の電圧降下を通じてVDDに連結された第2の端子、及び、前記増幅器の前記出力端子に連結された第3の端子を有する高電位側ドライバ回路を備える。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

パルス幅変調回路およびスイッチングアンプ

【課題】 蓄積手段に蓄積された電圧が無駄に放電されることを防止する。

【解決手段】 コンパレータCOMP1の出力がハイレベルのときに、コンデンサC3は、コンデンサC1の電圧によって充電される。次に、コンパレータCOMP1の出力がローレベルのときに、コンデンサC3の電圧が定電流Iの生成に使用される。同様に、コンパレータCOMP2の出力がハイレベルのときに、コンデンサC4は、コンデンサC2の電圧によって充電される。コンパレータCOMP2の出力がローレベルのときに、コンデンサC4の電圧が定電流Iの生成に使用される。従って、コンデンサC1、C2の電圧が無駄に放電されることが無く、定電流Iの生成に再度利用することができる。

(もっと読む)

完全差動型オペアンプ

【課題】完全差動型オペアンプの動作の安定度を向上し、高速動作を可能にする。

【解決手段】差動増幅部は、第1ステージの第1の差動増幅回路と、第2ステージの第2の差動増幅回路2から構成される。位相補償回路5は、第2の差動増幅回路2の差動入力端子と差動出力端子との間に接続されている。第1のCMFB回路3は、第1ステージの差動増幅回路1の差動出力電圧VP,VNの第1の同相電圧VC1が第1の基準電圧になるように、第1の差動増幅回路1をフィードバック制御する。第2のCMFB回路4は、第2の差動増幅回路2の差動出力電圧VOUTP,VOUTNの第2の同相電圧VC2が第2の基準電圧になるように、第2の差動増幅回路2をフィードバック制御する。

(もっと読む)

トランスインピーダンスアンプ

【課題】利得周波数特性の広帯域化と群遅延平坦特性とを両立させる。

【解決手段】ソース接地トランジスタM1、ゲート接地トランジスタM2、および負荷抵抗RLからカスコード接続回路11を構成し、ソース接地トランジスタM1のドレイン端子とゲート接地トランジスタM2のソース端子と間に第1のインダクタL1を設ける。

(もっと読む)

受信機および高周波増幅器

【課題】高周波増幅器の消費電流の増加を伴うことなく、良好なNFを得ることのできる受信機を提供する。

【解決手段】負荷抵抗としての抵抗R1とこれに直列に接続されたMOSトランジスタM1からなるシングル増幅回路1と、MOSトランジスタM2およびM3からなる差動対を有する差動増幅回路2とから高周波増幅器10を構成する。MOSトランジスタM1のゲートに増幅対象の信号を入力し、シングル増幅回路1の出力をDCバイアスカット用のキャパシタC1を介して差動増幅回路2の差動対の一方のMOSトランジスタM2のゲートに入力し、他方のMOSトランジスタM3は無入力とする。MOSトランジスタM2およびM3からなる差動対の出力信号を、高周波増幅器10の出力信号として出力する。高周波増幅器10のNFが改善されるため受信機100のNFが改善されることになる。

(もっと読む)

スイッチングアンプ

【課題】 簡単な回路構成であり、かつ、正確に、電源電圧のパンピング現象、および、出力電圧の直流成分を検出すること。

【解決手段】 トランジスタQ1は、スイッチングアンプの出力電圧に正の直流電圧が含まれることを検出する機能と、正側電源電圧+VBにパンピング現象が生じていることを検出する機能とを兼有する。トランジスタQ2は、スイッチングアンプの出力電圧に負の直流電圧が含まれることを検出する機能と、負側電源電圧−VBにパンピング現象が生じていることを検出する機能とを兼有する。パンピング現象が生じていない場合、ツェナーダイオードD1、D2は共にオフ状態である。従って、抵抗R4、R5が、直流電圧検出の精度の低下を防止できる。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

半導体装置

【課題】シングルエンド−差動変換器を備えた半導体装置において、理想的な出力差動電流特性が得られる周波数の上限を向上させる。

【解決手段】入力電圧Vinを、パッケージ3の外部電極PIN1に入力し、外部電極PIN1、ボンディングワイヤWire1、チップ2の入力端子PAD1、シングルエンド−差動変換器1の入力端子Tin1を介してゲート接地のMOSトランジスタM1のソースに伝達する。また、外部電極PIN1、ボンディングワイヤWire2、チップ2の入力端子PAD2、シングルエンド−差動変換器1の入力端子Tin2を介してソース接地のMOSトランジスタM2のゲートに伝達する。

(もっと読む)

81 - 100 / 1,872

[ Back to top ]