Fターム[5J500AH10]の内容

増幅器一般 (93,357) | 回路素子 (16,323) | 半導体素子 (6,058) | FET (3,573) | MOSFET、MISFET(絶縁ゲート形電界効果トランジスタ) (1,872)

Fターム[5J500AH10]に分類される特許

21 - 40 / 1,872

EM級増幅器

【課題】高調波歪みを容易に低減させることのできるEM級増幅器を提供する。

【解決手段】本発明にかかるEM級増幅器は、主回路と、主回路に信号を入力する補助回路と、を有するEM増幅器であって、主回路は、プッシュプル構造を有することを特徴とする。この場合において、限定されるわけではないが、プッシュプル構造は、第一の主基礎回路と、第一の主基礎回路と同様な構造の第二の主基礎回路と、第一の主基礎回路と第二の主基礎回路に接続される負荷回路と、を有して構成される。

(もっと読む)

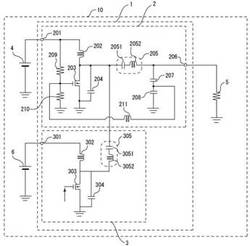

同相電圧帰還回路及び全差動演算増幅器

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

電流出力回路

【課題】アイドリング電流の影響を受けることなく高精度に電流検出を行うことが可能な電流出力回路を小規模な回路で実現すること。

【解決手段】第1の増幅器と、第1の増幅器の出力を入力するプッシュプル形出力段と、プッシュプル形出力段の第1のトランジスタ及び第2のトランジスタに対して夫々カレントミラー接続した電流検出器の第3のトランジスタ及び第4のトランジスタと、第3のトランジスタのドレインを第1のトランジスタのドレインの電位と等しくするバッファ回路と、第4のトランジスタのドレインに接続された電流検出抵抗と、を備える。プッシュプル形出力段の増幅信号は、負荷を介して第1の増幅器の反転入力端子に接続される。この構成により、電流検出抵抗にアイドリング電流を流さないようにすることができる。

(もっと読む)

デジタルアンプ及びデジタルアンプのテスト方法

【課題】安価な試験装置を用いても、PWM信号のパルス幅を測定可能にするデジタルアンプを提供する。

【解決手段】PWM信号のキャリア周期とPWM信号のパルス幅を測定する際の目標分解能との和に基づく周期であるサンプリングクロックSCLKの第1の論理から第2の論理への遷移に応じて発生させたサンプリング信号SCLKDIV(微分回路21の出力)と、PWM信号との論理積の結果(アンド回路22の出力)をカウントし、カウント結果に基づいてPWM信号のパルス幅を示すカウント値を出力するテスト回路部10bを設けたことを特徴とする。

(もっと読む)

スイッチングシステムおよびスイッチングシステムの制御方法

【課題】EMIを低減できるスイッチングシステムを提供する。

【解決手段】本発明は、スイッチングシステムを提供する。スイッチングシステムは、Hブリッジ、電流ルーターおよび制御回路を含む。Hブリッジは、第一出力ノードに結合される第一スイッチと第二スイッチおよび第二出力ノードに結合される第三スイッチと第四スイッチを含み、ロードは、第一出力ノードと第二出力ノード間に結合される。電流ルーターは、第一出力ノードと第二出力ノード間に結合される第一シャントスイッチと第二シャントスイッチを含む。制御回路は、第一制御信号を生成して、第一スイッチと第四スイッチを制御し、第二制御信号を生成して、第二スイッチと第三スイッチを制御し、第三制御信号を生成して、第一シャントスイッチを制御し、第四制御信号を生成して、第二シャントスイッチを制御する。

(もっと読む)

定電流回路

【課題】1または複数の他の定電流回路との間で共通インピーダンスを共有する定電流回路の出力電流に、他の定電流回路の出力電流に起因した誤差が生じることを防ぐ。

【解決手段】オペアンプと、当該オペアンプの出力端子にゲートが接続されドレインが当該定電流回路の出力端となる電界効果トランジスタと、この電界効果トランジスタのソースと共通インピーダンスとの間に介挿された抵抗と、を有する定電流回路に、共通インピーダンスおよび抵抗の共通接続点の電圧を第1の基準電圧とし、オペアンプの非反転入力端子には、第2の基準電圧と第1の基準電圧と電位差を所定の分圧比で分圧した電圧を印加し、同反転入力端子には、電界効果トランジスタのソースおよび抵抗の共通接続点の電圧と第3の基準電圧との電位差を所定の分圧比で分圧した電圧を印加する分圧回路を設ける。

(もっと読む)

バイアス回路およびそれを有するアンプ回路

【課題】増幅トランジスタのトランスコンダクタンスgmの変動を抑制する。

【解決手段】バイアス回路は,第1のドレイン電流を生成する第1のトランジスタと,第2のドレイン電流を生成する第2のトランジスタと,直列に接続された複数の抵抗素子を有し,複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有する。そして,抵抗回路の第1のノードの第1の電圧が第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が第2のトランジスタのゲートに印加され,第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力される。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

基準電圧発生回路

【課題】小規模の付加回路により、基準電圧の温度特性を簡易な調整によって十分に改善することができる基準電圧発生回路を提供する

【解決手段】バイポーラトランジスタ106、バイポーラトランジスタ106と並列に接続されるバイポーラトランジスタ107、バイポーラトランジスタ107のエミッタに一端が接続される抵抗素子104、バイポーラトランジスタ106のベース電位と、バイポーラトランジスタ107のベース電位との差分によって生じる差電圧を発生させる抵抗素子109、バイポーラトランジスタ106のエミッタ電位と抵抗素子104の他端の電位とが等しくなるように動作する演算増幅器105によって基準電圧発生回路を構成し、抵抗素子109が生成する差電圧が、温度によって変化する。

(もっと読む)

ソースフォロア回路

【課題】複数段構成におけるソースフォロア回路において入出力レンジを確保する。

【解決手段】ソースフォロア部SF11、SF12間に、ゲートドレイン間がダイオード接続され且つソースフォロア部SF11およびSF12を構成するMOSトランジスタM11およびM12と同一チャネル種類のMOSトランジスタM13とそのドレインに接続された電流源C13とからなる接続部11を設け、前段のソースフォロア部SF11の出力端とMOSトランジスタM13のソースとを接続し、MOSトランジスタM13のドレインと後段のソースフォロア部SF12の入力端とを接続する。接続部11における入出力間の電圧レベルのシフト方向は、ソースフォロア部SF11、SF12における入出力間の電圧レベルのシフト方向と逆となり、電圧シフトを打ち消す方向に作用するため、電圧レベルのシフトにより入出力レンジが狭くなることを抑制することが可能となる。

(もっと読む)

バラン

【課題】プッシュプル電力増幅器に適用できるバランであって、バランを介してプッシュプル電力増幅器に、2次高調波を注入もしくは抽出し得る、または直流バイアスを印加し得るバランを提供する。

【解決手段】基本波f0に対して1/4波長の長さを有し、性能が同等の2つの結合伝送線路11,12を用いて構成され、2次高調波を注入もしくは抽出し、または直流バイアスを印加できるように、入力される周波数により短絡および開放を切り換える周波数選択性インピーダンス回路23を設け、これによりバラン103を介してプッシュプル電力増幅器に、2次高調波を注入もしくは抽出することを可能にするとともに、直流バイアスの印可を可能にする。

(もっと読む)

ソースフォロア回路

【課題】消費電力の増加を抑制しつつ、負荷回路からのキックバックを抑制する。

【解決手段】MOSトランジスタM11と、ゲートおよびドレイン間がダイオード接続されたMOSトランジスタM12と、電流源C11とを直列接続してソースフォロア回路10を構成する。MOSトランジスタM11のゲートに入力された、ソースフォロア回路10への入力信号Vinは、MOSトランジスタM11によりほぼ1倍の利得で出力され、さらに、ダイオード接続されたMOSトランジスタM12でほぼ1倍の利得で出力され、これがソースフォロア回路10の出力信号Voutとして出力されるため、結果的に、1段構成のソースフォロア回路と同様の動作をするが、その消費電力は少なくてすむ。

(もっと読む)

トランスインピーダンスアンプ

【課題】広帯域かつ平坦性の高い利得周波数特性を有するトランスインピーダンスアンプを提供する。

【解決手段】トランスインピーダンスアンプは、コア回路6と、コア回路6の出力信号振幅を検出する出力信号モニタ回路7と、振幅検出値に基づいてコア回路6の利得および周波数ピーキング量を制御する制御回路8を備える。制御回路8は、出力信号モニタ回路7の第一の帯域通過フィルタの通過帯域におけるコア回路6の出力信号振幅が所望の値になるように、出力信号モニタ回路7の第一の振幅検出回路が検出した検出値に基づいて帰還抵抗RFの値を変化させ、出力信号モニタ回路7の第二の帯域通過フィルタの通過帯域におけるコア回路6の出力信号振幅が所望の値になるように、出力信号モニタ回路7の第二の振幅検出回路が検出した検出値に基づいて周波数ピーキング量を変化させる。

(もっと読む)

センサ信号処理装置

【課題】簡単な構成で入力オフセット電圧の温度依存性が小さいセンサ信号処理装置を提供する。

【解決手段】センサ用電源として第1の電源電圧V´ccを供給されて動作し、センサ出力Vs1、Vs2を出力するセンサ部100と、信号処理用電源として第2の電源電圧Vccを供給されて動作し、センサ出力Vs1、Vs2が入力される差動対を使用する差動増幅部を有して信号処理を行なう信号処理部200と、を有してセンサ信号処理装置1を構成する。この第1の電源電圧V´ccは、信号処理部200の差動増幅部250の入力電圧範囲の下限領域に設定される。

(もっと読む)

半導体装置、電子装置、車両、及び過熱検出方法

【課題】過熱検出回路の検出温度がばらつくことを抑制する。

【解決手段】コンパレータ170には、第1抵抗110と第1定電流源120の間の電圧Aと、ダイオード130と第2定電流源140の間の電圧Bが入力される。第1リーク電流源150は、ドレインが第1抵抗110と第1定電流源120の間に接続されており、ソース及びゲート電極が第1定電流源120と第2配線104の間に接続されている。第2リーク電流源160は、ドレインが第1配線102とダイオード130の間に接続されており、ソース及びゲート電極がダイオード130と第2定電流源140の間に接続されている。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

抵抗の調整機能を有する演算回路

【課題】MOSスイッチによる抵抗の調整機能を有する演算回路において、面積の増加を最小限に留め、かつ、非常に簡易な方法でMOSスイッチの寄生容量の影響を抑える演算回路を提供する。

【解決手段】MOSスイッチ21−23のゲートやバックゲートに、調整対象の抵抗11−13よりも数倍以上大きな抵抗31−33、61を設けることにより、寄生容量でできる極とほぼ同じ周波数にゼロが発生し、寄生容量の影響を抑えることができる。この抵抗には、絶対値バラつきや温度特性、相対バラつきやノイズ等の特性は要求されないため、用いるプロセスで最もシート抵抗の高い抵抗を細い幅で作成すればよく、面積の増加量は少ない。また、抵抗は容量よりも微細化が容易であるため、今後更にプロセスの微細化が進んでも本発明を変わらず使用できる。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】低ノイズ係数(NF)、高利得、及び低電流消費と共に、非常に高い三次入力インターセプトポイント(IIP3)を有する低ノイズ増幅器(LNA)を提供する。

【解決手段】修正された微分重ね合わせ(DS)低ノイズ増幅器(LNA)222は、メイン電流経路320とキャンセル電流経路322を含む。キャンセル経路の三次歪みは、メイン経路の三次歪みをキャンセルするために使用される。新規な一側面では、分離されたソース・ディジェネレーション・インダクタ306,308が、2つの電流経路の各々につきあり、これにより他方の電流経路に影響を与えることなく、一方の電流経路の調整を容易にする。第3の新規な側面では、キャンセル電流経路及び/またはデブースト電流経路がプログラマブルにディセーブルとされて、高線形性を求めない動作モードにおいて電力消費を低減し、ノイズ量を改善する。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

電圧電流変換回路および電圧制御発振回路

【課題】入力電圧に正確に対応した値の出力電流を得ることができる電圧電流変換回路およびその電圧電流変換回路で生成した電流を用いて高精度な発振周波数を得ることができるようにした電圧制御発振回路を提供する。

【解決手段】3容量Csと、容量CBと、スイッチSW1〜SW4と、オペアンプOP1と、トランジスタM1,M2とを備え、スイッチSW1,SW2がオン/オフするときスイッチSW3,SW4がオフ/オンするようにスイッチSW1〜SW4を制御し、電圧入力端子1に入力した入力電圧Vinに比例した電流IREFをトランジスタM1のドレインから出力する。

(もっと読む)

21 - 40 / 1,872

[ Back to top ]