Fターム[5J500AH33]の内容

Fターム[5J500AH33]の下位に属するFターム

Fターム[5J500AH33]に分類される特許

201 - 220 / 1,197

歪み補償装置

【課題】メモリ効果歪みを効果的に打ち消すことのできる歪み補償装置を得る。

【解決手段】直流電源(30)と、直流電源から供給される直流電圧をパラメータとして変化させることで入力電力に対する利得特性および通過位相特性を調整する歪み補償回路(20)と、変調波信号の偶数次高調波、奇数次高調波、またはベースバンド変調波周波数のうち、少なくとも1つに対して振幅と位相を制御することで、歪み補償回路の能動素子からみた負荷インピーダンスを決定する整合回路(10)とを備え、整合回路は、歪み補償装置の入出力端子を結ぶ信号路に対して縦続に接続され、振幅と位相を制御することで、歪み補償装置の前段または後段に接続される増幅器の歪み成分と逆特性を持つ歪み成分を歪み補償回路から発生させる。

(もっと読む)

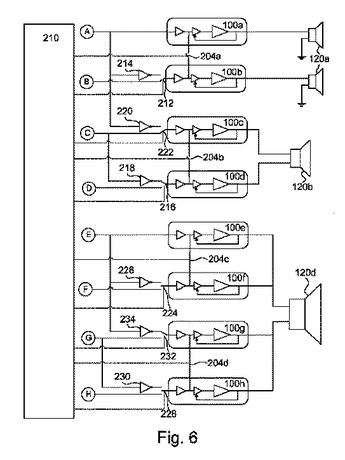

汎用オーディオ電力増幅器

オーディオ電力増幅器が、第1および第2の増幅ユニットを含み、それぞれが、スイッチング電圧増幅器と、出力フィルタと、電流補償器と、出力インダクタにおいて測定された電流の測定値を電流補償器の加算入力にフィードバックする内側電流フィードバックループと、電流補償器の加算入力に結合された電圧補償器と、外側電圧フィードバックループとを備えている。制御された信号経路が、第1の増幅ユニットの電圧補償器の出力を、第2の増幅ユニットの電流補償器に提供する。第1および第2の増幅ユニットは、別々の負荷と共に、共通の負荷を並列に駆動するように、またはブリッジ接続された負荷にわたって動作可能である。増幅ユニットの第2の対を追加して、第1の対と共に動作させて、ブリッジ接続された負荷のそれぞれの側で並列の対の増幅器を用いて単一のスピーカを駆動することができる。  (もっと読む)

(もっと読む)

電流センサを用いた平面オーディオ増幅器出力インダクタ

第1回路基板の層上に形成された第1複数巻線と、第2回路基板上の層に形成された第2複数巻線とを備えた平面インダクタ構造を有するオーディオ増幅器。前記平面インダクタ構造は、センサ巻線をさらに備えてもよい。  (もっと読む)

(もっと読む)

温度補償回路及び電力増幅器

【課題】高精度な温度補償を実現できる温度補償回路を提案する。

【解決手段】バイアス回路20は、絶対温度に関して正の線形温度特性を有するトランジスタTr1,Tr2,Tr3の電流又は電圧の温度変化を相殺するように、絶対温度に関して負の線形温度特性を有する基準電流をベースバイアス電流としてそれぞれのトランジスタTr1,Tr2,Tr3に供給するCTAT回路30と、CTAT回路30の温度特性とトランジスタTr1,Tr2,Tr3の温度特性とのずれを補償するための温度特性補償回路40を備える。

(もっと読む)

電力増幅器

【課題】多段接続される増幅器からのバイアス電流の逆流に起因するバイアス変動を効果的に抑制し、安定して信号増幅できる電力増幅器を提案する。

【解決手段】電力増幅器100は、トランジスタTr1〜Tr3を有する増幅系統10と、トランジスタTr4〜Tr6を有する増幅系統20と、トランジスタTr1〜Tr6のバイアス点を制御するバイアス回路31,32,33とを備える。増幅系統10は、最終段のトランジスタTr3以外のトランジスタTr1,Tr2を含む第一のグループと、少なくとも最終段のトランジスタTr3を含む第二のグループとを含む2つ以上のグループにグループ分けされている。バイアス回路31は、第一のグループに属するトランジスタTr1,Tr2にバイアス電流を分岐供給する。バイアス回路32は、第二のグループに属するトランジスタTr3にバイアス電流を供給する。

(もっと読む)

デジタルアンプ

【課題】出力電流の過電流及び共振電流の検出時間を短くするとともに、出力の停止を最小限にし、より適切な電流制御動作を可能にする。

【解決手段】デジタルアンプは、スイッチング素子Q1、Q2の出力部において、出力電流における所定値以上の過電流を検出する過電流検出回路19と、過電流検出信号の位相を進める進相回路22と、出力フィルタ15において共振が発生した際の出力電流に関する所定値以上の共振電流を検出する共振電流検出回路21とを有する。駆動回路12は、過電流検出信号または共振電流検出信号に基づき、出力電流の異常状態が検出された場合に、駆動信号をオフしてスイッチング素子Q1、Q2のスイッチング動作を停止させることで、電流制限動作を行う。

(もっと読む)

デジタルアンプ

【課題】起動時にブートストラップコンデンサの充電を簡単な制御で確実に行うデジタルアンプを提供すること。

【解決手段】デジタルアンプは、直列接続された2つのスイッチング部と、所定電圧の電源供給により動作して一方のスイッチング部を駆動する第1駆動部と、所定電圧より高い電圧の電源供給によって動作して他方のスイッチング部を駆動する第2駆動部とを有し、2つのスイッチング部を交互にオンオフすることによってデジタルパルス信号を増幅する増幅部と、第2駆動部に供給する電源をブートストラップするブートストラップコンデンサと、ブートストラップコンデンサの充電を制御するブートストラップ制御部とを備える。ブートストラップ制御部は、所定電圧にブートストラップコンデンサの出力電圧を加えたブート電圧が所定値未満であれば、ブートストラップコンデンサの充電を行う。

(もっと読む)

検出回路とそれを用いた半導体装置

【課題】本発明は、安価かつ容易に歪特性の劣化を抑制できる検出回路とそれを用いた半導体装置を提供することを目的とする。

【解決手段】電力増幅器とアンテナの間に配置された方向性結合器の結合線路両端の信号を用いて、該電力増幅器の歪特性劣化を検出する回路であって、該結合線路の結合端子の電力を移相および減衰する移相・減衰器と、該移相・減衰器からの出力電力と、該結合線路のアイソレーション端子の電力の差分を出力する手段と、該差分をDC信号に変換する検波回路と、該DC信号の電圧レベルが所定値よりも高いかを判定する比較回路とを備える。そして、該移相・減衰器は、該電力増幅器の歪特性が劣化する該アンテナ端の負荷状態において、該移相・減衰器が出力する信号の位相が該アイソレーション端子の信号の位相と180°の位相差になるように該結合端子の電力を移相することを特徴とする。

(もっと読む)

パワーアンプモジュール

【課題】複数の入力整合回路及び複数の出力整合回路をコンパクトに実装できるパワーアンプモジュールを提案する。

【解決手段】パワーアンプモジュール11は、それぞれが異なる周波数帯域を有する複数の無線信号を選択的に電力増幅するパワーアンプ20と、複数の無線信号のそれぞれについてパワーアンプ20の入力のインピーダンス整合を行うようにモノリシック集積回路化された複数の入力整合回路31,32と、複数の無線信号のそれぞれについてパワーアンプ20の出力のインピーダンス整合を行うようにモノリシック集積回路化された複数の出力整合回路41,42と、パワーアンプ20を搭載するとともに複数の入力整合回路31,32及び複数の出力整合回路41,42を内蔵する多層基板50を備える。

(もっと読む)

バイアス回路

【課題】 不要波の出力を抑制することのできる小型なバイアス回路を得ることを目的とする。

【解決手段】 半導体素子3に電力を供給するバイアス回路において、インダクタ5及びキャパシタ6が直列に接続された直列回路と、直列回路に並列に接続されて並列回路を構成するインダクタ7と、接地されたキャパシタ8とインダクタ7との間に接続され、外部から電力が供給されるバイアス端子9を備えて、直列回路および並列回路の共振により、半導体素子3の不要波を除去し所望の周波数のみを伝達する。

(もっと読む)

電源装置及びデジタルアンプ

【課題】回路サイズが小さい電源装置を提供すること。

【解決手段】電源装置は、直列接続された2つのスイッチング部と、所定電圧の電源供給によって動作して2つのスイッチング部を交互にオンオフする駆動部と、を有し、外部電源から得られた交流電力を直流電力に変換するスイッチング電源部と、外部電源から得られた交流電力を直流電力に変換して出力する電源部と、スイッチング電源部の駆動部が2つのスイッチング部の動作を制御するための制御信号を出力する制御部と、電源部の出力電力及び制御信号をスイッチング電源部の駆動部に伝送すると共に、入力側と出力側を絶縁する伝送部とを備える。

(もっと読む)

電子デバイスにおける無線周波数伝送を制御するためのシステムおよび方法

【課題】調波のレベルを低減させるためのシステムおよび方法を提供すること。

【解決手段】無線通信デバイスのために無線周波数伝送回路における電力増幅器からの出力信号の調波を低減させるための電子回路であって、通信デバイスのために出力信号を生成する電力増幅器と、出力信号のために電力増幅器の出力端子に接続された回路であって、該回路は、第1のフィルタリングステージ、遅延要素、および調波フィルタを含んでいる、回路とを備えており、遅延要素は、調波フィルタと出力端子との間に配置されており、遅延要素は、出力信号にタイミング遅延を提供し、調波フィルタは、出力信号の1次の調波を減衰させる周波数カットオフポイントを有しているローパスフィルタである、電子回路。

(もっと読む)

高周波増幅回路

【課題】高周波増幅回路において、LC共振を用いずにピーキングをかけること。

【解決手段】高周波増幅回路は、1段目にトランジスタTr1を用いたエミッタ接地増幅回路、2段目にダーリントン接続のトランジスタTr2、Tr3を用いたエミッタ接地回路の2段増幅の構成となっている。トランジスタTr1のエミッタとトランジスタTr2のコレクタとの間には容量素子が挿入されている。容量素子は、ダイオード接続のトランジスタTr4であり、トランジスタTr4のエミッタはトランジスタTr2のコレクタに、トランジスタTr4のベースおよびコレクタはトランジスタTr1のエミッタに接続されている。ダイオード接続のトランジスタTr4によって位相をずらしてフィードバックすることにより、高域での利得を向上させることができる。

(もっと読む)

マルチバンド電力増幅器

【課題】 インピーダンス不整合をなくしたマルチバンド電力増幅器を提供する。

【解決手段】 マルチバンド電力増幅器11の増幅器12,13間には、これらを整合させる段間整合回路14を設ける。また、入力段の増幅器12の入力側に入力段整合回路15を設けると共に、出力段の増幅器13の出力側には出力段整合回路16を設ける。そして、制御回路17は、基地局BSからの周波数設定情報Spによって第1,第2の送信信号TX1,TX2の通信周波数f11〜f1m,f21〜f2nを特定し、この特定した通信周波数f11〜f1m,f21〜f2nに応じて段間整合回路14、入力段整合回路15および出力段整合回路16のインピーダンス値Zm,Zi,Zoを最適な値に調整する。

(もっと読む)

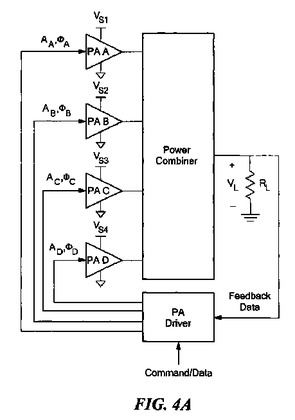

無線周波数(RF)増幅器回路および関係する技法

広帯域幅の線形増幅と高い平均効率の両方を同時に提供するための、電力結合およびアウトフェージングの、システムおよび関係する技法が説明される。線形増幅を提供することは、広範囲にわたってRF出力電力レベルを動的に制御し、一方でなお、広い周波数帯域幅にわたって動作する能力を包含する。本明細書で説明するシステムおよび技法は、高い平均効率が高度に変調された出力波形に対して実現され得るように、広範囲の出力電力レベル全体で高い効率を維持するようにさらに動作する。  (もっと読む)

(もっと読む)

増幅回路、集積回路装置及び電子機器

【課題】特性が安定し、増幅効率の良い増幅回路、集積回路装置及び電子機器等を提供すること。

【解決手段】増幅回路は、出力ノードNPに増幅信号VPを出力する増幅用トランジスター10と、インダクターLA及びキャパシターCA、CBにより構成され、インダクターのインダクタンス値及びキャパシターのキャパシタンス値の少なくとも一方が可変に設定されるLC負荷回路20と、増幅信号VPの電圧振幅を検出する振幅検出回路30と、振幅検出回路30の検出結果に基づいてインダクタンス値及びキャパシタンス値の少なくとも一方を設定し、増幅信号VPの電圧振幅値を極大値に近づける制御を行う制御回路40とを含む。

(もっと読む)

高周波増幅回路

【課題】高速に起動・シャットダウンが可能な高周波増幅回路を実現すること。

【解決手段】バイアス電圧Va、Vbの供給が停止されると、高周波信号を増幅するトランジスタTr1〜Tr3はオフとなる。また、同時にトランジスタTr4、Tr5がオフとなり、キャパシタC1、C2の放電は遮断される。そのため、キャパシタC1、C2には一定の電荷が保持される。その結果、高周波増幅回路1は高速にシャットダウンされる。また、バイアス電圧Va、Vbが供給されると、キャパシタC1、C2には一定の電荷が保持されるため、キャパシタC1、C2が充電されるまでの時間は非常に短くなる。そのため、高高周波増幅回路1は高速に起動される。

(もっと読む)

エラーアンプの位相補償回路

【課題】 ICチップ上のコンデンサ面積を小さくすることができる位相補償回路を提供する。

【解決手段】 エラーアンプの出力端子に容量と抵抗を直列接続し、容量に流れる電流を抵抗の両端に接続したトランスコンダクタンスアンプにより増幅してフィードバックすることにより、エラーアンプの周波数特性の主要極の周波数を低くする。

(もっと読む)

大電力増幅回路

【課題】DCバイアス電圧の供給構造を簡素化する。

【解決手段】同一高周波信号を増幅する増幅器A41,A42,A43,A44と、増幅器A41,A42の出力信号を合成する合成器S11と、増幅器A43,A44の出力信号を合成する合成器S12と、合成器S11,S12の出力信号を合成する合成器S13と、+VのDCバイアス電圧を合成器S13に印加する高周波カット用インダクタL11と高周波パス用キャパシタC11からなるバイアス供給回路とを設ける。+VのDCバイアス電圧を、合成器S13から合成器S11を経由して増幅器A41,A42に供給し、合成器S13から合成器S12を経由して増幅器A43,A44に供給する。

(もっと読む)

電力増幅器

【課題】異なる周波数、出力電力または変調方式において動作可能な電力増幅器および通信機器を提供できる。

【解決手段】入力端子および出力端子を有する第1増幅器PA2と、入力端子および出力端子を有する受動回路PC3と、単極端子と、2つの多投端子とを有する第1スイッチSW2と、を備えた電力増幅器であって、該第1スイッチSW2の該多投端子の一方は、該第1増幅器PA201の該入力端子に接続されており、該第1スイッチSW2の該多投端子の他方は、該受動回路PC3の該入力端子に接続されている。

(もっと読む)

201 - 220 / 1,197

[ Back to top ]