Fターム[5J500AH33]の内容

Fターム[5J500AH33]の下位に属するFターム

Fターム[5J500AH33]に分類される特許

121 - 140 / 1,197

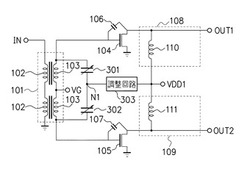

増幅回路

【課題】ドレインバイアスノードの電位を変化させた場合に、信号通過位相の変化を抑制することを課題とする。

【解決手段】増幅回路は、一次側インダクタが入力端子に接続され、二次側インダクタの中点がゲートバイアスノードに接続されるトランスフォーマー回路(101)と、ゲートが二次側インダクタの一端に接続され、ドレインが第1の出力端子に接続される第1のトランジスタ(104)と、ゲートが二次側インダクタの他端に接続され、ドレインが第2の出力端子に接続される第2のトランジスタ(105)と、第1の出力端子及びドレインバイアスノード間に接続される第1のインダクタ(110)と、第2の出力端子及びドレインバイアスノード間に接続される第2のインダクタ(111)と、トランスフォーマー回路の二次側インダクタに並列に接続され、ドレインバイアスノードの電位に応じて容量値が変化する可変容量(301,302)とを有する。

(もっと読む)

電力増幅器用バイアス回路

【課題】差分周波数Δfが数百MHzにおいても電力増幅器用バイアス回路のリップル電圧ΔVが抑制されてバイアス回路電圧が平滑化され、マイクロ波/ミリ波/サブミリ波帯の高周波に適用可能な電力増幅器用バイアス回路を提供する。

【解決手段】電力増幅器の出力側整合伝送線路のバイアス回路接続点に接続された第1ボンディングワイヤと、第1ボンディングワイヤの終端に接続された第2ボンディングワイヤと、第1ボンディングワイヤの終端に接続されたオープンスタブ伝送線路と、第2ボンディングワイヤの終端に接続されたバイパスリザバーキャパシタとを備える電力増幅器用バイアス回路。

(もっと読む)

整合回路及びこれを備えた電力増幅回路

【課題】小型化を図ることができる整合回路を提供する。

【解決手段】半導体装置1のインピーダンス整合を取るための整合回路であって、半導体装置1上に設けられた第1のボンディングパッド1A及び第2のボンディングパッド1Bと、半導体装置1の外部に設けられた外部電極1と、第1のボンディングパッド1Aと外部電極2とを接続する第1のワイヤ4Aと、第2のボンディングパッド1Bと外部電極2とを接続する第2のワイヤ4Bとによって形成されるインダクタを少なくとも1つ備える整合回路。

(もっと読む)

電力変換装置

【課題】大出力でスピーカが駆動された場合でも、出力電圧の変動を抑制することができる電力変換装置を提供する。

【解決手段】入力信号を増幅するアンプである負荷駆動回路2に対し、コントローラ11によってNMOSQ1をオンオフすることで電力を供給するDC/DCコンバータ1と、スピーカSPを駆動するアンプ出力電圧を検出するアンプ出力電圧検出機能と、検出したアンプ出力電圧の変化量とDC/DCコンバータ1の出力電圧とを演算した誤差信号をDC/DCコンバータ1にフィードバックするフィードバック機能とを備えたフィードバック回路4とを具備し、コントローラ11は、フィードバックされた誤差信号に基づいて、アンプ出力電圧が増加すると供給する電力量を増加させ、アンプ出力電圧が減少すると供給する電力量を減少させる。

(もっと読む)

差動増幅回路

【課題】入力電力に対する利得の線形動作領域を広くすることができる差動増幅回路を提供することを課題とする。

【解決手段】差動増幅回路は、ゲートが第1の差動入力信号端子に接続され、ソースが基準電位ノードに接続され、ドレインが第1の差動出力信号端子に接続される第1のトランジスタ(211)と、ゲートが第2の差動入力信号端子に接続され、ソースが基準電位ノードに接続され、ドレインが第2の差動出力信号端子に接続される第2のトランジスタ(212)と、第1のトランジスタのゲート及び第2のトランジスタのドレイン間に接続される第1の可変容量(401)と、第2のトランジスタのゲート及び第1のトランジスタのドレイン間に接続される第2の可変容量(402)と、第1の差動出力信号端子又は第2の差動出力信号端子の信号の包絡線を検波する第1の包絡線検波器(405)とを有する。

(もっと読む)

パルス駆動回路

【課題】高周波増幅用のFETのドレインに印加されるパルス電圧の安定化を図る。

【解決手段】駆動用電源11の出力電圧に基づきMOS−FETQ1を駆動する。Q1はパルス信号源12から出力される基準パルス信号bでスイッチングさせ、Q1オン時は、コンデンサC1の電荷を移行させて得られる電圧でQ1を非飽和状態で駆動する。Q1のスイッチングによりソース電極に得られるパルス電圧を、ゲート電極に供給される高周波信号を増幅する高周波電力FETQ2の駆動電圧としてドレイン電極に印加する。Q2のドレイン電極に発生するパルス電圧dと基準パルス信号bの電圧をオペアンプOP2で比較し、Q1のゲート電極にフィードバックする。非飽和状態で駆動されるQ1にフィードバックさせたことで、Q1に印加されるパルス内ドレイン電圧の低下を防止することができる。

(もっと読む)

高周波回路

【課題】最小ループと2セルループのオッドモード発振を共に抑制する高周波回路を提供する。

【解決手段】半導体基板上に並列に配列された複数のトランジスタと、第1の絶縁基板上に配置され、複数のトランジスタのゲート端子電極にそれぞれ接続された複数の入力整合回路と、第1の絶縁基板上に配置され、入力整合回路に隣接して配置された入力側第4発振抑制抵抗と、入力側第4発振抑制抵抗に直列接続された入力側第1キャパシタと、隣接する入力整合回路間を繋ぐ伝送線路上の点と入力側第1キャパシタ間に接続された入力側第1インダクタとを有する入力側発振抑制回路とを備え、入力側第1インダクタのインダクタンス値をL1、入力側第1キャパシタのキャパシタンス値をC1とすると、1/{2π(L1×C1)1/2}で表される入力側第1インダクタと入力側第1キャパシタの共振周波数が、2セルループの発振周波数fosc2に等しい高周波回路。

(もっと読む)

容量性負荷駆動回路

【課題】容量成分または誘導成分を有する容量性負荷の駆動信号を、安定してしかも電力

消費を抑制しながら生成する。

【解決手段】容量性負荷に印加すべき駆動信号の基準となる駆動波形信号を、パルス変調

することによって変調信号を生成し、得られた変調信号を電力増幅した後、平滑化するこ

とによって、駆動信号を生成する。また、こうして容量性負荷に印加された駆動信号を、

駆動信号の基準となる駆動波形信号に負帰還させる。このとき、駆動信号に含まれる周波

数帯域でのゲイン特性が平坦となるような所定のアナログ補償処理を駆動信号に対して加

えた後、得られた信号をデジタル信号に変換して、駆動波形信号に負帰還させる。

(もっと読む)

容量性負荷駆動回路

【課題】電源電圧を超えた電圧の駆動信号を発生させることが可能で、しかも環境温度や

部品の製造ばらつきの影響を受けることなく安定した駆動信号を発生させることが可能な

技術を提供する。

【解決手段】容量性負荷に印加すべき駆動信号の基準となる駆動波形信号を、パルス変調

することによって変調信号を生成し、得られた変調信号を電力増幅した後、平滑フィルタ

ーを用いて駆動信号を復調する。また、こうして得られた駆動信号を負帰還させることに

よって、平滑フィルターの共振ピークを抑制する。このとき、ピークを完全に抑制するの

ではなく、比較的広い周波数帯域でゲインが一定以上(たとえば2以上)となるようにす

ることで、電源電圧を超えた電圧の駆動信号を安定して発生させることが可能となる。

(もっと読む)

高周波信号処理装置

【課題】送信パワーばらつきの低減と高調波歪みの低減を実現可能な高周波信号処理装置を提供する。

【解決手段】例えば、飽和領域に動作点が定められたプリドライバ回路PDRと、線形領域に動作点が定められ、高いQ値を持つインダクタL1aによって線形増幅動作を行う最終段ドライバ回路FDRとを備える。例えば、電圧制御発振回路VCOによって直接変調された信号は、その振幅レベルのばらつきがPDRによって抑圧され、PDRで生じ得る高調波歪み成分(2HD,3HD)がFDRのL1a等によって低減される。

(もっと読む)

マルチ周波数マッチングのための単一マッチングネットワーク、その構築方法及び当該マッチングネットワークを使用するRFパワーサプライヤーシステム

【課題】プラズマ処理室のための選択的に二つの周波数のうちの任意の周波数にRFパワーを提供してプラズマ負荷にマッチングさせるための、二つの周波数入力に適用される単一マッチングネットワークを提供する。

【解決手段】単一マッチングネットワーク800は、マルチ周波数入力f1及びf2に接続される入力端子とプラズマ負荷に接続される出力端子を含み、入力端子と出力端子との間には互いに直列接続される容量値C0を有するコンデンサーとインダクタンス値L0を有するインダクタンスを含み、且つコンデンサーとインダクタンスはブランチ電路を構成し、ここで、容量値C0とインダクタンス値L0は、周波数f1でマッチング状態になるのに必要なブランチ電路のインピーダンスy1及び周波数f2でマッチング状態になるのに必要なブランチ電路のインピーダンスy2と特定な関係を満足するように設定される。

(もっと読む)

不均等入力電力分割を用いた増加されたバックオフ能力および電力付加効率を持つNウェイRF電力増幅器回路

【課題】RF電力増幅器の高効率動作

【解決手段】入力電力は分割され、不均等にキャリア増幅器および複数のピーク増幅器に供給されることによって、増加された電力負荷効率(PAE)および直線性を実現できる。それぞれのピーク増幅器は、キャリア増幅器へ提供される入力信号レベルより高い入力信号レベルを提供される。ピーク増幅器は、均等電力分割を用いて達成されえるよりも、より効率的にRF信号によって持ち上げられえ、よってスレッショルド近くにトランジスタのトランスコンダクタンス特性を補償し、同じ効率についてのバックオフ能力を増し、または同じバックオフ点における直線性を改善しえる。

(もっと読む)

保護装置、相補型保護装置、信号出力装置、ラッチアップ阻止方法、及びプログラム

【課題】保護対象のスイッチング素子のラッチアップを阻止することができる保護装置、相補型保護装置、信号出力装置及びプログラムを提供する。

【解決手段】PMOSトランジスタ106に対して過電流が流れていない状態でPMOSトランジスタ106を非導通状態にする場合、PMOSトランジスタ20A及びPMOSトランジスタ22の各々を導通状態とするように制御し、PMOSトランジスタ106に対して過電流が流れている状態でPMOSトランジスタ106を非道通状態にする場合、PMOSトランジスタ20Aを導通状態にすると共にPMOSトランジスタ22を非導通状態にするように制御する。

(もっと読む)

電子回路

【課題】低電源電圧を用いて高性能な電子回路を提供すること。

【解決手段】信号が入力される制御端子と第1端子と第2端子とを有する第1トランジスタT1と、第1トランジスタの第2端子が接続された制御端子と第1端子と第2端子とを有する第2トランジスタT2と、第2トランジスタの第2端子が接続された制御端子と第1端子と第2端子とを有する第3トランジスタT3と、第2および第3トランジスタの少なくとも一方における第1および第2端子間を経由し、経由したトランジスタよりも前段に位置するトランジスタの第2端子に直流電流を供給する第1直流経路31と、第2および第3トランジスタの少なくとも一方における第1および第2端子間を経由し、経由したトランジスタよりも前段に位置するトランジスタの第2端子に直流電流を供給する第1直流経路とは異なる第2直流経路32と、第1および第2直流経路の間を共通に接続する共通接続点N1と、を具備する電子回路。

(もっと読む)

送受信切替器における前置増幅器保護回路及び電力増幅器

【課題】本発明は送受信切替器における前置増幅器保護回路に関し、前置増幅器を保護することを目的としている。

【解決手段】送信波を入力して電力増幅させ、アンテナ5に供給して送信すると共に、アンテナ5からの信号を受信して前置増幅器7に与えるように構成され、送信と受信を切り替えることができるように構成された送受信切替器において、送信波を電力増幅してアンテナ5に供給する電力増幅器1と、該電力増幅器1の出力側に設けられた送信波を検出するためのカプラ10と、該カプラ10の出力を受けて、元の切り替え信号とのORをとり、切り替え信号として送受信切替器に与えるように構成する。

(もっと読む)

高周波差動増幅回路

【課題】安定性が高く、かつ高い利得を有する高周波差動増幅回路を提供する。

【解決手段】本発明の一実施形態としての高周波差増増幅回路は、第1MOSトランジスタ、第2MOSトランジスタ、第1正帰還素子および第2正帰還素子を備える。前記第1MOSトランジスタおよび第2MOSトランジスタは、ソースがそれぞれ第1電源に接続され、ドレインがそれぞれ負荷を介して第2電源に接続され、互いに反転した位相関係にある第1および第2入力信号をゲートで受ける。前記第1正帰還素子は、前記第1MOSトランジスタのゲートと、前記第2MOSトランジスタのドレインとの間に直列接続された第1キャパシタおよび第1可変抵抗を含む。前記第2正帰還素子は、前記第2MOSトランジスタのゲートと、前記第1MOSトランジスタのドレインとの間に直列接続された第2キャパシタおよび第2可変抵抗を含む。

(もっと読む)

電力増幅器および無線機

【課題】電源電圧の上昇に伴う余分な消費電流の増加を抑え、効率を改善した電力増幅器及びそれを備えた無線機を構成する。

【解決手段】電力増幅器101は、エミッタ接地された電力増幅用トランジスタQ1、この電力増幅用トランジスタQ1のベースと制御電圧入力端Vctlとの間に接続されたベースバイアス回路31、電力増幅用トランジスタQ1のコレクタと電源電圧入力端Vccとの間に接続されたインダクタL5、およびベース電圧調整回路41を備えている。電源電圧(Vcc)が上昇すれば、ベース電圧制御用トランジスタQaのベース電流(Iba)が増大し、コレクタ電流(Ica)が増大する。これにより、抵抗R3による電圧降下が大きくなって、A点の電位が下がり、電力増幅用トランジスタQ1のベース電位(Vb1)が下がる。そのため電力増幅用トランジスタQ1の消費電流(Icc)が抑制される方向に作用する。

(もっと読む)

双方向中継器

【課題】中継器内でループ発振の発生を抑制することができ、ひいては、動作を安定させることができる双方向中継器を得る。

【解決手段】入力されたディジタル信号を等化する等化器11a、11bと、等化器11a、11bの出力を増幅する可変利得増幅器12a、12bと、可変利得増幅器12a、12bの出力をオンオフするオンオフ回路13a、13bと、等化器11a、11bから出力されるディジタル信号のレベルを検出するレベル検出回路15a、15bと、レベル検出回路15a、15bによって検出された信号レベルと閾値電圧Vthとを比較し、信号レベルが閾値電圧Vthよりも小さい場合には、オンオフ回路13a、13bをオフする制御信号を出力するオンオフ制御回路16a、16bとを設けた。

(もっと読む)

増幅器及び方法

【課題】消費電力を低減できる増幅器および方法を提供する。

【解決手段】デジタル信号によりキャリア周波数を変調し、該変調された信号を増幅する増幅器は、デジタル信号に対して要求される音質、前記デジタル信号の音源、及び前記デジタル信号の音種のうち少なくとも1つを判定する判定部と、該判定結果に応じて、キャリア周波数を設定するキャリア周波数設定部と、デジタル信号により、キャリア周波数をパルス幅変調するパルス幅変調部とを有する。

(もっと読む)

高周波電力増幅器

【課題】部品の使用点数を減少させて実装面積を縮小すると共に、信号のスイッチ通過による通過損失を抑制する高周波電力増幅器を提供する。

【解決手段】整合回路23,25,26,27と少なくとも1以上の高周波電力増幅素子24とを有する高周波電力増幅器21であって、前記整合回路は2つのリアクタンス素子37,38,39,40が直列に接続された第1の整合ライン41及び第2の整合ライン42が並列に接続された回路と、前記第1の整合ラインの前記リアクタンス素子間及び前記第2の整合ラインの前記リアクタンス素子間とグランドに接続され何れか一方を選択可能なスイッチ43とを有し、該スイッチを切替えることで前記第1の整合ライン及び前記第2の整合ラインの何れか一方に信号を伝搬させ、他方を前記グランドに接続させる。

(もっと読む)

121 - 140 / 1,197

[ Back to top ]