Fターム[5J500AH33]の内容

Fターム[5J500AH33]の下位に属するFターム

Fターム[5J500AH33]に分類される特許

61 - 80 / 1,197

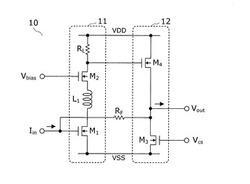

トランスインピーダンスアンプ

【課題】利得周波数特性の広帯域化と群遅延平坦特性とを両立させる。

【解決手段】ソース接地トランジスタM1、ゲート接地トランジスタM2、および負荷抵抗RLからカスコード接続回路11を構成し、ソース接地トランジスタM1のドレイン端子とゲート接地トランジスタM2のソース端子と間に第1のインダクタL1を設ける。

(もっと読む)

集積電力段

【課題】集積電力段において、入力電圧を集積電力段の一側面(例えば上面)で受け取り、出力電圧を集積電力段の反対側面(例えば底面)から出力する。

【解決手段】集積電力段は負荷段の上に位置する共通ダイを備え、共通ダイはドライバ段102及び電力スイッチ104を備える。電力スイッチは制御トランジスタ110及び同期トランジスタ112を含む。制御トランジスタのドレインD1が共通ダイの入力電圧を共通ダイの一側面(例えば上面)で受ける。制御トランジスタのソースS1が同期トランジスタのドレインD2に結合され、前記共通ダイの出力電圧を共通ダイの反対側面(例えば底面)で出力する。電力段の下にインターポーザ106を含めることができる。インターポーザは共通ダイの反対側面で共通ダイの出力電圧に結合される出力インダクタ118及び必要に応じ出力キャパシタ120を含む。

(もっと読む)

アクティブポストディストーション線形化を有する差動増幅器

【課題】電力消費量を低下させ、回路面積を縮小した線形性がより高いLNAを提供する。

【解決手段】差動増幅器300の一腕は第1トランジスタ310及び第2トランジスタは320、第1のカスケード対として結合され、第3トランジスタ330及び第4トランジスタ340は、第2のカスケード対として結合される。第3トランジスタ330は、第2トランジスタ320のソースに結合したゲートを有し、第4トランジスタ340は、第2トランジスタ320のドレインに結合したドレインを有する。第3トランジスタ330は、第1トランジスタ310によって生成される3次歪み成分を除去するのに用いられる歪み成分を生成する。誘導子350は、第1トランジスタ310に対してソースディジェネレーションを提供し、歪み除去を向上させる。第2トランジスタ320及び第3のトランジスタ330の大きさは、利得損失を低減させるために選択される。

(もっと読む)

CATV伝送用増幅器

【課題】端子仕様1、2を機械式スイッチを用いて切替える切替回路を備え、端子仕様切替時における設定エラーを検知して作業者に報知する。

【解決手段】幹線信号用の第1の入力端子31及び分岐信号用の第2の入力端子32と、第1の出力端子33及び第2の出力端子34との間に第1〜第4のスライドスイッチ35a〜35dを設け、出力端子33、34の信号出力状態を端子仕様1又は2に切替えられる構成とする。スライドスイッチ35a、35dの信号出力端間に電流方向によって点灯又は消灯する発光ダイオード67、68を設け、スライドスイッチ35cの信号入力側に発光ダイオード53を設ける。スライドスイッチ35aの信号入力側から直流電源E1を供給し、スイッチ設定が正しい場合は発光ダイオード67、68の一方を駆動して端子仕様を表示し、スイッチ操作を誤った場合は発光ダイオード53を駆動してエラー表示する。

(もっと読む)

半導体装置

【課題】シングルエンド−差動変換器を備えた半導体装置において、理想的な出力差動電流特性が得られる周波数の上限を向上させる。

【解決手段】入力電圧Vinを、パッケージ3の外部電極PIN1に入力し、外部電極PIN1、ボンディングワイヤWire1、チップ2の入力端子PAD1、シングルエンド−差動変換器1の入力端子Tin1を介してゲート接地のMOSトランジスタM1のソースに伝達する。また、外部電極PIN1、ボンディングワイヤWire2、チップ2の入力端子PAD2、シングルエンド−差動変換器1の入力端子Tin2を介してソース接地のMOSトランジスタM2のゲートに伝達する。

(もっと読む)

可変出力増幅器

【課題】低出力時の回路損失を低減し、低出力時の効率を高める可変出力増幅器を得る。

【解決手段】トランジスタ5と共に並列接続されたトランジスタ11と、信号出力される平均電力レベルを所定の値よりも小さくするときには、トランジスタ5のみ動作するようにバイアス電圧を印加し、信号出力される平均電力レベルを所定の値よりも大きくするときには、トランジスタ5,11の両方が動作するようにバイアス電圧を印加するバイアス制御回路12とを備えた。

このように構成したことにより、低出力時および高出力時に関わらずバイパス経路を用いずに、トランジスタ5,11の信号出力をそのまま出力するため、低出力時の回路損失を低減し、低出力時の効率を高めることができる。

(もっと読む)

増幅器

【課題】省電力化を実現することができる増幅器を提供する。

【解決手段】高周波信号を増幅する増幅手段と、前記増幅手段により高周波信号を増幅する第1の選択肢を含み、かつ、前記増幅手段をパスして高周波信号を伝送する第2の選択肢と高周波信号の伝送をカットする第3の選択肢の少なくともいずれかを含む複数の選択肢の中から一つを選択する選択手段と、特定の回路と、を備え、前記第1の選択肢が前記選択手段により選択された場合、前記増幅手段に直流電源から電源電流が供給されると共に、前記供給された電源電流は前記増幅手段を介して前記特定の回路に供給され、前記第2の選択肢及び/または前記第3の選択肢が前記選択手段により選択された場合、前記直流電源から前記特定の回路に電源電流が供給される構成とする。

(もっと読む)

増幅装置、送信機、及び増幅装置制御方法

【課題】電流が規定値を維持する増幅装置、送信機、及び増幅装置制御方法を提供する。

【解決手段】電力増幅装置100は、RF増幅用GaNデバイス118と、モニタ用GaNデバイス106と、Idq検出回路112と、ゲートバイアス制御(GBC)回路119とを有する。RF増幅用GaNデバイス118は、入力信号を増幅して出力する。モニタ用GaNデバイス106は、RF増幅用GaNデバイス118の入出力信号をモニタするための増幅デバイスである。Idq検出回路112は、RF増幅用GaNデバイス118に入力される入力信号から分岐してモニタ用GaNデバイス106に入力される入力信号に対応し、モニタ用GaNデバイス106が出力する出力信号を、検出する。ゲートバイアス制御回路119は、Idq検出回路112により検出された出力信号に応じて、RF増幅用GaNデバイス118に印加するゲート電圧を制御する。

(もっと読む)

増幅回路ならびにそれを用いた送信装置および通信装置

【課題】 デューティ比が変化する入力信号を高効率で増幅することが可能な増幅回路ならびにそれを用いた送信装置および通信装置を提供する。

【解決手段】 デューティ比が変化するパルス波状の第1信号が入力されて、第1信号を増幅した第2信号を出力するトランジスタ回路10と、第2信号が入力されて、第1信号の基本波と周波数が等しい第3信号を出力する出力回路30とを有しており、出力回路30は、第1信号の基本波の周波数を含む通過帯域を有するとともに、第1信号のデューティ比が小さくなるにつれて通過帯域の幅が大きくなる帯域通過フィルタ31と、帯域通過フィルタ31とトランジスタ回路10とのインピーダンスを整合させる整合回路とを有する増幅回路ならびにそれを用いた送信装置および通信装置とする。デューティ比が変化する入力信号を高効率で増幅できる増幅回路ならびに消費電力が小さい送信装置および通信装置を得ることができる。

(もっと読む)

高周波電力増幅器

【課題】インピーダンス整合の切り替えと経路の切り替えを同時に行うことができ、回路設計の自由度を向上させることができる高周波電力増幅器を得る。

【解決手段】トランジスタTr1は、外部から入力された高周波信号を増幅する。トランジスタTr2は、トランジスタTr1の出力信号を増幅する。トランジスタTr3は、トランジスタTr1と並列に接続され、外部から入力された高周波信号を増幅する。トランジスタTr1の出力とトランジスタTr2の入力との間に切り替え素子SW1が接続されている。トランジスタTr3の出力と切り替え素子SW1との間に切り替え素子SW2が接続されている。トランジスタTr1の出力及び切り替え素子SW2とトランジスタTr2の出力との間に切り替え素子SW3,SW4が直列に接続されている。切り替え素子SW3と切り替え素子SW4との間にキャパシタC1が接続されている。

(もっと読む)

集積されたパワー増幅器を有するCMOSトランシーバ

【課題】通信信号を増幅する絶縁破壊に耐えるトランジスタ構造を提供する。

【解決手段】入力無線周波数信号を受信するため接地点と第1のゲートに接続されたソースを有する第1のNMOSトランジスタ12は、第1のトランスコンダクタンスと第1の破壊電圧とを有する。また第2のNMOSトランジスタは、第1のNMOSトランジスタのドレインに接続されたソースと、基準DC電圧に接続されたゲートと、増幅された無線信号の出力を与えるドレインと、基準DC電圧と第2のNMOSトランジスタのドレインとの間に配置された負荷とを有する。第2のNMOSトランジスタ14は第2のトランスコンダクタンスと第2の破壊電圧とを有し、第2の絶縁体は第1の絶縁体よりも厚い。この結果、第1のトランスコンダクタンスは第2のトランスコンダクタンスよりも大きく、第2の破壊電圧は第1の破壊電圧よりも大きい。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

容量性負荷駆動回路及び流体噴射装置

【課題】上限あるいは下限付近のデューティー比でも効率よく容量性負荷を駆動する。

【解決手段】容量性負荷駆動回路は、駆動信号COMの基準となる駆動波形信号WCOMを発生する駆動波形信号発生回路210と、WCOMをパルス変調して変調信号MCOMを生成する変調回路230と、MCOMを電力増幅して電力増幅変調信号ACOMを生成するデジタル電力増幅器240と、複数のインダクター251と複数のインダクター251の少なくともひとつを選択可能な接続手段252で構成され、かつACOMを平滑化することによってCOMを生成する平滑フィルター250と、デジタル電力増幅器240から平滑フィルター250に流れる電流の方向がMCOMの一変調周期内で逆転する逆転条件下では、一変調周期内での電流の最大値及び最小値の絶対値が所定の閾値以上となるように、接続手段252における選択を切り替える切替制御部270とを含む。

(もっと読む)

分布形増幅器

【課題】利得の低下を防止して、高利得、高出力、高効率及び広帯域特性を実現することができる分布形増幅器を得ることを目的とする。

【解決手段】並列に接続されている複数のトランジスタ1a〜1jと、複数のトランジスタ1a〜1jに対して入力側バイアス電圧を供給する電圧源2と、複数のトランジスタ1a〜1jに対して出力側バイアス電圧を供給する電圧源5,7とを備え、電圧源5,7から複数のトランジスタ1a〜1jに供給される出力側バイアス電圧のうち、トランジスタ1aに供給される出力側バイアス電圧が、トランジスタ1b〜1jに供給される出力側バイアス電圧と異なるように構成する。

(もっと読む)

広帯域マイクロ波増幅器

【課題】クラスEのHPAが広い帯域幅にわたって同時に高いPAE及び電力を維持することを可能にする。

【解決手段】スイッチングモード電力増幅器の出力に結合されたシャント誘導素子と、前記増幅器の前記出力に結合されている直列の誘導素子と、前記直列の誘導素子に結合されている直列の容量素子とを含む構成とした。

(もっと読む)

電力増幅器

【課題】 オフセット補正後の電力増幅器の動作開始時に電力増幅器に接続されたスピーカからポップ音が発生するのを防止する。

【解決手段】 直流電圧発生回路170は、D級増幅器内の差動増幅器のオフセットキャンセルを行わせるためにD級増幅器の出力端子T21およびT22に直流電圧を供給する。この直流電圧発生回路170の出力端子T30と接地線との間には放電用抵抗RDISとNチャネルトランジスタ183が介挿されている。オフセットキャンセルが終わった後、D級増幅器の増幅動作が開始される前の安定期間に、Nチャネルトランジスタ183はONとされ、出力端子T21およびT22に接続された容量C1およびC2の充電電荷が放電用抵抗RDISおよびNチャネルトランジスタ183を介して放電される。これによりポップ音の発生を防止することができる。

(もっと読む)

差動増幅回路

【課題】基本波周波数のゲイン変化を生じさせることなく、2次高調波のみを抑圧および低減した回路面積の小さい差動増幅回路の実現。

【解決手段】差動対をなし、差動信号S,ZSが入力される2個のMOSトランジスタTr1,Tr2と、2個のMOSトランジスタTr1,Tr2のドレイン間に直列に接続された2個の容量素子C1,C2と、2個の容量素子C1,C2の接続ノードとバイアス電源端子GND間に接続されたインダクタンス素子L1と、を有する差動増幅回路。

(もっと読む)

高周波増幅回路

【課題】低出力モードで出力電力を変化させても、ゲインの差が殆ど生じない高周波増幅回路を実現する。

【解決手段】高周波増幅回路100Aは増幅用トランジスタ10を備える。増幅用トランジスタ10のベースは、バラスト抵抗素子52を介してエミッタフォロワ用トランジスタ20のエミッタに接続する。エミッタフォロワ用トランジスタ20のベースには、抵抗素子51を介してバイアス電源が接続されている。エミッタフォロワ用トランジスタ20のコレクタには、抵抗素子53を介してモード制御電源が接続されている。抵抗素子53は固定抵抗値の抵抗素子である。モード制御電源は、可変電圧型であり、モードに応じて直流のモード制御電圧Vmodeを発生する。モード制御電圧Vmodeは、低出力モード時には低電圧となり、高出力モード時には高電圧となる。

(もっと読む)

電力増幅装置、電力増幅装置の入力バイアス電圧調整方法

【課題】入力バイアス電圧の調整の時間的効率を大幅に向上することができる電力増幅装置および電力増幅装置の入力バイアス電圧調整方法を提供すること。

【解決手段】バイアス電圧供給部は、GaN−FETのゲートにバイアス電圧を与える。演算制御部は、異なる時点の負荷電流の差を算出する。参照テーブルは、GaN−FETに対応して定められている、ゲートソース間電圧を一定に保ち始めたときからドレイン電流が変化していく当初のドレイン電流変化率と、ゲートソース間電圧を一定に保ち始めたときのドレイン電流を時間経過後に保つため必要なゲートソース間電圧の変更量との対応関係を記述している。参照制御部は、負荷電流の差を参照テーブルのドレイン電流変化率に当てはめて、ゲートソース間電圧の変更量を取り出す。バイアス電圧変更制御部は、変更量に基づいて、ゲートバイアス電圧を変更するように、バイアス電圧供給部を制御する。

(もっと読む)

61 - 80 / 1,197

[ Back to top ]