Fターム[5J500AS00]の内容

増幅器一般 (93,357) | 用途 (4,306)

Fターム[5J500AS00]の下位に属するFターム

プリアンプ(前置増幅器) (138)

イコライザ(任意の周波数特性) (7)

マルチアンプ (3)

オーディオアンプ (877)

車載機器 (58)

映像機器 (236)

磁気記録再生用アンプ (31)

サーボアンプ (15)

ブースター (5)

通信機器 (2,560)

試験、測定器 (166)

スイッチング用 (38)

Fターム[5J500AS00]に分類される特許

81 - 100 / 172

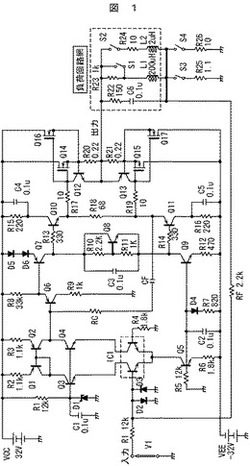

演算増幅器及びそれを用いた走査電子顕微鏡

【課題】高電圧・大電流を扱うことができ、安定且つ精密な増幅が可能な演算増幅器、及び走査電子顕微鏡を提供する。

【解決手段】差動対と、当該差動対にカスコード接続されたベース接地増幅回路と、アクティブ負荷を含む初段増幅部と、エミッタフォロア回路と定電流負荷回路を備えたインバータを含む2段目増幅部と、ソースフォロア回路又はエミッタフォロア回路を含む3段目増幅部を備えた演算増幅器。

(もっと読む)

基準電圧発生回路およびそれを内蔵した半導体集積回路

【課題】 低電圧で電圧変動が比較的大きい電源電圧であっても温度依存性がなくかつ精度の高い基準電圧を生成することが可能であり、特に無線タグICに内蔵するのに好適な基準電圧発生回路を提供する。

【解決手段】 電源電圧依存性のない電流を流す第1の定電流源(Mp3)と直列に第1のMOSFET(Mn3)を接続し、第1の定電流源が流す電流は該第1のMOSFETを飽和領域で動作させる大きさとし、第1のMOSFETとカレントミラー接続されて第1の定電流源と同一の電流を流す第2の定電流源として作用する第2のMOSFET(Mn4)を設ける。そして、該第2のMOSFETと直列に第1のMOSFETのしきい値電圧よりも小さなしきい値電圧を有する第3のMOSFET(MnL1)を接続して、第2のMOSFETと第3のMOSFETとの結合点から、上記第1のMOSFETと第3のMOSFETのしきい値電圧差に相当する電圧を取り出すように基準電圧発生回路を構成した。

(もっと読む)

半導体集積回路装置

【課題】低電圧化と高速動作化を実現した差動増幅回路を提供する。

【解決手段】一対の第1入力端子にそれぞれゲートが接続された第1及び第2導電型の第1及び第2差動MOSFET対の第1共通ソースにそれぞれ第1及び第2容量手段及び第1及び第2導電型の第1及び第2電流源MOSFETを設けて第1及び第2増幅部を構成する。上記第1及び第2差動MOSFET対に流れる電流をそれぞれ供給する第2及び第1導電型の第1及び第2MOSFET対及び上記第1及び第2MOSFET対のそれぞれに直列形態にされた第2及び第1導電型の第3及び第4MOSFET対により第1及び第2出力部を構成する。上記第3MOSFET対と第4MOSFET対の対応するドレイン同士を接続して一対の出力端子とし、上記第1及び第2電流源MOSFET並びに上記第1ないし第4MOSFETのゲートにバイアス電圧を供給する。

(もっと読む)

コンパレータ回路

【課題】入力電圧の比較可能レベルを広げ、かつ比較レベルによる判定時間の変動、入力からみた出力に対する比較精度の変動を抑えられるコンパレータ回路の提供。

【解決手段】第1差動増幅回路11は、入力電圧Vin+、Vin−の差に応じた電流を出力する。ソースフォロワ回路18は、入力電圧Vin+、Vin−を電圧SV+、SV−にレベルシフトする。第2差動増幅回路12は、その電圧SV+、SV−の差に応じた電流を出力する。受け渡し回路16は、入力電圧Vin+、Vin−の動作コモン電位レベルに応じて第1差動増幅回路1と第2差動増幅回路2の動作を切り替える。電流電圧変換回路15は、第1差動増幅回路11の出力電流と第2差動増幅回路12の出力電流とを加算し、その加算に応じた出力電圧Vout を出力する。

(もっと読む)

カレントミラー回路、電流制御回路、および、LED駆動用半導体集積回路

【課題】 非常に高い精度のミラー比を実現できるカレントミラー回路を提供する。また、駆動電流を非常に高い精度で制御することのできるLED駆動用半導体集積回路を提供する。

【解決手段】 カレントミラー回路において、転写元の電流を流す第1電流経路(L0)と、転写先の電流を流す第2電流経路(L1)と、制御端子への入力により電流量を変化させるとともに互いの制御端子が結合された第1電流回路(M1,M2)および第2電流回路(M3,M4)と、第1電流経路(L0)と第2電流経路(L1)の接続を前記第1電流回路と前記第2電流回路とで互い違いに切り換えるスイッチ回路(SW1,SW2)と、第1および第2電流回路の制御端子の接続を切り換えるスイッチ回路(SW3,SW4)とを備え、これらスイッチ回路を所定周期で切り換えるように構成した。また、LED駆動用半導体集積回路において駆動電流を生成するために、上記のカレントミラー回路を基準電流を転写する回路として用いた。

(もっと読む)

差動増幅器、差動増幅方法、及びこれを利用した位相固定ループ、並びに遅延同期ループ

【課題】位相固定ループ(PLL)又は遅延同期ループ(DLL)に使用される場合、出力信号のデューティ比の歪曲を減少させること。

【解決手段】差動増幅器は、入力端710、バイアス部720、及び負荷部730を含む。入力端は、奇数個の位相信号のうち、第1位相信号(Clki)と、前記奇数個の位相信号のうち少なくとも2つの位相信号(Clkib,Clkibr)の位相の平均値が前記第1位相信号に対して実質的に180°の差異を有する前記少なくとも2つの位相信号とを受ける。バイアス部は、前記入力端と第1電源電圧との間に連結される。負荷部は、前記入力端と第2電源電圧との間に連結され、前記第1位相信号と前記少なくとも2つの位相信号とを差動増幅した差動出力信号(out,outb)を出力する。

(もっと読む)

トランスインピーダンスアンプ

【課題】 回路規模が小さい出力電圧制限回路を備えたトランスインピーダンスアンプを提供する

【解決手段】 光信号を受信して電流を発生させる光検出素子4と、反転入力端子に光検出素子の出力端子を、非反転入力端子1に参照電圧Vrefを、それぞれ接続した差動増幅器2と、差動増幅器2の出力端子に接続されたバッファ回路3と、差動増幅器2の出力電圧が所定の値を超過したとき、差動増幅器2の出力端子から差動増幅器2の反転入力端子へ制限電流を流す出力電圧制限回路と、バッファ回路3の出力端子と光検出素子4の出力端子との間に接続された抵抗5からなり、出力電圧制限回路は、差動増幅器2の出力端子にアノードを、差動増幅器2の反転入力端子にカソードを、それぞれ接続したダイオード7で構成する。

(もっと読む)

出力回路およびそれに用いられる定電流源回路

【課題】上限クランプ電圧を電源電圧近傍にしつつ、下限クランプ電圧をより小さな値にできる出力回路を提供する。

【解決手段】出力電圧VOUTをフィードバックすることで定電流源回路7が形成する定電流I4の大きさを出力電圧VOUTに応じて変化させるようにし、出力電圧VOUTが小さい場合には、定電流源回路7をOFFさせて定電流I4がゼロとなるようにする。これにより、出力電圧VOUTをGND(ゼロ)に近い値とすることが可能となる。このため、高周波除去用のフィルタ回路9の影響で下限クランプ電圧が低くできなくなることを防止でき、従来よりも下限クランプ電圧をGND(ゼロ)に近い値にすることが可能となる。

(もっと読む)

オフセットキャンセル装置

【課題】オフセット補償の動作中に信号出力を行うことができ、またオペアンプに外部接続された容量素子や抵抗素子によるオフセットを補償するオフセットキャンセル装置を提供。

【解決手段】駆動回路10は、複数の出力端子(#1〜#n) 12に対しそれぞれ駆動信号を一方の出力14から出力する複数の出力回路(#1〜#n+1) 16を備え、他方の出力18から駆動信号を出力する。出力14と出力18とは複数の出力選択回路(#1〜#n)20に接続され、互いに隣接する2つの出力回路14から出力される信号のいずれかが選択されて、選択した信号が出力端子12に出力される。出力回路(#1〜#n+1) 16の他方の出力18は判定回路30に接続され、判定回路30は、信号18と基準電圧とを比較し、比較結果に応じた判定信号を所定のタイミングにて出力40に出力し、出力回路16はこの出力40に応じてオフセットキャンセル動作を行う。

(もっと読む)

サンプルホールド増幅回路、相関二重サンプリング回路

【課題】消費電流及び回路実装面積を低減すると共に、前の信号処理がその後の信号処理に影響を与えることのないサンプルホールド増幅回路を提供する。

【解決手段】CCD出力信号CDSINのフィードスルー期間に同期したSHP信号でスイッチS11が閉じ、サンプリング用コンデンサC11にフィードスルーレベルをサンプルホールドする。同時に、SHP信号でスイッチS12及びスイッチS15を閉じて、差動増幅器A11及びインバータA12をリセットする。CDSINのデータ期間では、SHHバー信号でスイッチS13が閉じて差動増幅器A11とインバータA12を接続すると共に、SHHバー信号でスイッチS14を閉じ、データレベルとサンプルホールドしたフィードスルーレベルの差分を、サンプリング用コンデンサC11及びアンプ用コンデンサC12の各容量CS、CAの比、CS/CA倍に増幅する。

(もっと読む)

電圧電流変換回路及びアナログフィルタ回路

【課題】寄生容量を変化させずに出力電流を停止する。

【解決手段】所定の定電流を供給する第1(12,14)及び第2電流源(11,13)と、前記第1電流源と直列に接続され、制御電極に第1入力電圧(Vin−)が印加される第1トランジスタ(18)と、前記第2電流源と直列に接続され、制御電極に第2入力電圧(Vin+)が印加される第2トランジスタ(17)とを有し、前記第1入力電圧及び前記第2入力電圧に応じて動作する差動回路と、を備え、前記第1電流源と前記第1トランジスタとの間から、前記第1電流源から供給される前記定電流と、前記第1トランジスタを流れる電流とに応じた第1出力電流(Iout+)を出力する電圧電流変換回路であって、前記第1トランジスタの入力電極と、前記第2トランジスタの入力電極とを電気的に接続することにより前記第1出力電流を停止するスイッチ回路を、更に備える。

(もっと読む)

差動増幅回路、レシーバ回路、発振回路及びドライバ回路

【課題】立ち上がり時の遅延時間と立下り時の遅延時間との差を小さくすることができる差動増幅回路と、これを用いたレシーバ回路、発振回路及びドライバ回路を提供する。

【解決手段】差動入力信号の極性が正負の何れに変化する場合でも、ノードN31及びN32bに発生するバイアス電圧がほぼ一定になり、各カスコード部のNチャンネル側の負荷トランジスタ(MN21,MN22,MN21b,MN22b)には常に電流が流れた状態になる。これにより、ノードN31及びN32bの充放電に要する時間が非常に短くなるため、非反転出力信号O(+)及び反転出力信号O(−)の立ち上がり時の遅延時間と立下り時の遅延時間をほぼ等しくすることができる。これにより、入力信号のパルス幅と出力信号のパルス幅がほぼ同じになり、高速な回路への適用が可能になる。

(もっと読む)

増幅回路及びそれを用いた物理量センサ

【課題】 センサ素子の温度特性を相殺する温度特性を有し、周囲の温度変化に関わらず一定の出力を得る増幅回路を提供する。

【解決手段】 温度特性を有するセンサ素子2からの検出信号V1を入力する演算増幅器5と、この演算増幅器5の入力端に接続される入力抵抗と、演算増幅器5の出力端と入力端との間に接続される帰還抵抗とを有し、入力抵抗及び帰還抵抗は、n型ポリシリコン抵抗とp型ポリシリコン抵抗とを所定の比率で組み合わせる構成とした。これにより、センサ素子の温度特性を相殺し、温度変化に対して一定の出力を得る増幅回路を実現出来る。

(もっと読む)

制御用増幅回路

【課題】温度変動に伴う差動増幅器のオフセット電圧変動に起因する制御誤差を抑制でき、レーザダイオードパワー制御等に用いる制御用増幅回路を提供する。

【解決手段】フォトダイオード22の検知信号が入力される電流電圧変換回路23には、参照電源側にプッシュプル回路27が接続される。プッシュプル回路27では、電流電圧変換回路のオフセット電圧の温度特性に応じて、NPN型トランジスタ対16,17及びPNP型トランジスタ対18、19のエミッタ面積比が設定される。その結果、差動増幅器の温度変化に起因するオフセット電圧変動は、プッシュプル回路27の参照電圧によってキャンセルされ、出力回路Voutへは適正な電圧が送られる。

(もっと読む)

差動増幅回路

【課題】 出力電圧の反転を防止するとともに、入力電圧範囲を広くすることができる差動増幅回路を提供する。

【解決手段】 第1の入力信号をベースに入力する第1のトランジスタと、第2の入力信号をベースに入力する第2のトランジスタと、第1の電源電位に接続し、第1および第2のトランジスタに電流を供給する電流源とからなる差動回路と、第1のトランジスタのコレクタにエミッタを、第2電源電位にベースを接続した第3のトランジスタと、第3のトランジスタのコレクタと第2電源電位との間に接続した第1の負荷と、第2のトランジスタのコレクタと第2電源電位との間に接続した第2の負荷と、第3のトランジスタのコレクタに接続した第1の出力端子とで構成する。

(もっと読む)

演算増幅器

【課題】

入力抵抗素子の抵抗値が可変の演算増幅器において、入力端子に接続されたC結容量と前記入力抵抗素子とでハイパスフィルターが構成された場合に、前記ハイパスフィルターのカットオフ周波数を一定にできるようにする。

【解決手段】

基準電源106からの基準電圧を差動入力増幅器101の一方の入力端子に入力する。抵抗値が可変で一方の端子が差動入力増幅器101の他方の入力端子に接続された入力抵抗素子、および前記入力抵抗素子の他方の端子と直列に接続された容量素子によってハイパスフィルターを構成する。そして、前記入力抵抗素子の前記他方の端子に接続され、前記入力抵抗素子の抵抗値に応じて、オンオフが切り替わるアナログスイッチを介して、電流源107から前記入力抵抗素子に一定の電流を出力する。

(もっと読む)

交流増幅器及び圧電振電子発振器

【課題】

交流増幅器の低電圧動作を損なうことなく、消費電流を低減でき、かつ出力信号波形のデュティーのずれが少なく、更に十分な増幅特性を有する交流増幅器を提供する。

【解決手段】 連結配線Ndで結ばれた増幅回路AP1とバイアス回路VS1を有し、バイアス回路VS1は前記連結配線Ndを介して前記増幅回路AP1の前記交流信号を入力し、増幅回路AP1の交流信号の振幅に応じたバイアス回路VS1の直流電圧を連結配線Ndを介して増幅回路AP1へ供給する交流増幅器とした。

(もっと読む)

演算増幅回路および電子情報機器

【課題】 演算増幅器の出力が負荷電流により変動した場合であっても、従来のように出力電流を検出することなく、より安定した出力電圧を負荷に供給する。

【解決手段】 演算増幅回路10Aの出力端と接地間に負帰還抵抗R1およびR2を2個直列接続してその間から差動増幅器2に負帰還すると、その利得が(1+R1/R2)倍とすることができる。この演算増幅回路10Aの出力端と接地間に直列に接続された負帰還抵抗R1およびR2を切り離し、負荷4の手前までの往復分の配線抵抗r1およびr2を含めて負帰還抵抗手段を構成することにより、負荷電流の増加分によって配線抵抗r1およびr2の電圧降下が大きくなった分だけ、差動増幅器2で利得制御されて利得を高くできるため、負荷電流による電位変動を低減することができて、従来のように出力電流を検出することなく、演算増幅回路10Aによる安定した出力電圧を得ることができる。

(もっと読む)

電子回路

【課題】カレントミラー回路では、電源電圧の変動によって動作が不安定になる場合があった。

【解決手段】電源電圧の変動に応じて、カレントミラー回路を構成するトランジスタのゲート電圧を電源電圧の変動と同様に変化させる安定化回路をカレントミラー回路に接続する。安定化回路はフィルタ回路と、カレントミラー回路を安定に作動させるための安定化電流を供給するトランジスタによって構成できる。

(もっと読む)

増幅回路

【課題】低消費電流でより高速な増幅回路を提供すること。

【解決手段】差動入力される電圧電流変換増幅器と、node1とVddの間に接続される第1の電流源と、node1にドレイン端子が接続されゲート端子に第1のバイアス電圧が印加される第1導電型の第1のトランジスタと、node2とVssの間に接続される第2の電流源と、node1にソース端子が接続されnode2にドレイン端子が接続されゲート端子に第2のバイアス電圧が印加される第2導電型の第2のトランジスタと、node1にゲート端子が接続され出力端子にドレイン端子が接続されVddにソース端子が接続される第2導電型の第3のトランジスタと、node2にゲート端子が接続され出力端子にドレイン端子が接続されVssにソース端子が接続される第1導電型の第4のトランジスタと、第1の電流源又は第2の電流源は前記増幅器により電流量を制御する電流量制御手段とを有する。

(もっと読む)

81 - 100 / 172

[ Back to top ]