Fターム[5J500AS00]の内容

増幅器一般 (93,357) | 用途 (4,306)

Fターム[5J500AS00]の下位に属するFターム

プリアンプ(前置増幅器) (138)

イコライザ(任意の周波数特性) (7)

マルチアンプ (3)

オーディオアンプ (877)

車載機器 (58)

映像機器 (236)

磁気記録再生用アンプ (31)

サーボアンプ (15)

ブースター (5)

通信機器 (2,560)

試験、測定器 (166)

スイッチング用 (38)

Fターム[5J500AS00]に分類される特許

21 - 40 / 172

D級増幅器

【課題】変調信号のパルスデューティーに対して電力増幅後のパルス信号のパルスデューティーに生じる誤差を防止し、ローパスフィルター等で復調された駆動信号の歪を防ぐことが可能なD級増幅器を提供する。

【解決手段】D級増幅器100は、出力する駆動信号8の基準となる駆動波形信号5の振幅値に基づいてパルス変調して変調信号6を出力する変調回路1と、変調回路1で変調された変調信号6を電力増幅して電力増幅変調信号7を出力するデジタル電力増幅回路2と、デジタル電力増幅回路2で電力増幅された電力増幅変調信号7を平滑化し、駆動信号8を出力する平滑フィルター3と、を備えたD級増幅器であって、変調回路1は、駆動波形信号5の振幅値と電力増幅変調信号7のパルスデューティーが線形特性となるように予め備えられた補正テーブル4に基づいて、変調信号6のパルスデューティーを補正することを特徴とする。

(もっと読む)

クラス特性可変増幅器

半導体装置及び電子機器

【課題】負荷(EL画素や信号線)に電流を供給するトランジスタにおいて、バラツキの影響を受けずに正確な電流を供給できる半導体装置を提供する。

【解決手段】増幅回路を使ったフィードバック回路を用いて、トランジスタの各端子の電圧を調節する。電流源回路から電流Idataをトランジスタに入力して、トランジスタが電流Idataを流すのに必要なゲート・ソース間電圧を、フィードバック回路を用いて設定する。フィードバック回路は、トランジスタが飽和領域で動作するように制御する。すると、電流Idataを流すのに必要なゲート電圧が設定される。そして、設定されたトランジスタを用いれば、正確な電流を負荷(EL画素や信号線)に供給できる。なお、必要なゲート電圧を設定するとき、増幅回路を用いるので、すばやく設定できる。

(もっと読む)

差動増幅回路及びA/D変換器

【課題】電源電圧が比較的小さい場合においても、性能劣化を起こさず、かつオーバードライブリカバリ可能な差動増幅回路を得る。

【解決手段】第1の出力部であるノードN1と電源Vddとの間にPMOSトランジスタMP1及びMP3が互いに並列に介挿され、第2の出力部であるノードN2と電源Vddとの間にPMOSトランジスタMP2及びMP4が互いに並列に介挿される。レプリカ回路4及びコンパレータ5によって、入力電圧Vinと基準電圧Vrefとの入力電位差が“0”のバランス状態時の出力電圧Voutp及びVoutnは共に基準出力コモン電圧Voutcm_idealに設定される。電源電圧Vddと出力コモン電圧Voutcmとの電位差がダイオード接続されたPMOSトランジスタMP1及びMP2の閾値電圧Vthよりも低い値となるように、レプリカ回路4の基準出力コモン電圧Voutcm_idealを設定する。

(もっと読む)

電流源、電流源回路、およびこの電流源回路の使用

【課題】MOS技術を使ったパワー素子を用いなくても、正確な負荷電流を供給しうる電流源を提供する。

【解決手段】電流源10が、制御端子および制御パスを有するバイポーラトランジスタ1と、バイポーラトランジスタ1の制御パス上にあって、電気負荷D1と接続される第1の端子と、抵抗器4経由で基準電源端子と接続される第2の端子と、バイポーラトランジスタ1の制御端子に接続され、この制御端子に送られる制御電流を測定する測定装置2と、バイポーラトランジスタ1の制御電流が制御パス上に位置する第1の端子において補償されるように、測定装置2およびバイポーラトランジスタ1に接続された補償電流源3とを備える。

(もっと読む)

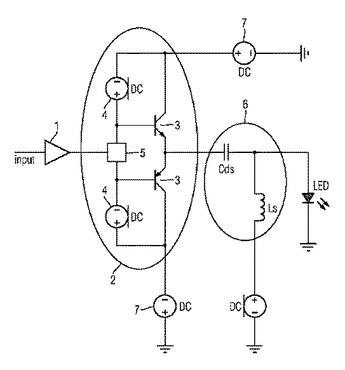

高い出力性能とコンパクトな構造を有する広帯域高線形性LED増幅器

本発明は、発光ダイオードを駆動制御する増幅回路に関する。この増幅回路は、約3オームの小さい出力インピーダンスと、200KHzの下方境界周波数と例えば5MHzの上方境界周波数とを備えた広い帯域幅と、例えば数100mAの出力電流振幅とを有する。この増幅回路は、直流電流供給部(6)によって発光ダイオードを駆動制御するドライバー回路(2)を駆動制御する入力段を有している、という特徴を有している。  (もっと読む)

(もっと読む)

増幅素子

【課題】ECMのインピーダンス変換および増幅に、J−FETを入力としバイポーラトランジスタを出力とする増幅素子に、バックゲート構造のJ−FETを用いると、バックゲート−半導体基板間の容量が、増幅素子の入出力間の寄生容量(ミラー容量)となり、増幅素子の入力ロスが増大する問題に対し有効な半導体装置を提供する。

【解決手段】接地されたp型半導体基板11にp型半導体層12を積層し、p型半導体層12にn型チャネル領域22を有するJ−FETと、n型コレクタ領域33bを有するバイポーラトランジスタを設けた増幅素子とする。これにより、増幅素子の入出力間の寄生容量が発生しなくなるため、ミラー容量による入力ロスの増大を防止できる。また、J−FETのチャネル領域は、エミツタ拡散31と同時に形成できるため、IDSSSや、ピンチオフ電圧が安定し、増幅素子としての消費電流のばらつきが低減し、生産性が向上する。

(もっと読む)

センサ信号処理回路

【課題】大きな入出力ダイナミックレンジを確保しなくても十分な利得を確保し、かつ十分な周波数帯域によりセンサの出力信号を増幅できるようにする。

【解決手段】センサ信号処理回路11より交流結合容量を削除すると共に、出力信号Voutからローパスフィルタ(R2、C1)により直流成分を分離し、この直流成分と基準電圧Vrefとの差電圧に応じた直流電流を入力側に電流帰還する。

(もっと読む)

増幅回路及びこれを備える光ピックアップ

【課題】増幅回路の応答速度等を改善する。

【解決手段】増幅回路1bは、入力信号が供給される差動増幅回路20と、差動増幅回路20の出力を受けるソースフォロア回路30と、ソースフォロア回路30の出力端E、差動増幅回路20の入力端S、差動増幅回路20の出力端とソースフォロア回路30の入力端Sの間の中間端点Mのそれぞれと接続される複数の帰還経路ブロック40を備える。各帰還経路ブロック40において、抵抗16およびキャパシタ17の一端は、選択スイッチ18を介して入力端Sと接続され、抵抗16の他端は出力端Eに接続され、キャパシタ17の他端は中間端点Mに接続されている。そして、中間端点Mから帰還経路ブロック40−2、40−3のキャパシタ17−2、17−3に至る経路に解放スイッチ70が間挿される。

(もっと読む)

増幅器を安定化する方法およびシステム

【課題】増幅器を安定化する方法を提供すること。

【解決手段】本発明は、一般に、増幅器を安定化することに関する。一局面においては、増幅器と電気通信する安定化モジュールが提供される。安定化モジュールは、開ループ制御システムおよび閉ループ制御システムの両方を含む。開ループ制御システムは、安定化モジュールによって受信される入力信号の少なくとも1つの特性を修正し、制御を閉ループ制御システムに渡すために使用される。閉ループ制御システムは、次いで、入力信号の少なくとも1つの特性を修正するために使用される。修正された入力信号は、増幅器に提供される。

(もっと読む)

ディザ追加型増幅器

アナログ増幅器は、少なくとも1つの信号経路を具備する。上記少なくとも1つの信号経路の各々は、入力端子と出力端子との間に延びるとともに、出力端子に接続された負荷デバイスと入力端子に接続されたトランジスタとを具備する。上記アナログ増幅器は、上記少なくとも1つの信号経路に選択的に接続されたディザ電流源を更に具備する。上記ディザ電流源は、選択された信号経路のトランジスタをバイパスすることによって、選択された信号経路の負荷デバイスに対してディザ電流を直接供給することができる。  (もっと読む)

(もっと読む)

高電圧出力ドライバーおよび圧電ポンプ

【課題】圧電素子等の素子の駆動信号を効果的に得る。

【解決手段】駆動波形発生手段であるD/Aコンバータ30は、外部から供給される制御電源電圧であって、その電圧が圧電素子等の素子の駆動状態を示す制御電源電圧VCCを電源として素子の駆動波形を発生する。そして、この駆動波形を増幅することで、駆動信号を得る。従って、制御電源電圧に応じた振幅を有する、素子を駆動する駆動信号を得ることができる。

(もっと読む)

非反転増幅器、受光増幅素子および光ピックアップ素子

【課題】BD,DVD,CDの再生・記録に対応した光ピックアップのように、多段のゲイン切り替えが必要な場合においても、安定したゲイン切り替えを行うことができる非反転増幅器、受光増幅素子および光ピックアップ素子を提供する。

【解決手段】差動増幅回路に備えられる差動トランジスタ対Q1,Q2の入力側トランジスタQ1のコレクタ側にベース接地トランジスタQ3が挿入された非反転増幅器において、ベース接地トランジスタQ3のベースとベースが接続されたNPNトランジスタQ5のコレクタにベースが接続され、ベース接地トランジスタQ3のベースにエミッタが接続され、電源電位(Vcc)にコレクタが接続されたNPNトランジスタQ7を備えている。これにより、ゲイン切替時に増幅回路が差動増幅回路として機能しなくなり、出力が基準電圧より低い電位に固定された動作不能の状態になることを防ぐことができる。

(もっと読む)

液晶パネル駆動回路

【課題】異なる負荷容量を駆動可能としつつも、液晶パネルへ出力する駆動信号のセトリング時間を改善することができる液晶パネル駆動回路を提供すること。

【解決手段】液晶パネルへ駆動信号を出力する複数のバッファアンプ部20のそれぞれを、オペアンプAMP1と、このオペアンプAMP1の出力ノードと反転入力ノードとの間に接続された第1スイッチSW1と、オペアンプAMP1の出力ノードに一端が接続された出力抵抗R1と、この出力抵抗R1の他端とオペアンプAMP1の反転入力ノードとの間に接続された第2スイッチSW2とにより構成する。そして、重い負荷の装置が接続されるときに第1モードに設定して第1スイッチSW1を短絡状態にし、軽い負荷の装置が接続されるときに第2モードに設定して第2スイッチSW2を短絡状態にする。

(もっと読む)

高周波電力増幅器および高周波電力増幅器を備えた高周波電力出力装置

【課題】高出力かつ大電力動作時でも出力電力の位相を正確に検出し、任意の位相に制御可能な高周波電力増幅器等を提供する。

【解決手段】

高周波電力増幅器は、入力端子を介して受け取った高周波電力信号を増幅する増幅器と、増幅器に入力される高周波電力信号に基づいて、増幅器から出力された高周波電力信号を直交検波し、同相および直交検波出力信号を出力する直交検波部と、同相および直交検波出力信号に基づいて増幅器から出力された高周波電力信号の位相を検出し、位相情報を出力する位相検出部と、外部から受け取った、設定すべき位相を示す設定位相情報および位相検出部から出力された位相情報に基づいて、位相を変化させるための制御信号を生成する位相制御部と、入力端子と増幅器との間に設けられ、制御信号に基づいて、増幅器に入力される高周波電力信号の位相を変化させる移相器とを備えている。

(もっと読む)

積分回路

【課題】入力端子の電圧範囲をより広くする。

【解決手段】トランジスタ11に流れる電流と比例した電流をトランジスタ13に流すように構成されたカレントミラー回路10と、トランジスタ11と直列に接続されたトランジスタ21と入力端子IN1に非反転入力端子が接続された演算増幅器24とを有し、入力端子IN1に印加される入力電圧Vinとともにトランジスタ21に流れる電流が増加するように構成された可変定電流回路20と、トランジスタ13と直列に接続され、このトランジスタ13との接続点に出力端子OUTが接続されたコンデンサ30を備えた非反転積分回路を構成する。

(もっと読む)

バイアス回路とこれを用いた増幅器

【課題】単純な回路構成で、かつ回路の誤差に起因する雑音が発生せず、しかも温度変動に対して良好な特性のバイアス用の電流を得る。

【解決手段】このバイアス回路は、電流I1を生成する電流源1と、温度の変化に伴い出力電流の特性が電流I1と交るように増加または減少するような温度対出力電流特性の電流I2を生成する電流源2と、電流源1から入力される電流I1を電圧V1に変換する電流電圧変換回路3と、電流源2から入力される電流I2を電圧V2に変換する電流電圧変換回路4と、電圧V1と電圧V2を比較し、比較結果に応じた電流I3を生成する比較回路5と、電流I3と電流I2を加算して電流電圧変換回路4へ入力する電流加算部6と、電圧V2をバイアス用の電流IDに変換する電圧電流変換回路7とを備える。

(もっと読む)

オフセットキャンセル回路及び表示装置

【課題】液晶或いは表示装置における駆動回路において、オフセット電圧を抑制し、なおかつ、高速に出力すること実現する。

【解決手段】差動対をなすトランジスタM1、M2に同時に入力電圧を与え、能動負荷をなす、M3、M4トランジスタをともにダイオード接続し、M3、M4のゲートに各々容量を備えることで、入力電圧に好適な動作電流、動作電圧を記憶しておき、次に、能動負荷をなす、M3のゲート−ドレイン間、M4のゲート−ドレイン間を非導通状態にして、M3、M4の各々の容量に蓄えられた電荷を保持する状態として、ボルテージフォロア状態で動作する。

(もっと読む)

コンパレータ回路

【課題】フォールデッドカスコード接続の差動増幅段を有するコンパレータにおいて、オフセットの温度依存性を減らし検出精度を向上させる。

【解決手段】ソース共通接続された一対の差動MOSトランジスタを有する差動入力段(11)と、差動MOSトランジスタのドレイン端子にフォールデッドカスコード接続されたカスコード段(12)と、差動入力段とカスコード段に共通に接続された電流回路(Mn11〜Mn13,Mn21〜Mn23)と、カスコード段の出力ノードに接続された出力段(13)とを備えたコンパレータ回路において、前記電流回路は、カスコード段のMOSトランジスタのキャリア移動度の温度特性に起因する動作点の変動をキャンセルするような温度特性を付与された電流を流すように構成した。

(もっと読む)

差動増幅回路及びそれを用いた電源回路

【課題】オフセットが少なく、低ノイズの差動増幅回路及び電源回路を提供する。

【解決手段】本発明にかかる差動増幅回路は、反転入力端子IN−及び非反転入力端子IN+から入力される差動電圧を第1及び第2の電流I1、I2に変換する入力変換回路101と、第1の電流I1に対応する第3の電流I3と第2の電流I2との間で演算を行い、第4の電流I4を得る出力演算回路103と、反転入力端子IN−及び非反転入力端子IN+を同電位とするスイッチSW1と、反転入力端子IN−及び非反転入力端子IN+が同電位となった場合に出力演算回路103が第2及び第3の電流I2、I3間で演算を行ったときの電位を保持する容量Coffと、出力演算回路103から入力される第4の電流I4を外部に出力する出力バッファ回路104と、出力演算回路103から入力される第4の電流I4を記憶する容量Cbとを備える。

(もっと読む)

21 - 40 / 172

[ Back to top ]