Fターム[5J500DP01]の内容

Fターム[5J500DP01]に分類される特許

21 - 40 / 329

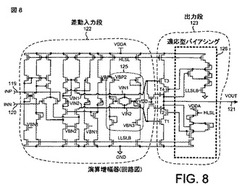

適応型バイアシングを用いた高スイング演算増幅器出力段

【課題】加工コストを増大させず、適応型バイアシング出力段を用いた高スイング演算増幅器を提供する。

【解決手段】出力段123は、VDDAノードと出力ノードとの間のプルアップ電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT3及びバイアシングトランジスタT4)を含み、前記出力ノードと接地ノードとの間のプルダウン電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT1及びバイアシングトランジスタT2)も含む。前記バイアシングトランジスタT4,T2を提供することは、前記トランジスタT3,T4において低下される最大電圧を低減させ、それによって前記トランジスタT1〜T4がVDDAよりも低い破壊電圧を有するのを可能にする。

(もっと読む)

増幅回路

【課題】簡易な構成で歪を抑制しつつ消費電流を低減する。

【解決手段】増幅回路100は、正入力端子T1と負入力端子T2とに供給される電圧の差分を増幅し差分電圧Vaを出力する差動増幅部10と、入力信号Vinの電圧を検出し検出電圧Vbを出力する入力電圧検出部20と、正電源電圧+Vccが供給される正電源端子T6と出力端子Toutとの間に設けられ、出力端子Toutから電流を吐き出すPMOS31と、負電源電圧−Vccが供給される負電源端子T7と出力端子Toutとの間に設けられ、出力端子Toutから電流を吸い込むNMOS32とを有する出力部30とを備える。

(もっと読む)

増幅回路

【課題】 動作が制限されることのない増幅回路を提供する。

【解決手段】 増幅回路1において、初段増幅回路10は、反転入力端子41に入力される入力信号61と、非反転入力端子42に入力される入力信号62とを増幅して初段増幅信号を出力する。第5トランジスタのコレクタ電流は、正電源の電位と第1コレクタ抵抗の抵抗値とに基づいて決定される。第6トランジスタのコレクタ電流は、負電源の電位と第2コレクタ抵抗の抵抗値とに基づいて決定される。このため、従来の差動増幅回路に比べて、第5トランジスタ及び第6トランジスタのコレクタ電流の上限値が大幅に緩和される。第5トランジスタ及び第6トランジスタのコレクタ電流が第1入力信号及び第2入力信号に応じて変化するときに、各コレクタ電流の波形が歪むことを防止できる。

(もっと読む)

差動増幅回路

【課題】差動増幅回路における入力オフセット電圧の上昇を抑制しつつ、同相入力電圧範囲を拡張する。

【解決手段】本発明による差動増幅回路は、ソース及びバックゲートが第1電流源205に共通接続された差動対トランジスタ201、202を備える差動入力段回路111と、差動入力段回路111の出力端子に接続される出力段回路121と、第1電流源205と出力段回路121の第2電流源206のそれぞれの電流I1、I2を、差動入力段回路111への入力電圧VIN1、VIN2に応じた大きさに調整する電流制御回路101とを具備する。

(もっと読む)

増幅回路

【課題】追加プロセスなしに、コモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる高耐圧の入力段とすることが可能な増幅回路を提供する。

【解決手段】増幅回路の入力段は、入力端子IN1,IN2が接続された第1の差動対トランジスタ10と、N1VDDに接続された第1の入力段電流バイアス手段20と、第1の差動対トランジスタ10と第1の入力段電流バイアス手段20に接続された第1の入力段カスコードトランジスタ群30と、第1の差動対トランジスタ10に接続された第2の入力段カスコードトランジスタ群40と、0VからN1VDDまで変化するコモンモード入力電圧が入力されたときに、第1の差動対トランジスタ10、第1の入力段カスコードトランジスタ群30、第2の入力段カスコードトランジスタ群40のVGSとVGDの絶対値がVDD以内となるバイアス電圧に調整する入力段バイアス調整回路60を備えている。

(もっと読む)

オペアンプ

【課題】低い電源電圧に対応する生産プロセスで生産された製品に対して高い電源電圧を供給した場合にも、ホットキャリアに起因するオペアンプ特性の劣化を回避することができるオペアンプを提供する。

【解決手段】バイアス電源回路が、2つのカレントミラー回路の間に挿入された一対の抵抗部を有して定電流バイアス電位の他に付加バイアス電位を生成し、差動増幅器が、差動入力トランジスタ対と能動負荷トランジスタ対との間に挿入され且つ当該付加バイアス電位によってバイアスされる電圧降下用トランジスタ対を含むオペアンプ。

(もっと読む)

差動増幅器

【課題】差動増幅回路、カレントミラー回路およびレール・トゥ・レール回路を組み合わせた電気回路において、外部からの信号に応じて容量の充放電を高速化する機能を維持しつつ、容量の充放電に寄与しない無駄な電流を減少させた差動増幅器を提供する。

【解決手段】外部からの信号に基づくデジタル信号を生成する論理回路を内蔵するスイッチ制御回路を設けて、容量の充放電を高速化するスイッチをこのデジタル信号を用いて制御する。

(もっと読む)

差動増幅回路及び集積回路装置

【課題】差動対を構成する2つのPMOSトランジスターにおけるNBTIの発生を可能な限り防ぐことにより出力オフセット電圧の発生を抑制可能な差動増幅回路及び集積回路装置を提供すること。

【解決手段】差動増幅回路1は、第1の信号が入力されるPMOSトランジスター10(第1のPMOSトランジスターの一例)と、第2の信号が入力されるPMOSトランジスター20(第2のPMOSトランジスターの一例)と、制御信号XSTBに基づいて、PMOSトランジスター10のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター14(第1のスイッチ部の一例)と、制御信号XSTBに基づいて、PMOSトランジスター20のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター24(第2のスイッチ部の一例)と、を含む。

(もっと読む)

無線周波デバイスのための差動シングルエンド変換

【課題】他の回路との磁気的結合による干渉を引き起こしにくい無線周波送信機回路のための差動シングルエンド変換回路を提供する。

【解決手段】異なる位相を有する複数の差動入力波形から無線周波波形を受信するための複数の入力361a、361bと、波形を複数の差動入力波形から非反転入力波形とほぼ同じ位相に反転させるためのインバータ回路366とを具備する回路が開示される。回路は、反転及び非反転入力波形を出力波形に組み合わせるためのコンバイナノード368をさらに具備する。

(もっと読む)

演算増幅回路、液晶パネル駆動装置

【課題】演算増幅回路を安定に動作させつつスルーレートを向上させる。

【解決手段】第1差動増幅部(311)は、P型差動対(P1/P2)のソースと正側電源電圧(VDD)との間に、並列に接続される第1電流源(I1)と第1容量(C1)とを備え、P型差動対(P1/P2)のソースと第1容量(C1)との間に挿入される第1スイッチ(SW1)をさらに備える。第2差動増幅部(312)は、N型差動対(N1/N2)のソースと負側電源電圧(VSS)との間に、並列に接続される第2電流源(I2)と第2容量(C2)とを備え、N型差動対(N1/N2)のソースと第2容量(C2)との間に挿入される第2スイッチ(SW2)をさらに備える。第1スイッチ(SW1)と第2スイッチ(SW2)とは、第1差動増幅部(311)および第2差動増幅部(312)に入力される入力差動信号に同期して交互に回路を開閉する。

(もっと読む)

電流源回路

【課題】回路面積が小さな電流源回路を提供する。

【解決手段】この電流源回路では、直流電圧V1に応じた値の参照電流I1を生成し、その電流I1のうちの電流IrをダイオードD1に流し、残りの電流I1−IrをダイオードD2に流し、ダイオードD1,D2のアノードの電圧VR1,VR2を差動増幅回路のトランジスタQ1,Q2のベースに与える。また、直流電圧V2に応じた値の参照電流I2を生成し、その電流I2を差動増幅回路の駆動電流とする。トランジスタQ1のコレクタに流れる定電流Io=Ir・(V2/V1)が電流源回路の出力電流Ioとなる。したがって、外付け用の端子および外部抵抗器が不要となる。

(もっと読む)

負荷効果低減回路

【課題】 増幅器の出力に負荷が接続された場合、その増幅器の出力段が持つ出力インピーダンスと接続した負荷によって、出力が理想値からずれる。本発明はこの負荷効果による出力のずれを自動的に補正する負荷効果低減回路を提供することを課題とする。

【解決手段】 増幅器の出力部と負荷との節点に設けられ、増幅器の入力電圧と出力電圧の差電圧に応じた電流を自動的に負荷に供給することを特徴とする負荷効果低減回路により解決される。上記回路は、増幅器の入力電圧及び上記節点の電圧を入力とする差動アンプと、該差動アンプの出力電圧と該節点の電圧とを加算する加算器と、該加算器の出力を入力とし該節点に電流として出力する電圧−電流変換回路とを含む。

(もっと読む)

多入力差動増幅器

【課題】各動作モードにおいてレベルシフト回路を用いることなく所望の入力電圧範囲となる多入力差動増幅器を提供する。

【解決手段】差動部1は、バイアス部2と出力部3との間に設けられ、第一入力部10と第二入力部20とを有する。第一入力部10は、ソースがバイアス部2と接続され、ドレインが出力部3と接続された1個のn型MOSFET(M11)からなる。第二入力部20は、直列接続される2個のn型MOSFET(M21)、(M22)と、直列接続される2個のn型MOSFET(M23)、(M24)とが2列に並列接続される。また、入力端INaはM11のゲートに接続され、入力端INxはM22とM23のゲートに接続され、入力端INyはM21とM24のゲートに接続される。バイアス部2は1つの定電流源21を有し、出力部3は2つのp型MOSFET(Q1、Q2)で構成のカレントミラー回路を有する。

(もっと読む)

差動増幅器及びデータドライバ

【課題】従来の差動増幅器は出力誤差が増大する問題がある。

【解決手段】本発明の差動増幅器は、内挿機能を有し、第1導電型トランジスタで形成される第1、第2の差動対(21、22)と、第2導電型トランジスタで形成される第3、第4の差動対(23、24)と、第1、第2の差動対に動作電流を供給する第1、第2の電流源(41、42)と、第3、第4の差動対に動作電流を供給する第3、第4の電流源(43、44)と、第1、第2の差動対にそれぞれ流れる電流量が第1、第2の電流源が出力する動作電流よりも小さくなる第1の動作範囲において、第1の差動対に供給される動作電流の変化点を制御する第1の制御回路51と、第3、第4の差動対にそれぞれ流れる電流量が第3、第4の電流源が出力する動作電流よりも小さくなる第2の動作範囲において、第4の差動対に供給される動作電流の変化点を制御する第2の制御回路52と、を有する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力期間の切替時における出力信号の遅延発生を抑制する出力回路、データドライバと表示装置の提供。

【解決手段】出力回路は差動増幅回路110、105,出力増幅回路120と第1の制御回路160、入力端子101、出力端子104、第1乃至第3の電源端子VDD、VSS、VMLを備える。差動増幅回路は前記入力端子の入力信号と前記出力端子の出力信号を入力する差動入力段110と第1及び第2のカレントミラー130、140を備える。出力増幅回路120は第1の電源端子VDDと出力端子104との間に接続された第1導電型の第1のトランジスタ121と出力端子104と第3の電源端子VMLとの間に接続された第2導電型の第2のトランジスタ122とを備える。第1の制御回路160は、第1導電型の第3のトランジスタ161と第1のスイッチ162を備える。

(もっと読む)

スイッチトキャパシタ積分および加算回路

【課題】単一の演算増幅器を使用して積分器と加算器の両方を実現するスイッチトキャパシタ回路を提供する。

【解決手段】1つの入力信号は、(1)1つまたは複数の積分ブランチと、(2)1つまたは複数の第1の加算ブランチとを介して演算増幅器の入力に送られる。第2の入力信号は、1つまたは複数の第2の加算ブランチを介して演算増幅器の入力に送られる。ブランチの各々は、キャパシタと、異なるクロック位相によって制御されるいくつかのスイッチとを含む。スイッチトキャパシタ回路はシングルエンドまたは差動とすることができる。

(もっと読む)

増幅回路

【課題】負帰還回路の構成によってゲインが変化することを防止できる増幅回路を提供する。

【解決手段】オペアンプ1において、初段増幅回路10は、反転入力端子41に入力される入力信号61と、非反転入力端子42に入力される入力信号62とを増幅して初段増幅信号を出力する。後段増幅回路20は、後段増幅信号を出力する。初段増幅回路10において、トランジスタTR1は、正成分61Aを入力とするエミッタフォロワ回路を形成する。トランジスタTR2は、負成分61Bを入力とするエミッタフォロワ回路を形成する。これにより、オペアンプ1における反転入力端子41側の入力インピーダンスを高くすることができる。トランジスタTR5は、正成分61A,62Aを増幅して初段増幅信号の正成分を出力する。トランジスタTR6は、負成分61B,62Bを増幅して初段増幅信号の負成分を出力する。

(もっと読む)

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子及びアノードに接続されている端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子及びアノードに接続されている逆相信号処理回路と、を備える。正相信号処理回路は、正相信号Vinpに応じて、駆動電流を増加するように制御し、逆相信号処理回路は、逆相信号Vinnに応じて、駆動電流を減少するように制御する。

(もっと読む)

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

カレントミラー回路

【課題】ゲートリーク電流による影響を軽減させることができ、なおかつ、高周波ノイズに対する耐性を向上させることができるカレントミラー回路を提供する。

【解決手段】カレントミラー回路は、ミラー元となる第1のMOSトランジスタと、ミラー先となる第2のMOSトランジスタのゲートと、第1のMOSトランジスタのゲートと第2のMOSトランジスタのゲートとの間に、この順序で直列に接続された第4、第2、第1および第3の抵抗と、第1の抵抗および第3の抵抗の間のノード、ならびに、第2の抵抗および第4の抵抗の間のノードを入力とし、第1および第2の抵抗の間のノードを出力とする差動増幅回路とを備える。第3の抵抗は第1の抵抗よりも大きい抵抗値に設定され、第4の抵抗は第2の抵抗よりも大きい抵抗値に設定され、第3の抵抗は第4の抵抗よりも大きい抵抗値に設定されている。

(もっと読む)

21 - 40 / 329

[ Back to top ]