Fターム[5J500DP01]の内容

Fターム[5J500DP01]に分類される特許

41 - 60 / 329

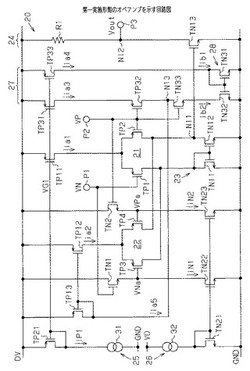

オペアンプ

【課題】出力電圧におけるひずみを低減すること。

【解決手段】制御回路27は、第1の差動対21と高電位電源VDとの間に接続されたトランジスタTP11に流れるバイアス電流ia1と等しい電流ia3を高電位電源VDとノードN13との間に生成する。また、制御回路27は、バイアス電圧VG1に応じた電流ib2をノードN13とグランドGNDとの間に生成する。ノードN13は、トランジスタTP13に接続され、電流源として動作するトランジスタTP12は、トランジスタTP13に流れる電流ia5と等しいバイアス電流ia2を第2の差動対22に供給する。そして、制御回路27は、入力電圧VPがゲートに供給されるトランジスタTN33により、ノードN13とグランドGNDとの間に流れる電流を制限する。

(もっと読む)

電流電圧変換回路および電流検出装置

【課題】入力電流を正確に検出する。

【解決手段】一対の外部入力端子2a,2bのうちの一方に第1電路11を介して一端が接続されると共に他端がグランド電位Gに接続された第1抵抗回路3と、他方の外部入力端子2bに第2電路12を介して一端が接続された第2抵抗回路4と、非反転入力端子が第1抵抗回路3の一端に直接接続され、かつ反転入力端子が第2抵抗回路4の一端に直接接続され、かつ出力端子が第2抵抗回路4の他端に接続された演算増幅器9とを備え、第1抵抗回路3および第2抵抗回路4の各抵抗値が共に値Rに規定され、演算増幅器9は、一対の外部入力端子2a,2b間に流れる電流値Iの入力電流Idを、グランド電位Gを基準として電圧値の絶対値が(2×R×I)となる出力電圧Voに変換して出力端子10a,10bから出力する。

(もっと読む)

差動増幅器及びその制御方法

【課題】オーバーシュートやアンダーシュートを低減し、安定した出力電圧を生成することが可能な差動増幅器を提供すること。

【解決手段】本発明にかかる差動増幅器は、入力信号Vinとフィードバック信号とに応じた1対の信号を出力する差動増幅段回路110と、1対の信号に基づいて出力電圧VOUTを生成する出力段回路120と、を備える。出力段回路120は、外部出力端子と高電位側電源端子との間に設けられ、1対の信号の一方に基づいて抵抗値が制御されるトランジスタ11と、外部出力端子と中間電源端子との間に設けられ、1対の信号の他方に基づいて抵抗値が制御されるトランジスタ12と、外部出力端子と2種類の電源電圧を排他的に切り替えて出力する切り替えスイッチSW3、SW4との間に設けられ、1対の信号の他方に基づいて抵抗値が制御されるトランジスタ15と、2種類の電源電圧として、中間電圧と接地電圧とを備える。

(もっと読む)

電荷検出回路

【課題】差動アンプの入力側のゲイン調整を容易に行うことができる電荷検出回路を提供する。

【解決手段】電荷発生型センサ及び容量変化型センサの何れかで構成される物理量検出センサ1A,1Bの一端が差動アンプ3の負極入力端子に接続され、他端が前記差動アンプ3の正極入力端子に接続され、前記差動アンプ3の出力端子と前記負極入力端子との間にフィードバック抵抗Rf及びフィードバック容量Cfが並列に接続され、且つ前記差動アンプの正極入力端子と基準電圧との間にキャンセル抵抗Rc及びキャンセル容量Ccが並列に接続された差動型の電荷検出回路であって、前記差動アンプの負極入力端子及び正極入力端子の少なくとも一方に逆バイアス電源7,9によって逆バイアス電位が与えられた可変容量ダイオードD1,D2を接続してゲイン調整を可能とした。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

差動増幅回路

【課題】電源電圧変動除去比を向上させつつ、回路内の消費電流の低減及び回路自体の小型化を図ることができる差動増幅回路を提供する。

【解決手段】電源電圧源に接続された電源ラインと、2つの差動入力素子からなる入力回路と、2つの差動入力素子にそれぞれが接続された2つのトランジスタからなる能動負荷とからなり、2つの差動入力素子のそれぞれに入力される入力信号に応じて差分信号を生成する入力部と、差分信号を増幅して出力電圧生成信号を生成する増幅部と、増幅部から供給される出力電圧生成信号と、電源電圧源から供給される電源電圧と、に基づいて出力電圧を生成する出力部と、2つのトランジスタのそれぞれの制御端と電源ラインとの間に接続され、電源電圧のノイズ成分のみを透過させるノイズ透過部と、を有することを特徴とする差動増幅回路。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし、差動段を単一導電型に簡素化した構成においても、充電及び放電における出力電圧波形の対称性を実現する。

【解決手段】第1の差動対111、112と、第1のカレントミラー130と、第2のカレントミラー140と、第1の浮遊電流源回路150と、第2の浮遊電流源回路160を備えた差動入力段と、第1導電型の第1のトランジスタ101と、第2導電型の第2のトランジスタ102と、を備えた出力増幅段110と、第1及び第2の電流源121、123と、第3のトランジスタ103と、第4のトランジスタ105と、第3及び第4の電流源122、124と、第5のトランジスタ104と、第6のトランジスタ106とを備えた電流制御回路120とを含む。

(もっと読む)

CMOSオペアンプ、センサ装置

【課題】信号の信号レベルを増幅するに際し、十分な利得を得ながら、サーマルノイズとフリッカノイズとの両者を同時に低減することができるCMOSオペアンプ、及びセンサ装置を提供することを目的とする。

【解決手段】第1MOSFETQ1及びQ2が配置されており、互いに信号レベルが異なる2種類の信号の入力を受け付ける信号入力部10と、第2MOSFETQ4〜Q11が配置されており、信号入力部10により受け付けられた2種類の信号の差分を増幅して出力する信号出力部11と、を備える。第1MOSFETQ1及びQ2のゲート酸化膜の厚さは、第2MOSFETQ4〜Q11のゲート酸化膜の厚さよりも小さく、第2MOSFETQ4〜Q11のゲート酸化膜の厚さは、基準厚さを超える厚さとされており、基準厚さは、第2MOSFETQ4〜Q11が予め設定された利得を得ることができる基準電圧値のゲート電圧に耐える厚さとされている。

(もっと読む)

差動増幅回路

【課題】高利得特性を有するとともに、小型でかつ安定な差動増幅動作を実現した差動増幅回路を得る。

【解決手段】1対のバイポーラトランジスタ1、2と、1対のバイポーラトランジスタ1、2の各々に対する出力バイアス印加回路および入力バイアス印加回路と、1対のバイポーラトランジスタ1、2の2つの出力端子の一方を接地するための終端抵抗15と、を備えている。1対のバイポーラトランジスタ1、2は、互いに異なるサイズからなり、2つの出力端子の他方は、振幅が大きい線路側に設けられている。

(もっと読む)

トランスミッタ、インタフェイス装置、車載通信システム

【課題】電源電圧の変動に起因する入力信号と出力信号のデューティばらつきを抑制する。

【解決手段】トランスミッタ10は、一端から充電電圧Vaが引き出されるコンデンサ105と、コンデンサ105の充電電流I1を生成する第1定電流源103と、コンデンサ103の放電電流I2を生成する第2定電流源104と、送信入力信号INの論理レベル、及び、充電電圧Vaと基準電圧Vrefとの比較結果に基づいて、コンデンサ105の充放電制御を行う充放電制御部(101、102、106)と、充電電圧Vaに応じてスルーレートが設定され、出力側電源電圧V2に応じて信号振幅が設定される送信出力信号OUTを生成する出力段(109〜116)と、出力側電源電圧V2に依存して基準電圧Vrefを変動させる基準電圧生成部107と、基準電圧Vrefに依存して充電電流I1及び放電電流I2の各電流値を変動させる定電流制御部108と、を有する。

(もっと読む)

フォールデッドカスコード型の差動アンプ及び半導体装置

【課題】回路を構成する素子数を削減すると共に、差動アンプのオフセットや抵抗の比精度による誤差を低減できるフォールデッドカスコード型の差動アンプ及び半導体装置を提供する。

【解決手段】フォールデッドカスコード型の差動アンプ14の入力段30をHVMOSにより構成し、出力段32をLVMOS20により構成することにより、従来では、2つの差動アンプにより構成していた差動増幅アンプを1つの差動アンプ14により構成することができる。

(もっと読む)

差動増幅回路

【課題】オフセット電圧が入力電圧に依存しない差動増幅回路を提供する。

【解決手段】1対のPMOSトランジスタ及び第一電流源からなる第一入力段と、1対のNMOSトランジスタ及び第二電流源からなる第二入力段に加え、第一補正電流発生回路及び第二補正電流発生回路を設け、折り返しカスコード増幅段に流れる電流と同じ電流を出力段に流す構成としたので、折り返しカスコード増幅段と出力段のトランジスタのバイアス条件が同じになるようにした。

(もっと読む)

デューティ比自動調整コンパレータ回路

【課題】電源電圧などの回路の動作条件の変動に関わらず、デューティ比の変動を抑圧、低減する。

【解決手段】差動増幅回路1と、この差動増幅回路1において差動対を構成する2つのMOSトランジスタ21,22のソース同士の接続点における電位に基づいて閾値電圧を生成する閾値電圧生成回路2と、インバータ動作における閾値電圧を、閾値電圧生成回路2により生成された閾値電圧に設定可能に構成された閾値電圧可変インバータ回路3とが設けられることにより、インバータ動作における閾値電圧が、差動増幅回路1の出力振幅の中心電圧に設定でき、電源電圧の変動などが生じてもインバータの入出力間におけるデューティ比の変動が抑圧、低減できるものとなっている。

(もっと読む)

比較回路

【課題】消費電流および回路規模をほとんど増大させることなく、容易に容量の充電時間を短くすることの出来る比較回路を提供する。

【解決手段】差動増幅回路10の出力が入力される単相増幅回路20の出力をNチャネルMOSトランジスタMN5からなるソースフォロワによるクランプ回路41に入力し、当該クランプ回路41により単相増幅回路20の入力を制限することにより、新たに定電圧源を設けることなく必要な充電電圧幅を狭めて容量Cpの充電時間を短くすることができる。また、単相増幅回路10の出力に応じて単相増幅回路10の入力を制限するので、単相増幅回路10の閾値電圧のばらつきや電源電圧の影響が問題にならない。

(もっと読む)

再帰型フィルタ回路

【課題】再帰フィルタ回路のエミッタフォロア回路の数を低減し、回路規模が小さい再帰型フィルタ回路を提供する。

【解決手段】バイポーラトランジスタ(Tr)101を流れる電流Iinとフィードバック電流Ifbとを加算して電流Iを生成するノードB、電流Iをテール電流とし、ゲインを変更する制御信号が入力されるバイポーラTr106及びバイポーラTr103を含む差動対100、バイポーラTr106に流れる電流を電圧に変換する抵抗素子105を含む可変ゲイン増幅部、変換後の電圧を増幅して出力信号を生成するバイポーラTr113を含む出力部115、可変容量素子104を含むハイパス部、ハイパス部から出力された信号をバッファリングする回路114、バッファリングされた信号を、可変容量素子109を介して周波数帯域制限するローパス部を含む移相部によって再帰型フィルタを構成する。

(もっと読む)

増幅回路、信号処理回路および半導体集積回路装置

【課題】回路面積を増大させることなく、シングルエンド出力構成と差動出力構成とを切り替える機能を有する増幅回路を提供する。

【解決手段】スイッチS1、S4がオフされ、スイッチS2がオンされると、負荷回路11が差動対7の能動負荷として機能するとともに出力端子12が内部で切り離される。これにより、増幅回路1は、入力端子8、9に入力された入力電圧Vinp、Vinmを差動増幅し、不平衡信号Voを出力端子13から出力するシングルエンド出力構成となる。スイッチS1、S4がオンされ、スイッチS2がオフされると、負荷回路11が差動対7の負荷として機能するとともに出力端子12が内部で接続される。これにより、増幅回路1は、入力端子8、9に入力された入力電圧Vinp、Vinmを差動増幅し、平衡信号Vom、Vopを出力端子12、13から出力する差動出力構成となる。

(もっと読む)

表示装置、差動増幅回路、表示装置のデータ線駆動方法

【課題】パネルが大型化し、また、垂直同期周波数が高くなったとしても、画質の劣化を防止することが可能な表示装置を実現する。

【解決手段】表示装置の備える差動増幅器は、正電源と負電源との間に直列に接続された第1、第2トランジスタと、その各々のドレインを共通に接続された出力端子と、第1カレントミラー回路と出力端子との間に設けられた第1位相補償容量と、第2カレントミラー回路と出力端子との間に設けられた第2位相補償容量とを備える出力段回路と、加算回路と出力段回路との間に設けられて第1、第2トランジスタのバイアス制御を行うバイアス制御回路とを具備する。出力回路は、切り替え期間に第1、第2トランジスタの各々のゲートとソース間を短絡すると共に、第1位相補償容量及び前記第2位相補償容量を所定の電位へ充放電する。バイアス制御回路は、第1、第2トランジスタのゲート間の電流経路を遮断する。

(もっと読む)

増幅器および半導体記憶装置

【課題】容量素子の値をより小さくして、チップサイズの増大を抑制する。

【解決手段】差動対(NMOSトランジスタMN1、MN2)で構成される入力段回路と、差動対のそれぞれ負荷となる2つのカレントミラー回路(PMOSトランジスタMP1、MP2とPMOSトランジスタMP3、MP4)と、少なくとも一方のカレントミラー回路で駆動されるソース接地の出力トランジスタ(NMOSトランジスタMN5a)と、出力トランジスタのドレイン・ゲート間に接続され、抵抗素子(R1)と容量素子(C1)との直列接続からなる位相補償回路と、を備え、出力トランジスタ(NMOSトランジスタMN5a)は、入力段回路およびカレントミラー回路を構成するトランジスタよりもサイズが大きい。

(もっと読む)

差動増幅器、及びソースドライバ

【課題】入出力間オフセットの電源電圧付近におけるリニアリティを改善することが可能な差動増幅器、及びソースドライバを提供すること。

【解決手段】本発明にかかる差動増幅器100は、入力対の一方が第1入力端子IN1をなす第1差動対111と、第1差動対111と並列に接続され、入力対の一方が第2入力端子IN2をなす、第1差動対111と同じ導電型の第2差動対112と、第1入力端子IN1に入力される第1入力電圧Vin1が第1差動対111の動作しきい値以上、かつ第2入力端子IN2に入力される第2入力電圧Vin2が第2差動対112の動作しきい値未満のときに、動作している第1差動対111の能力を低減する第1能力低減回路と、を備えるものである。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

41 - 60 / 329

[ Back to top ]