国際特許分類[H04L25/02]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | デジタル情報の伝送,例.電信通信 (61,356) | ベースバンド方式 (1,966) | 細部 (1,421)

国際特許分類[H04L25/02]の下位に属する分類

送信機または受信機における整形回路網,例.整形回路網を付加するもの (399)

伝送レートを変えるための,伝送前または再送前の電気的又は時期的な信号蓄積

直流レベル再生手段;バイアスひずみ補正 (19)

混信を低減するための変形;線路障害による影響を低減するための変形 (56)

線路平衡の変動の補正 (1)

線路インピーダンスの変動の補正 (2)

チャネル分割配置

補間装置

電信信号を誘導的に発生させるための配置

中継器回路;リレー回路

国際特許分類[H04L25/02]に分類される特許

51 - 60 / 944

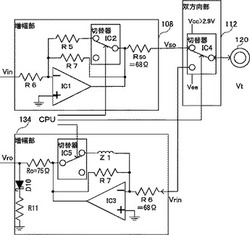

映像信号多重伝送装置およびそれを具備する撮像装置

【課題】映像信号多重デジタル伝送システムのケーブル長が延びたときの伝送波形を改善する。

【解決手段】一つの75Ω伝送路にデジタル映像信号を時分割双方向切換送受する多重伝送装置において、伝送路両側の終端に時分割で双方向を切換えるNMOSバススイッチICを有し、受信側に波形等化器または波形等化器を含む受信器を有し、NMOSバススイッチICの正電源Vccを+3.3Vとし負電源Veeを−1.7Vとし、NMOSバススイッチICの導通抵抗の平均値7Ω分差し引いた75−7=68Ωを終端抵抗値Rzとする。さらに、アナログ切換器の導通抵抗が低い信号波形極性を圧縮する接地されたショトキーバリアダイオードと抵抗の直列接続を有する。

(もっと読む)

信号配線システム及びジッタ抑制回路

【課題】従来は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することが難しかった。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

(もっと読む)

差動信号伝送回路、ディスクアレイコントローラ及び差動信号伝送ケーブル

【課題】差動信号伝送路の障害を作業者が容易に確認することができる差動信号伝送回路、ディスクアレイコントローラ及び差動信号伝送ケーブルを提供する。

【解決手段】差動信号伝送回路は、正負の伝送路間に設けたインダクタンスと、伝送路に直流電圧を引加する直流電圧部と、伝送路に引加された直流電圧の大きさを監視する監視部と、監視部が監視する直流電圧の大きさに基づいて前記伝送路の障害を検出し、障害を検出した場合当該旨を出力する制御部と、を有する。

(もっと読む)

リング型ネットワークシステム

【課題】電気的には接続されていながら正常に通信ができないような論理的な断線状態が発生した場合であってもループバックを行なうことを可能にし、通信を継続することができるようにする。

【解決手段】マスタ局1は、送信が連続して失敗したことを検知したときに断線検出フレームを生成して隣接するスレーブ局#1(2)、#4(5)に送信する。スレーブ局#4(5)では、断線検出フレームを受信したときに応答し、自局が末端局でない場合に、送信元局以外の隣接局#3(4)に対して断線検出フレームを送信する。そして、スレーブ局#4(5)では、断線検出フレームを送信してから所定時間経過しても隣接局#3(4)からその応答を受信できない場合に、自局を末端局としてループバックを行う。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

バイポーラ/ユニポーラ変換回路

【課題】入力信号の振幅レベルが変化した場合でも、最適なバイアス値を設定する。

【解決手段】バイポーラ/ユニポーラ変換回路1は、入力信号Iと正極バイアス値V(+)及び負極バイアス値V(−)とを比較し、比較の結果に基づき入力信号をRZ信号に各々変換するRZ変換回路2及び3と、各々のRZ信号の論理和を演算する論理和回路4と、論理和回路4から出力された両極RZ信号AをNRZ信号に変換するNRZ変換回路7と、両極RZ信号に基づき、入力信号の入力状態を検出する入力断検出回路10と、入力断検出回路10の検出結果に基づき、正極及び負極バイアス値を設定するバイアス設定回路12と、各々のRZ信号が所定の符号化規則に従っているか否かを検出する符号則誤り検出回路11とを備え、バイアス設定回路12は、各々のRZ信号が符号化規則に従っていないことが検出された場合に、正極及び負極バイアス値を設定する。

(もっと読む)

送信ドライバ回路

【課題】信号の伝送速度が速い差動通信においても、コモンモード電圧の発生を適切に抑制できる送信ドライバ回路を提供する。

【解決手段】レベルホールド回路3は、通信信号出力部2が差動信号の電圧レベルを変化させる際に伝送線路5に発生するコモンモード電圧の変化を検出し、その検出レベルをレベルホールドする。そして、信号処理回路4は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整する。

(もっと読む)

電子回路

【課題】簡易な構成でありながら正確に同期したクロックを各基板に分配することができる電子回路を提供すること。

【解決手段】第1コイルL1と第1キャパシタC1による第1共振回路を含む第1発振器21を有する第1基板11と、第2コイルL2と第2キャパシタC2による第2共振回路を含む第2発振器22を有する第2基板12とを備え、前記第1コイルL1と第2コイルL2が誘導結合して前記第1発振器21と第2発振器22が結合共振することを特徴とする電子回路。

(もっと読む)

差動信号伝送回路

【課題】スキューを低コストで低減した差動信号伝送回路を提供する。

【解決手段】差動信号伝送回路1は、第1の接続部6Aおよび第2の接続部6Bを有し、差動信号を送信する送信回路5と、第3の接続部9Aおよび第4の接続部9Bを有し、差動信号を受信する受信回路8と、一端が第1の接続部に接続され、差動信号の対をなす一方の信号を伝播する第1の信号線路11Aと、一端が第2の接続部に接続され、差動信号の対をなす他方の信号を伝播するとともに第1の信号線路より電気長が長い第2の信号線路11Bと、第1の信号線路の他端と第3の接続部とに接続された受信側調節配線10Aと、を備え、第1の接続部から第1の信号線路および受信側調節配線を介して第3の接続部までの電気長と、第2の接続部から第2の信号線路を介して第4の接続部までの電気長との差に対応するスキューが、許容される最大スキュー以下となるように調節されている。

(もっと読む)

伝送装置及びネットワークシステム

【課題】TDMデータをパケット化し伝送するネットワークシステムにおいて、パケットネットワーク上で発生する遅延変動を吸収するために、伝送装置内に具備した遅延変動吸収バッファにユーザデータを格納している時間を最適化し、エンド・ツー・エンドでの遅延時間によるリソースの過剰消費を抑止する。

【解決手段】伝送装置1は、TDMネットワーク7から受信したTDMフレームをパケット化してパケットネットワーク8へ送信し、また、パケットネットワーク8から受信したパケット信号をTDM化して前記TDMネットワークへ送信するものであり、パケットネットワーク上の伝送遅延時間を測定する手段106〜108、113と、測定した遅延時間から遅延変動時間を算出する手段109と、算出した遅延変動時間に基づいて、パケットネットワーク8から受信した信号をTDM化してTDMネットワークに送信するまでの時間を制御する手段112とを備える。

(もっと読む)

51 - 60 / 944

[ Back to top ]